# **VAXstation II**

Technical Manual, BA123 Enclosure

# VAXstation II Technical Manual, BA123 Enclosure

Prepared by Educational Services of Digital Equipment Corporation

## © Digital Equipment Corporation 1986. All Rights Reserved.

The material in this manual is for informational purposes only and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

FCC Notice: This equipment generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such a commercial environment. Operation of this equipment in a residential area may cause interference in which case, the user, at his own expense, may be required to take measures to correct the interference.

#### Printed in U.S.A.

The manuscript for this book was created on a VAX-11/780 system and, via a translation program, was automatically typeset by Digital's DECset Integrated Publishing System. The book was produced by Educational Services Development and Publishing in Marlboro, MA.

The following are trademarks of Digital Equipment Corporation:

| digital <sup>™</sup> | MicroPDP-11  | RSX            |

|----------------------|--------------|----------------|

| DEC                  | MicroVAX     | RT             |

| DECmailer            | MicroVMS     | UNIBUS         |

| DECmate              | PDP          | VAX            |

| DECservice           | P/OS         | VAXELN         |

| DECUS                | Professional | VAXstation     |

| DECwriter            | Q-Bus        | VMS            |

| DIBOL                | Rainbow      | VT             |

| MASSBUS              | RSTS         | Work Processor |

# **Contents**

| Preface   |                                                       |

|-----------|-------------------------------------------------------|

|           | INTRODUCTION xi CONVENTIONS USED IN THIS DOCUMENT xii |

| Chapter 1 | System Introduction                                   |

| 1.1       | INTRODUCTION                                          |

| 1.2       | SYSTEM COMPONENTS1-1                                  |

| 1.3       | SYSTEM ENCLOSURE                                      |

| 1.3.1     | BA123-A Frame                                         |

| 1.3.1.1   | Air Circulation                                       |

| 1.3.1.2   | Temperature Sensor Printed Circuit Board1-6           |

| 1.3.2     | Control Panel                                         |

| 1.3.2.1   | CPU Console Board1-8                                  |

| 1.3.3     | Mass Storage Area1-10                                 |

| 1.3.3.1   | Signal Distribution Board1-11                         |

| 1.3.4     | Backplane Assembly1-12                                |

| 1.3.5     | Power Supply                                          |

| 1.3.5.1   | Electrical Distribution1-18                           |

| 1.3.6     | I/O Distribution Panel1-19                            |

| 1.4       | GRAPHICS SUBSYSTEM1-22                                |

| 1.4.1     | VR260 Monitor                                         |

| 1.4.2     | LK201 Keyboard1-23                                    |

| 1.4.3     | VS10X Mouse                                           |

| Chapter 2 | System Description                         |

|-----------|--------------------------------------------|

| 2.1       | MicroVAX II PROCESSOR                      |

| 2.1.1     | KA630-A CPU2-1                             |

| 2.1.1.1   | Console Program2-3                         |

| 2.1.1.2   | Primary Bootstrap Program (VMB)            |

| 2.1.2     | CPU Patch Panel Insert                     |

| 2.1.3     | MS360 Memory Module 2-8                    |

| 2.2       | GRAPHICS SUBSYSTEM                         |

| 2.2.1     | VCB01 Video Controller Module              |

| 2.2.1.1   | Memory Starting Address (MSA)              |

| 2.2.1.2   | CSR Base Address                           |

| 2.2.1.3   | Display Density2-11                        |

| 2.2.2     | VR260 Monitor                              |

| 2.2.3     | LK201 Keyboard                             |

| 2.2.4     | VS10X Mouse                                |

| 2.3       | MASS STORAGE SUBSYSTEM                     |

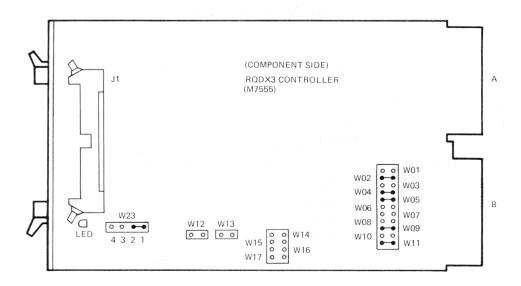

| 2.3.1     | RQDX3 Disk Controller                      |

| 2.3.1.1   | Memory Starting Address (MSA)              |

| 2.3.1.2   | Logical Unit Number                        |

| 2.3.2     | RD52 and RD53 Fixed Disk Drives            |

| 2.3.2.1   | RD52 Configuration                         |

| 2.3.2.2   | RD53 Configuration                         |

| 2.3.3     | RX50 Diskette Drive                        |

| 2.3.4     | TK50 Tape Drive Subsystem2-17              |

| 2.3.4.1   | M7546 Controller Module CSR Address and    |

|           | Interrupt Vector                           |

| 2.3.4.2   | M7546 Controller Module Revision Level and |

|           | Unit Number                                |

| Chapter 3 | Options                                    |

|           | - Process                                  |

| 3.1       | GENERAL                                    |

| 3.1.1     | Ordering Options                           |

| 3.1.2     | Module Configuration                       |

| 3.2       | DEQNA ETHERNET CONTROLLER                  |

| 3.2.1     | CSR Address and Interrupt Vector           |

| 3.3       | DZQ11 ASYNCHRONOUS MULTIPLEXER             |

| 3.3.1     | CSR Address and Interrupt Vector           |

| 3.4       | GRAPHICS TABLET                            |

| 3.4.1     | Baud Rate Selection                        |

| 3.4.2     | Graphics Tablet Connector Pin Assignments  |

| Chapter 4    | Configuration                                             |

|--------------|-----------------------------------------------------------|

| 4.1<br>4.1.1 | CONFIGURATION RULES 4-1 Physical Priority 4-1             |

| 4.1.2        | Expansion Space                                           |

| 4.1.3        | Power Requirements                                        |

| 4.1.4        | Bus Loads                                                 |

| 4.1.5        | CSR Addresses and Interrupt Vectors                       |

| 4.2          | FLOATING CSR ADDRESSES 4-10                               |

| 4.3          | CONFIGURATION EXAMPLES                                    |

| 4.3.1        | Module Utilizations                                       |

| Chapter 5    | Diagnostics                                               |

| 5.1          | KA630 SELF-TESTS 5-1                                      |

| 5.1.1        | Power-up Mode                                             |

| 5.1.2        | Console Mode                                              |

| 5.1.2.1      | Console Terminal Error Messages                           |

| 5.2          | DEVICE SELF-TESTS                                         |

| 5.2.1        | DEQNA Ethernet Controller Module                          |

| 5.2.2        | RQDX3 Mass Storage Controller Module                      |

| 5.2.3<br>5.3 | TQK50 Tape Controller Module                              |

| 5.3.1        | Configuration Verification                                |

| 5.3.2        | System Tests                                              |

| 5.4          | TROUBLESHOOTING 5-11                                      |

| 5.4.1        | Unknown System-Level Problems                             |

| 5.4.2        | Device-Specific Problems                                  |

| 5.4.3        | VR260 Monitor Troubleshooting Problems 5-15               |

| Chapter 6    | FRU Removal and Replacement                               |

| 6.1          | EXTERIOR PANEL REMOVAL                                    |

| 6.1.1        | Right Side Panel Removal                                  |

| 6.1.2        | Left Side Panel Removal                                   |

| 6.2          | ON/OFF SWITCH REMOVAL                                     |

| 6.3          | CPU CONSOLE BOARD REMOVAL                                 |

| 6.4          | 5-1/4 INCH (13.3 cm) MASS-STORAGE DEVICE                  |

| 6.4.1        | REMOVAL 6-10 RD52 Main Printed Circuit Board Removal 6-10 |

| 6.4.2        | RD52 Main Printed Circuit Board Removal                   |

| U. Ishi      | TUDO DISK DITTO INCUIDING DOMA REINOTAL                   |

| 6.5        | EAN DEMOVAL                             |

|------------|-----------------------------------------|

| 6.5.1      | FAN REMOVAL                             |

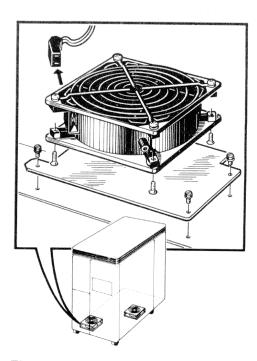

| 6.5.2      | Mass Storage Fan Removal                |

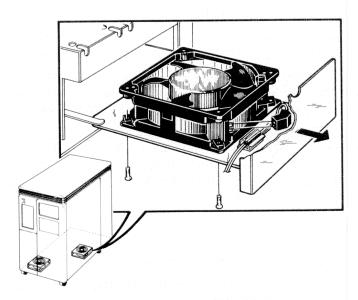

| 6.6        | Card Cage Fan Removal                   |

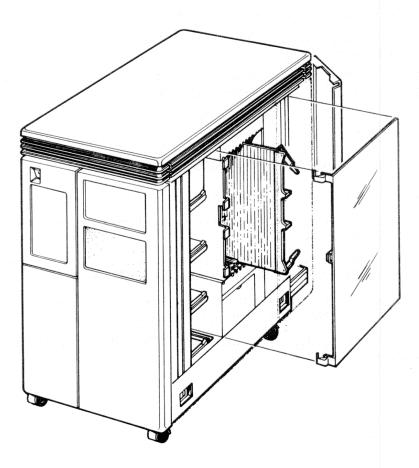

| 6.6.1      | MODULES                                 |

| 6.6.2      | Removal 6-18                            |

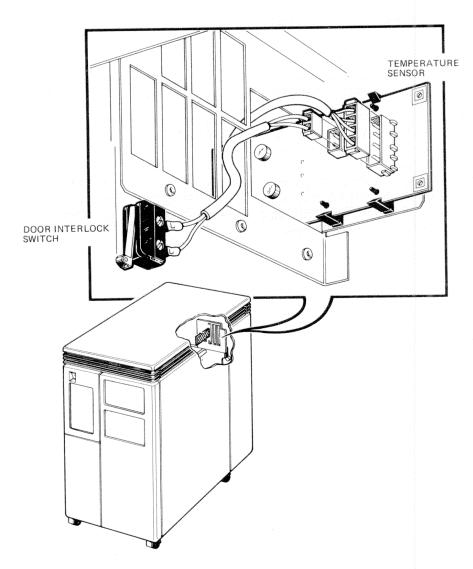

| 6.7        | DOOR INTERLOCK SWITCH REMOVAL 6-20      |

| 6.8        | TEMPERATURE SENSOR REMOVAL 6-20         |

| 6.9        | POWER SUPPLY REMOVAL 6-22               |

| 6.10       | BACKPLANE                               |

| 6.10.1     | Removal 6-24                            |

| 6.10.2     | Replacement                             |

| 6.11       | FILTER CONNECTOR REMOVAL 6-25           |

| 6.12       | MONITOR                                 |

| 6.12.1     | Cover and Rear Bezel6-26                |

| 6.12.1.1   | Removal                                 |

| 6.12.1.2   | Replacement                             |

| 6.12.2     | Deflection Board 6-27                   |

| 6.12.2.1   | Removal                                 |

| 6.12.2.2   | Replacement                             |

| 6.12.3     | CRT Assembly                            |

| 6.12.3.1   | Removal                                 |

| 6.12.3.2   | Replacement                             |

| 6.12.4     | Power LED                               |

| 6.12.4.1   | Removal                                 |

| 6.12.4.2   | Replacement                             |

| 6.12.5     | Monitor Alignment                       |

| Appendix A | Console Commands                        |

| Appendix B | Console Error Messages and Explanations |

| Appendix C | VCB01 Video Controller Module           |

| Index      |                                         |

# Figures

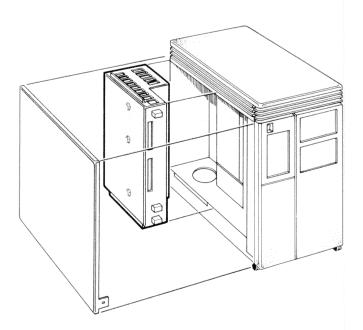

| 1-1  | VAXstation II System Components                                | <br>1-3  |

|------|----------------------------------------------------------------|----------|

| 1-2  | BA123 Enclosure                                                |          |

| 1-3  | BA123 Removable Panels and Doors                               | <br>1-5  |

| 1-4  | Airflow                                                        | <br>1-6  |

| 1-5  | Temperature Sensors                                            | <br>1-7  |

| 1-6  | BA123 Front Control Panel Cutouts                              | <br>1-7  |

| 1-7  | CPU Console Board                                              | <br>1-8  |

| 1-8  | Mass Storage Shelves                                           | <br>1-10 |

| 1-9  | Signal Distribution Board                                      | <br>1-11 |

| 1-10 | Signal Distribution Board Cabling                              |          |

| 1-11 | Backplane Grant Circuitry                                      |          |

| 1-12 | Backplane Connectors                                           |          |

| 1-13 | Power Supply                                                   |          |

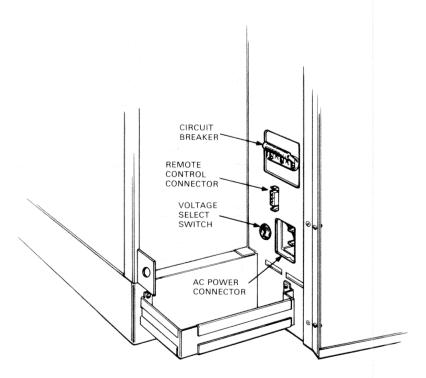

| 1-14 | Circuit Breaker, Voltage Select Switch, Connectors (Rear View) | <br>1-17 |

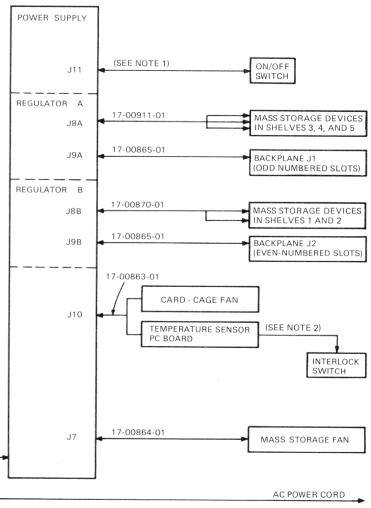

| 1-15 | Electrical Distribution                                        |          |

| 1-16 | Rear Door                                                      | <br>1-19 |

| 1-17 | Rear I/O Distribution Board                                    | <br>1-20 |

| 1-18 | I/O Insert Panels and Adapter Plate                            | <br>1-21 |

| 1-19 | VR260 Monitor                                                  |          |

| 1-20 | LK201 Keyboard                                                 |          |

| 1-21 | VS10X Mouse Device                                             | <br>1-25 |

| 2-1  | KA630-A CPU Module                                             | <br>2-3  |

| 2-2  | CPU Patch Panel Insert                                         | <br>2-6  |

| 2-3  | VCB01 Video Controller Module                                  | <br>2-9  |

| 2-4  | RQDX3 Controller Module                                        | <br>2-13 |

| 2-5  | RD52 Fixed Disk Drive                                          |          |

| 2-6  | RX50 Diskette Drive                                            | <br>2-17 |

| 2-7  | TK50 Tape Drive Subsystem                                      |          |

| 2-8  | M7546 Controller Module                                        |          |

| 3-1  | DEQNA Ethernet Controller Module                               | <br>3-3  |

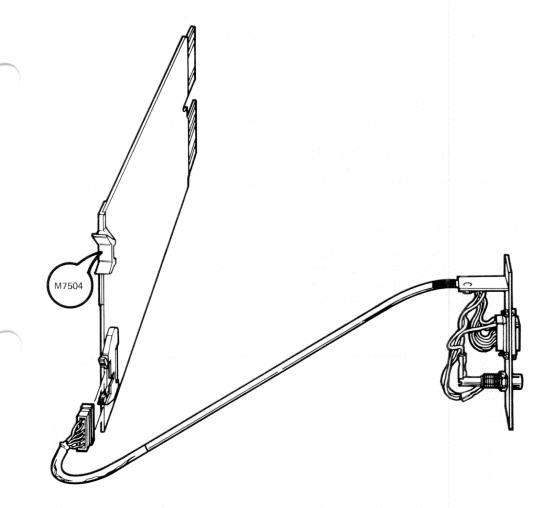

| 3-2  | DEQNA Module Internal Cabling                                  | <br>3-5  |

| 3-3  | DZQ11 Module                                                   |          |

| 3-4  | DZQ11 Module Internal Cabling                                  | <br>3-8  |

| 3-5  | Graphics Tablet Components                                     | <br>3-9  |

| 3-6  | Graphics Tablet Connector Pins                                 | <br>3-10 |

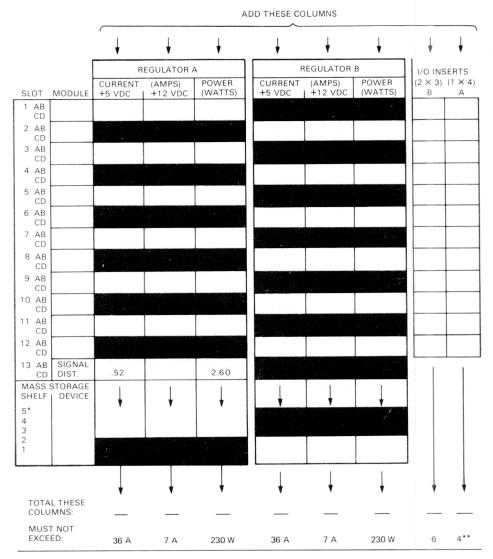

| 4-1  | Configuration Worksheet                                        | <br>4-3  |

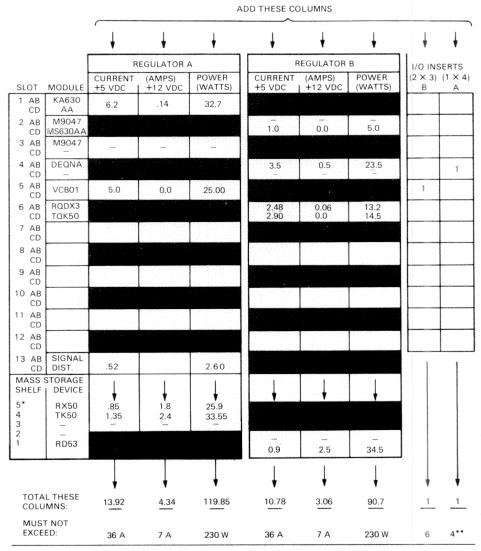

| 4-2  | Base System                                                    |          |

| 4-3  | Completed Configuration Worksheet                              |          |

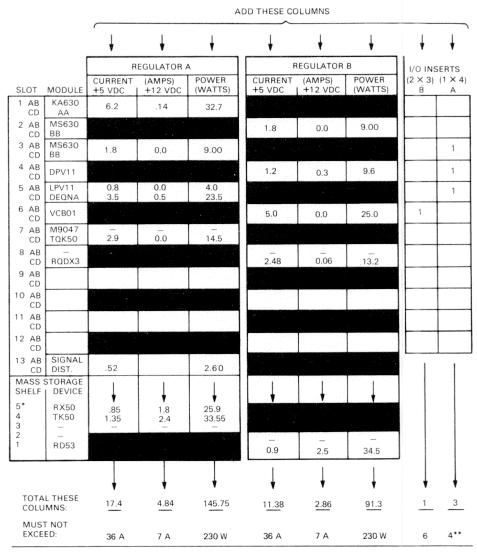

| 4-4  | Advanced System                                                | <br>4-12 |

# Contents

| 4-5  | Completed Configuration Worksheet (Advanced System) | . 4-13 |

|------|-----------------------------------------------------|--------|

| 5-1  | CPU Module LEDs                                     | . 5-1  |

| 5-2  | DEQNA Module LEDs                                   | . 5-7  |

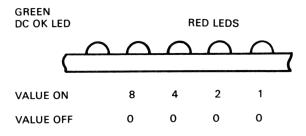

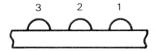

| 5-3  | RQDX3 Module LEDs                                   |        |

| 5-4  | TQK50 Module LEDs                                   |        |

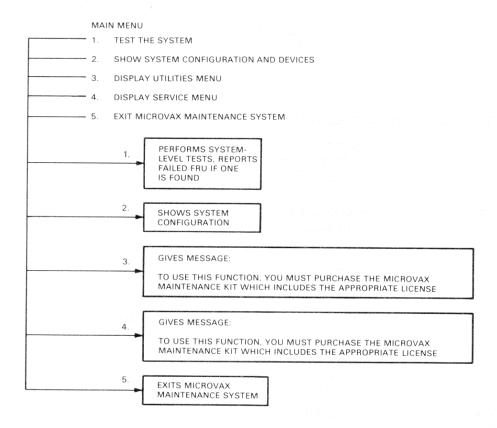

| 5-5  | MicroVAX Maintenance System Menu Tree               | . 5-10 |

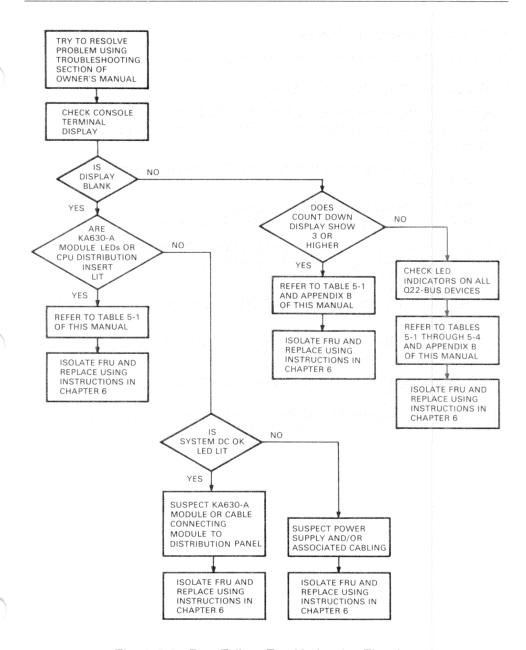

| 5-6  | Boot Failure Troubleshooting Flowchart              |        |

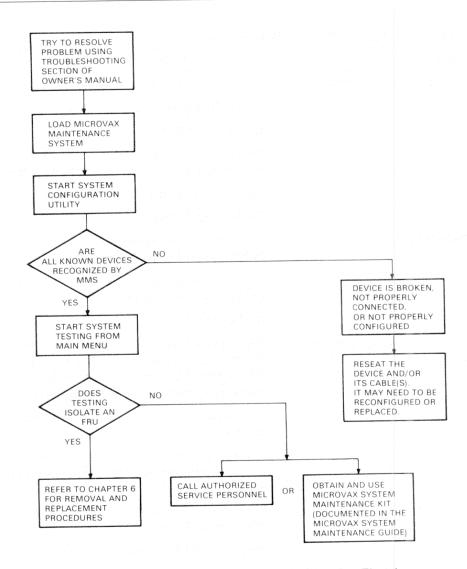

| 5-7  | Device-Specific Failure Troubleshooting Flowchart   | . 5-15 |

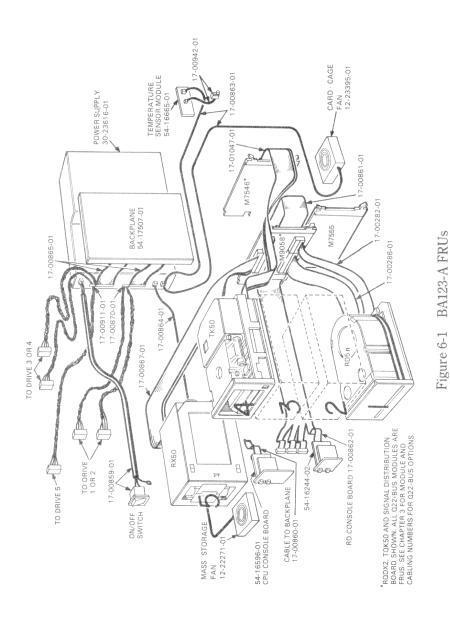

| 6-1  | BA123-A FRUs                                        |        |

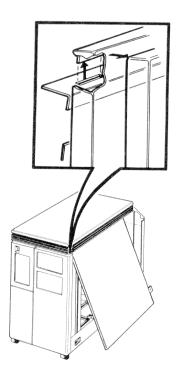

| 6-2  | Unhooking the Right Side Panel                      | . 6-4  |

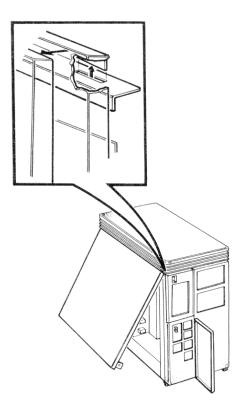

| 6-3  | Right Side Panel Removal                            | . 6-5  |

| 6-4  | Unhooking the Left Side Panel                       | . 6-6  |

| 6-5  | Left Side Panel Removal                             |        |

| 6-6  | ON/OFF Switch Removal                               | . 6-8  |

| 6-7  | CPU Console Board Removal                           | . 6-9  |

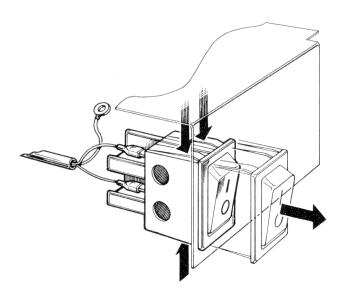

| 6-8  | Slide Plate Removal                                 | . 6-11 |

| 6-9  | Removing the 2-pin Connector and Screws             | . 6-11 |

| 6-10 | Front Bezel Removal                                 |        |

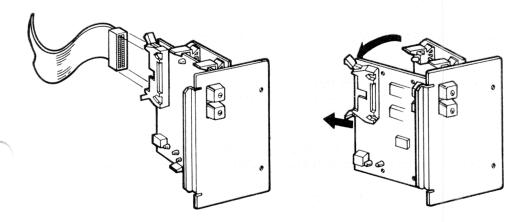

| 6-11 | Removing the Phillips Screws from Heatsink          | . 6-13 |

| 6-12 | MPCB Removal                                        | . 6-13 |

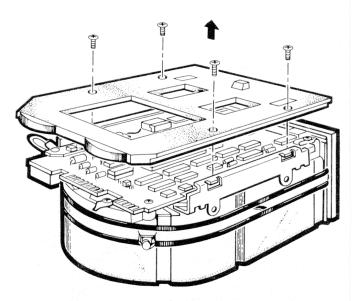

| 6-13 | RD53 Device Electronics Board Removal               | . 6-15 |

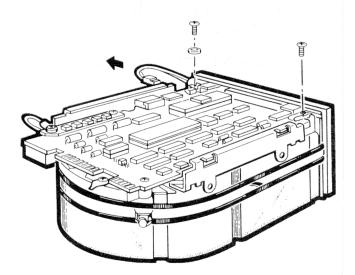

| 6-14 | Mass Storage Fan Removal                            | . 6-16 |

| 6-15 | Card Cage Fan Removal                               |        |

| 6-16 | Module Removal                                      |        |

| 6-17 | Temperature Sensor/Door Interlock Switch            | . 6-21 |

| 6-18 | Power Supply Removal                                |        |

| 6-19 | Backplane Removal                                   | 6-24   |

| 6-20 | Deflection Board and Chassis Door Location          | . 6-27 |

| 6-21 | Power LED Removal/Replacement                       | . 6-29 |

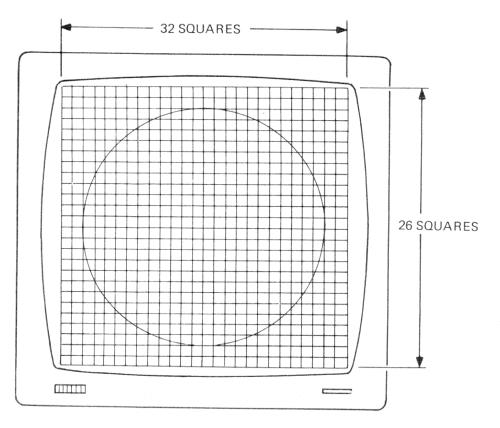

| 6-22 | Monitor Alignment Patterns                          | 6-30   |

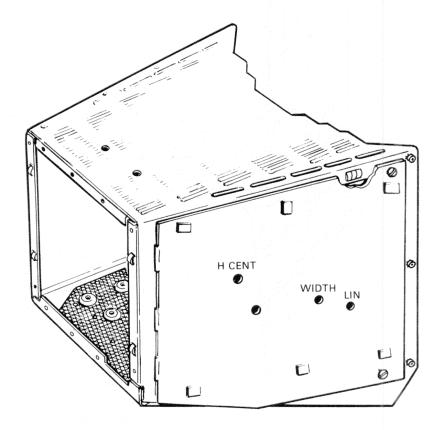

| 6-23 | VR260 Monitor Adjustments, H CENT, WIDTH, and LIN   | . 6-31 |

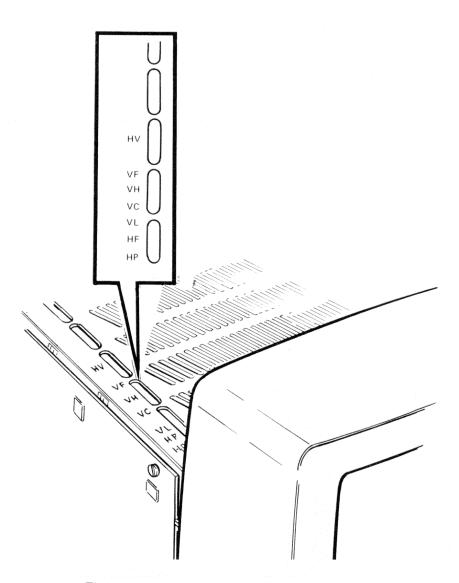

| 6-24 | VR260 Monitor Adjustments (Top)                     |        |

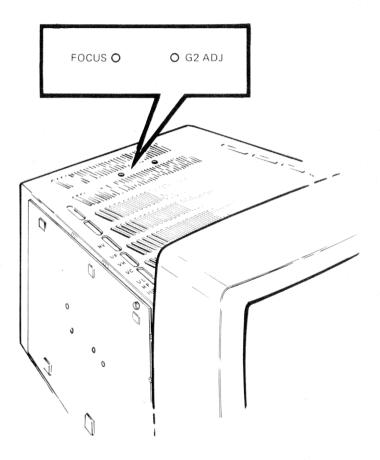

| 6-25 | VR260 Monitor Adjustments, Focus and G2             | . 6-33 |

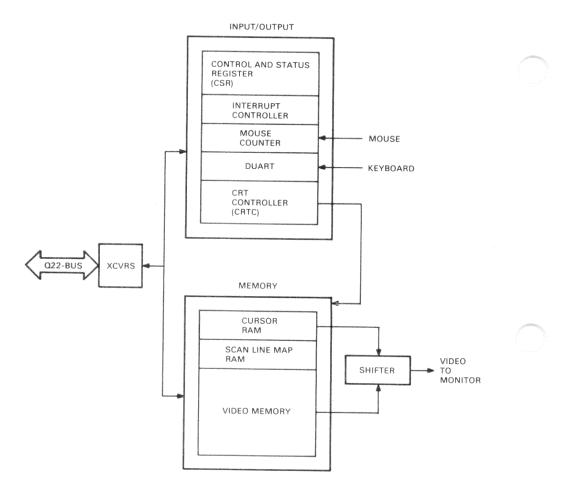

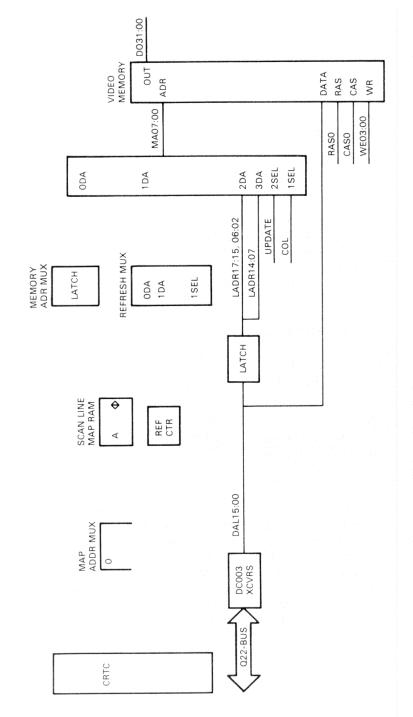

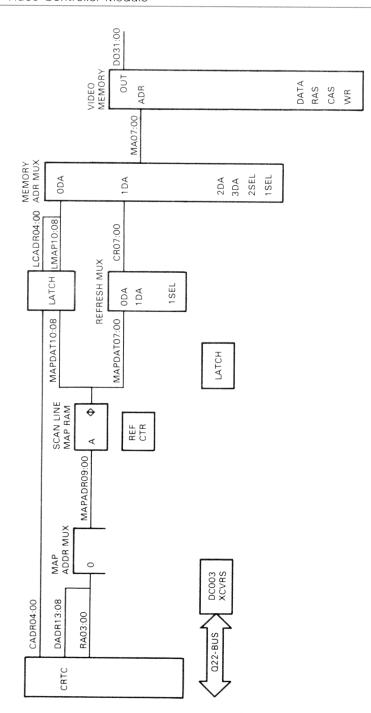

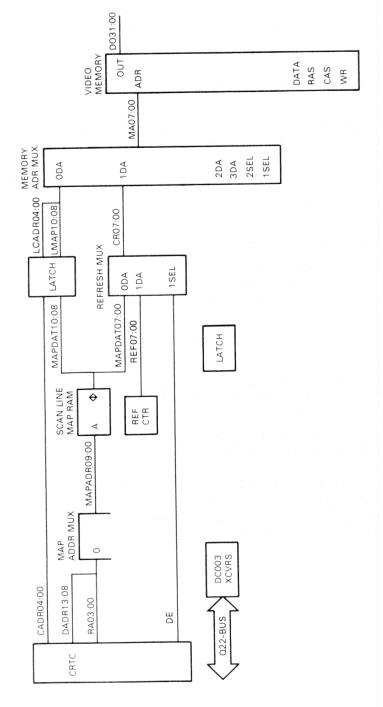

| C-1  | VCB01 Module, Simplified Block Diagram              | . C-2  |

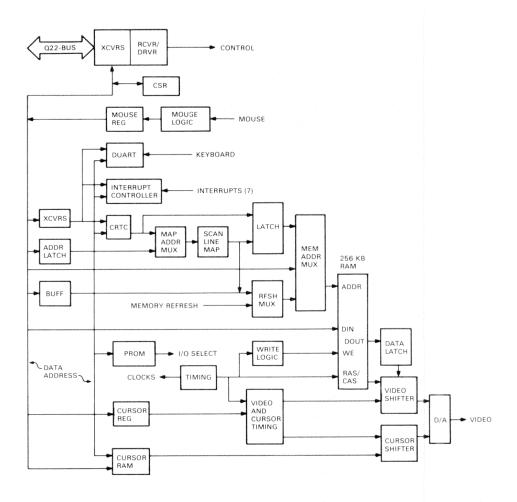

| C-2  | VCB01 Module, Functional Block Diagram              | . C-3  |

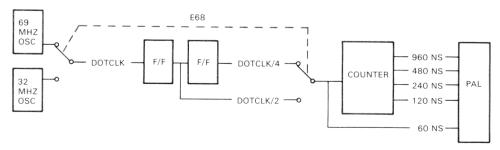

| C-3  | VCB01 Module, Simplified Timing Generator           | . C-4  |

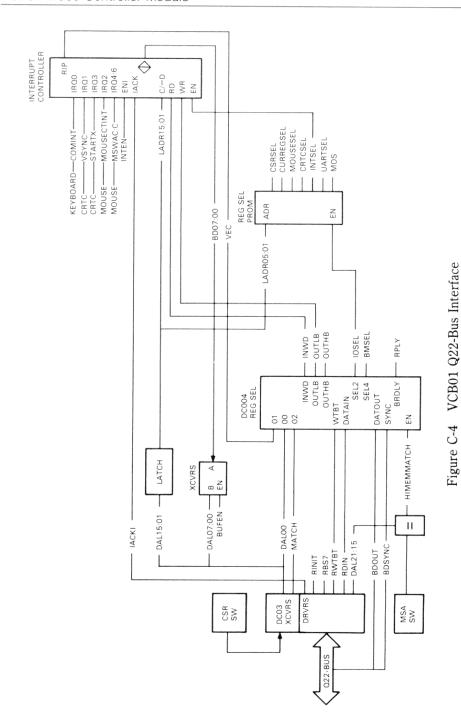

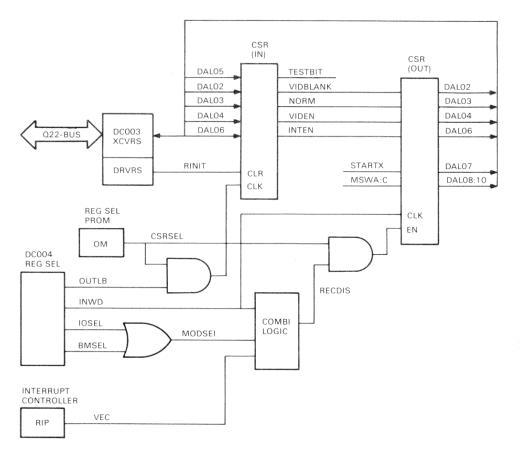

| C-4  | VCB01 Q22-Bus Interface                             | . C-6  |

| C-5  | VCB01 CSR Read/Write Paths                          | . C-8  |

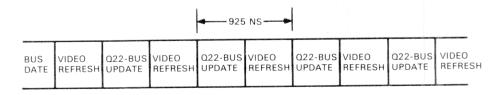

| C-6  | Video Memory Access Cycle                           | . C-9  |

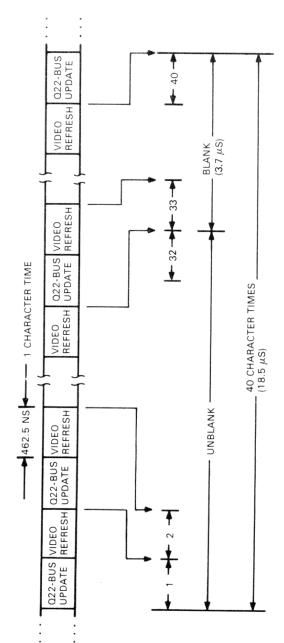

| C-7  | CRTC Horizontal Timing                              | C-10   |

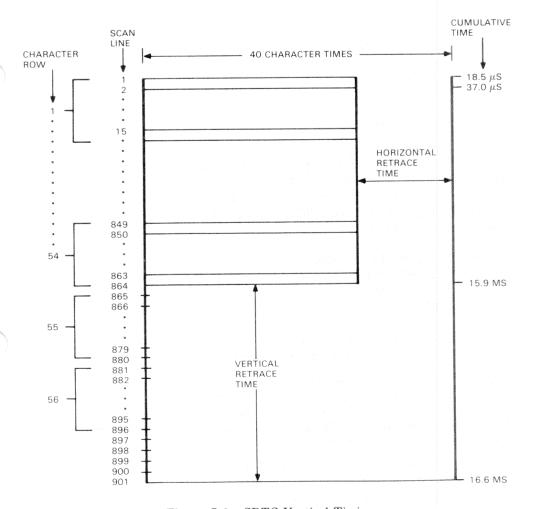

| C-8  | CRTC Vertical Timing                                |        |

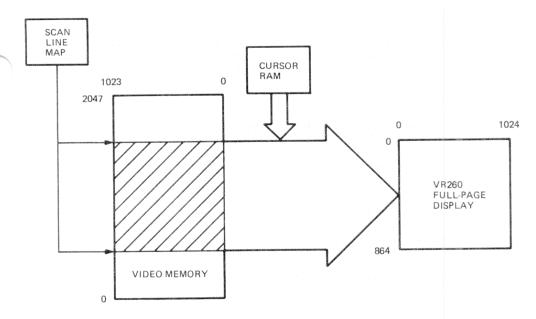

| C-9  | VR260 Monitor Display Mapping                            | C-13 |

|------|----------------------------------------------------------|------|

| C-10 | Video Memory Write (Update)                              |      |

| C-11 | Video Memory Read (Video Refresh)                        | C-18 |

| C-12 | Video Memory Read (RAM Refresh)                          |      |

| C-13 | Scan Line Map Write (Update)                             |      |

| C-14 | Cursor RAM Read/Write                                    |      |

| C-15 | Mouse Construction                                       |      |

| C-16 | Mouse Interface                                          |      |

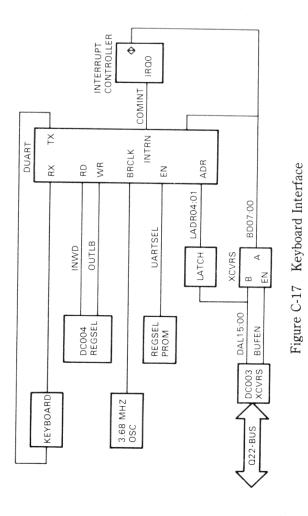

| C-17 | Keyboard Interface                                       |      |

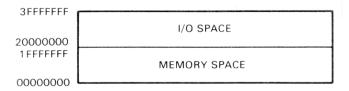

| C-18 | MicroVAX Physical Address Space                          |      |

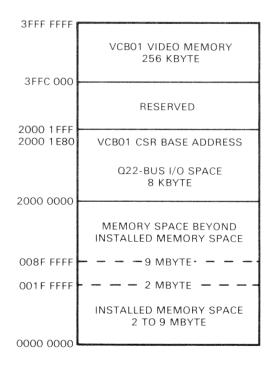

| C-19 | VAXstation II Physical Address Space                     |      |

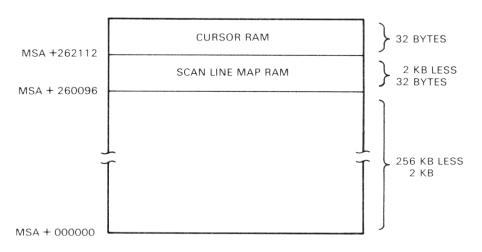

| C-20 | VCB01 256-Kbyte Address Space                            |      |

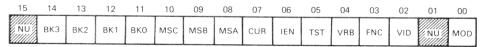

| C-21 | VCB01 CSR Format                                         |      |

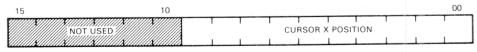

| C-22 | VCB01 Cursor X-Position Format                           |      |

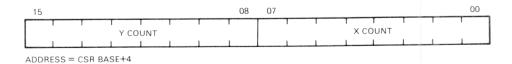

| C-23 | Mouse Position Register Format                           |      |

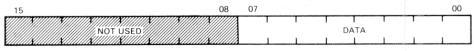

| C-24 | CRTC Address Register Pointer Format                     |      |

| C-25 | CRTC Data Register Format                                |      |

| C-26 | ICDR Register Format                                     |      |

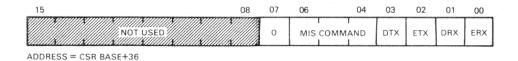

| C-27 | ICSR Format                                              | C-35 |

| C-28 | Mode Registers 1A and 2A Format                          |      |

| C-29 | Status/Clock Select Register A Format                    |      |

| C-30 | Command Register A Format                                |      |

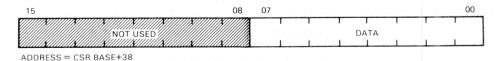

| C-31 | Transmit/Receive Buffer A Format                         |      |

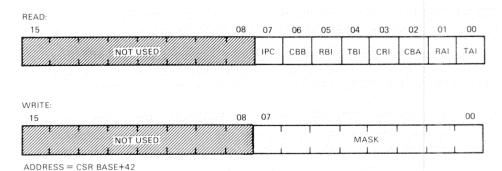

| C-32 | Interrupt Status/Mask Register Format                    |      |

|      |                                                          |      |

|      |                                                          |      |

|      | Tables                                                   |      |

|      |                                                          |      |

| 1-1  | VAXstation II Configuration                              |      |

| 1-2  | Regulator A and B Current and Power                      |      |

| 1-3  | Cutout, Insert Panel Size                                |      |

| 1-4  | VR260 Monitor Physical and Electrical Specifications     |      |

| 1-5  | LK201-AA Keyboard Physical and Electrical Specifications | 1-24 |

| 1-6  | VS10X Mouse Physical and Electrical Specifications       | 1-25 |

| 2-1  | Console Program Boot Sequence                            | 2-5  |

| 2-2  | CPU Patch Panel Insert Switches                          |      |

| 2-3  | MS630 Memory Modules                                     |      |

| 2-4  | RQDX3 Controller Module                                  |      |

| 2-5  | CSR Base Address Select                                  |      |

| 2-6  | VR260 Monitor Display Density Selection                  |      |

| 2-7  | RQDX3 Controller Module CSR Address                      | 2-14 |

| 2-8  | RQDX3 Controller Module LUN Jumpers                    |

|------|--------------------------------------------------------|

| 2-9  | M7546 Controller Module CSR Address2-20                |

| 2-10 | M7546 Controller Module Revision Level Switches 2-20   |

| 2-11 | M7546 Controller Module Unit Number Switches2-21       |

| 3-1  | Example of a 22-bit CSR Address                        |

| 3-2  | Example of Address Bits <12:03>                        |

| 3-3  | Example of Vector Bits < 08:03>                        |

| 3-4  | DEQNA CSR Address Settings                             |

| 3-5  | DEQNA Interrupt Vectors                                |

| 3-5  | DEQNA Interrupt Vectors                                |

| 3-6  | DZQ11 Module CSR Address                               |

| 3-7  | DZQ11 Module Interrupt Vector                          |

| 3-8  | Graphics Tablet Physical and Electrical Specifications |

| 3-9  | Graphics Tablet Pin Assignments 3-10                   |

| 4-1  | Power Requirements, Bus Loads, I/O Inserts             |

| 4-2  | Address/Vector Worksheet                               |

| 4-3  | Floating CSR Addresses                                 |

| 5-1  | Diagnostic LED Status and Error Messages               |

| 5-2  | DEQNA Module LEDs                                      |

| 5-3  | TQK50 Module LEDs                                      |

| 5-4  | VR260 Monitor Failure Indications                      |

| 5-5  | VR260 Monitor Failure Indications                      |

| 6-1  | BA123-A FRUs                                           |

| B-1  | Console Error Messages                                 |

| C-1  | VCB01 Clocks                                           |

| C-2  | Video Refresh Address Derivation                       |

| C-3  | VCB01 Registers                                        |

| C-4  | VCB01 CSR Bits                                         |

| C-5  | VCB01 Cursor X-Position Bits                           |

| C-6  | Mouse Position Register Bits                           |

| C-7  | CRTC Internal Registers                                |

| C-8  | CRTC Address Register Pointer Bits                     |

| C-9  | CRTC Data Register Bits                                |

| C-10 | ICDR Bits                                              |

| C-11 | ICSR Bits                                              |

| C-12 | ICSR Commands                                          |

| C-13 | Interrupt Controller Mode Register Bits                |

| C-14 | Mode Registers 1A and 2A Bits                          |

| C-15 | Status/Clock Select Register A Bits                    |

| C-16 | Command Register A Bits                                |

| C-17 | Transmit/Receive Buffer A Bits                         |

| C-18 | Interrupt Status/Mask Register Bits                    |

#### INTRODUCTION

The VAXstation II is a single-user workstation based on the MicroVAX II processor. It contains the VCB01 single-plane bit-mapped video subsystem, an RQDX3 mass storage subsystem, and the MicroVMS operating system. A technical/graphics workstation is formed with the addition of the VR260 monitor, an LK201-AA keyboard, and a VS10X-EA mouse. The workstation can be used as a stand-alone system, or, using the DEQNA Ethernet controller, in a clustered environment of print servers, disk servers, and other workstations.

This manual describes the VAXstation II base system, its service procedures, and configuration of options. The manual is meant as a reference tool for Digital's Field Service engineers trained to maintain the VAXstation II system.

- Chapter 1, System Introduction Describes and lists the general and physical characteristics of the base system.

- Chapter 2, System Description Describes the major functional components of the base system, and includes information about addresses, switches, and indicators.

- Chapter 3, Options Describes the optional modules that can be installed to extend the base system's capabilities, and includes information about the addresses, switches, and indicators of the options.

- Chapter 4, Configuration Describes configuration rules, and switch and jumper settings.

- Chapter 5, Diagnostics Describes the MicroVAX Maintenance System (MMS) and error reporting, and includes basic troubleshooting guidelines.

- Chapter 6, FRU Removal and Replacement Describes FRU removal and replacement procedures.

- Appendix A, Console Commands Describes the command line processor, and lists and describes the available commands, giving their proper syntax.

- Appendix B, Console Error Messages and Explanations Lists and describes the error messages generated by the command line processor.

- Appendix C, VCB01 Video Controller Module Describes the module's architecture and provides register and programming information.

#### CONVENTIONS USED IN THIS MANUAL

NOTE Contains general information.

CAUTION Contains information to prevent damage to equipment.

WARNING Contains information to prevent personal injury.

<mm:nn> Read as "mm through nn." This use of angle brackets and

the colon indicates a bit field or a set of lines or signals. For example, A<17:00> is the mnemonic for Unibus address

lines "A17 through A00."

<RETURN> A label enclosed by angle brackets represents a control or

special character key on the keyboard (in this case, the

Return key).

<CTRL>C Control sequence. Press the special function key <CTRL>

and the standard key C at the same time.

This chapter describes the general and physical characteristics of the VAXstation II. The major physical units are:

- 1. System Enclosure

- 2. Graphics Subsystem I/O Devices

#### 1.1 INTRODUCTION

The VAXstation II is a single-user workstation based on the MicroVAX II processor. It is mounted in the BA123 enclosure frame, a floorstanding unit for microcomputer systems. The enclosure is air cooled and is designed to operate in an open-office environment. It supports a variety of hardware options. Table 1-1 lists a typical VAXstation II configuration.

#### 1.2 SYSTEM COMPONENTS

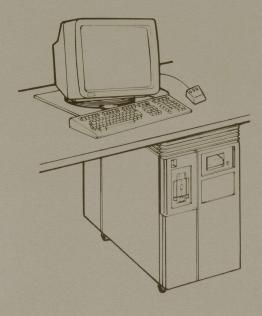

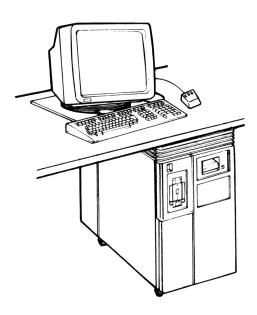

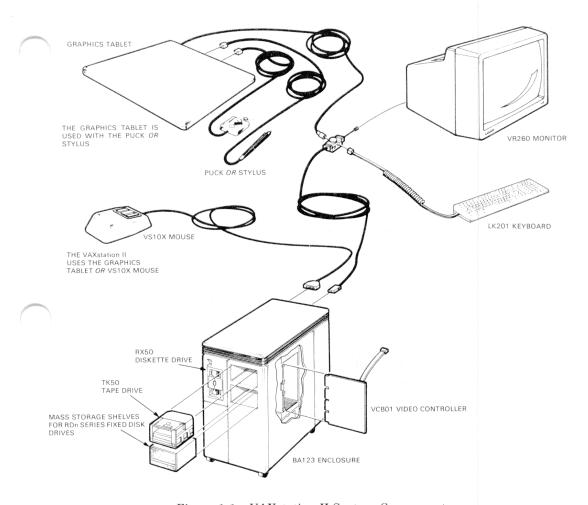

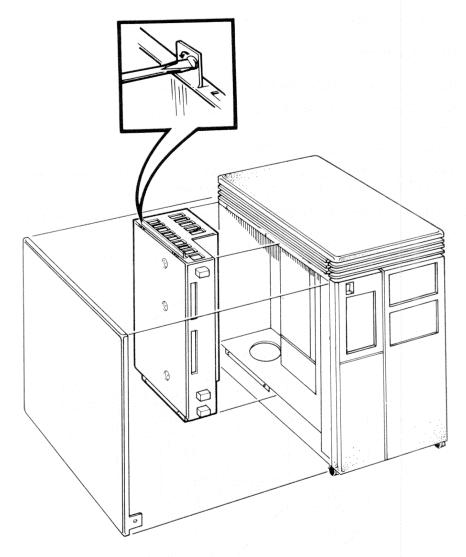

Several major components make up the VAXstation II. (Figure 1-1) These are the BA123 enclosure, which houses either an RD52 fixed disk drive and RX50 diskette drive, or an RD53 fixed disk drive and the TK50 tape drive, depending upon the particular system configuration. Also included within the BA123 enclosure are the system controls and indicators, backplane, mass storage area, power supply, and I/O distribution panel.

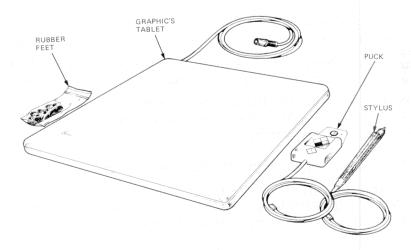

The VAXstation II graphics subsystem consists of a VR260 monochrome monitor, LK201 keyboard, VCB01 video controller, and the VS10X mouse. An optional graphics tablet that uses either a hand-held puck or stylus may be used in place of the mouse.

The VCB01 video controller is a quad-height module (part number M7602-YA) that provides a mouse interface, keyboard interface, and cursor controls for creating displays on the VR260 monitor.

Table 1-1 VAXstation II Configuration

| ***                     |           | T                                                                                                                                                                     |  |  |

|-------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Function                | Component | Description                                                                                                                                                           |  |  |

| CPU                     | KA630-AA  | MicroVAX II CPU with 1-Mbyte local (on-board) memory, boot/diagnostic ROM, floating point processor, console SLU (serial line unit), interval timer, and Q22-Bus map. |  |  |

| Memory                  | MS630-BA  | 2-Mbyte memory expansion module, quad-height, with 256K chips.                                                                                                        |  |  |

| Video Controller        |           | VCB01-KP VCB01 bit map video controller with interface for:                                                                                                           |  |  |

|                         |           | <ul><li>LK201 keyboard</li><li>VS10X-EA mouse</li><li>VS10X-XX tablet.</li></ul>                                                                                      |  |  |

| Mass-Storage Controller |           | RQDX3 Disk controller, supporting MSCP (mass storage control protocol) for:                                                                                           |  |  |

|                         |           | <ul> <li>RD52 31-Mbyte fixed-disk drive</li> <li>RX50 818-Kbyte dual diskette drive</li> <li>RD53 71-Mbyte fixed-disk drive.</li> </ul>                               |  |  |

| Tape Subsystem          |           | TQK50 95-Mbyte streaming tape subsystem, including tape drive and controller supporting TMSCP (tape mass storage control protocol).                                   |  |  |

Figure 1-1 VAXstation II System Components

#### 1.3 SYSTEM ENCLOSURE

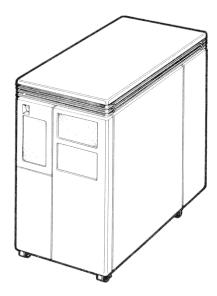

The BA123 enclosure (Figure 1-2) contains the MicroVAX II CPU, the VCB01 video controller, mass storage devices, and options. The air-cooled enclosure operates in an open-office environment and includes the following major sub-assemblies.

- Frame

- · Control panel

- · Mass storage area

- · Backplane assembly

- Power supply

- I/O (input/output) distribution panel

Figure 1-2 BA123 Enclosure

#### 1.3.1 BA123-A Frame

The BA123-A frame houses the power supply and the backplane assembly, and includes space for five 13.3 cm (5.25 in.) mass storage devices. Mounted on four shockproof castors, the BA123-A frame has the following dimensions.

Height: 62.2 cm (24.5 in)

Width: 33.0 cm (13.0 in)

Depth: 70.0 cm (27.5 in)

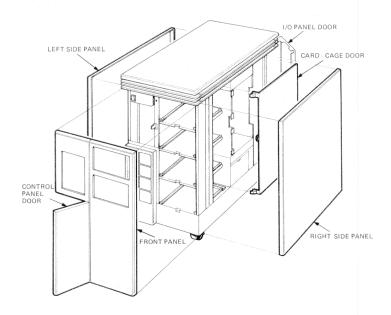

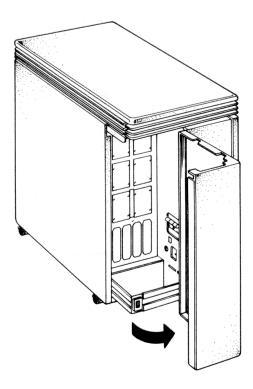

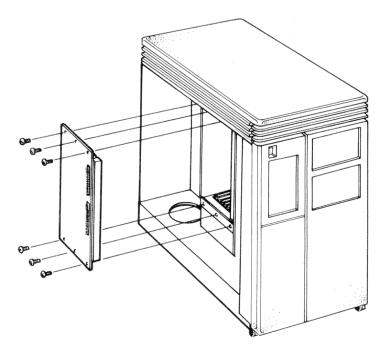

Removable panels cover the front, right, and left sides of the enclosure frame (Figure 1-3).

There are three doors: a control panel door on the front, an I/O panel door at the rear, and a card cage door inside the right side panel.

# NOTE For panel removal procedures, see section 6.1.

Figure 1-3 BA123 Removable Panels and Doors

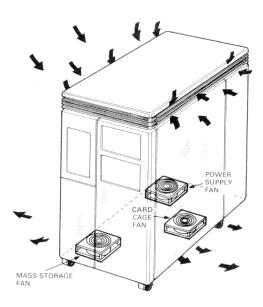

**1.3.1.1 Air Circulation** – Three fans in the BA123-A frame draw air from the bottom of the enclosure. (Figure 1-4) Air is drawn from below the module card cage, behind the control panel, and from inside the power supply.

**1.3.1.2 Temperature Sensor Printed Circuit Board** – A printed circuit (Pt board above the card cage contains two temperature sensors. (Figure 1-5) One sensor regulates the speed of the card cage fan at the minimum level required t maintain a constant temperature within the card cage. The other sensor, the overtemperature sensor, shuts down the system at high temperature. The card cage door encloses the area surrounding the modules. If this door is removed, an interlock switch is triggered, and the speed of the card cage fan is increased to maximum. If the proper temperature within the card cage cannot be maintained even at maximum fan speed, the over-temperature sensor will cause the system shut down. The system also shuts down if the card cage fan fails.

#### 1.3.2 Control Panel

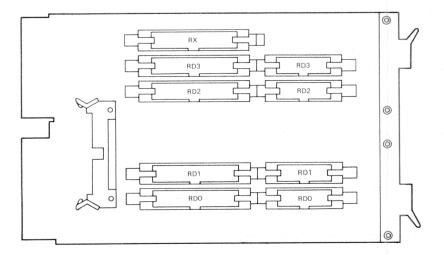

The control panel has six cutouts to provide space for control circuits. One cuto is used for a CPU console board. The other five cutouts provide space for mass storage control boards. Unused cutouts are covered with removable plates. Figu 1-6 shows the relation between the cutouts and the mass storage shelves.

Figure 1-4 Airflow

Figure 1-5 Temperature Sensors

Figure 1-6 BA123 Front Control Panel Cutouts

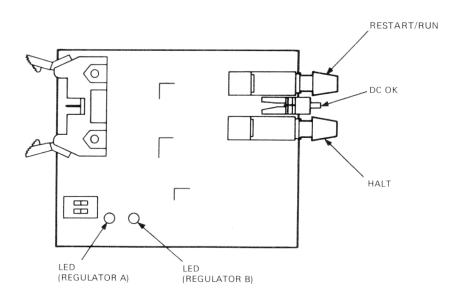

**1.3.2.1 CPU Console Board –** The CPU console board (Figure 1-7) is attached to the back of the control panel. It contains a DC OK indicator light and two buttons that let the user halt or restart the system. A ribbon cable connects the CPU console board to the backplane. This cable provides the connection between the CPU and the CPU console board.

Figure 1-7 CPU Console Board

The buttons and DC OK light provide the following functions.

When the HALT button is pressed, the red LED in the HALT button lights up.

If halts are enabled by the switch on the CPU distribution panel at the rear of the system, the system enters "Console I/O Mode" when the HALT button is pressed.

#### NOTE

If halts are disabled at the rear of the system, the LED in the HALT button will still light up when the button is pressed, but the system will not be halted.

- When the DC OK light is on, the system is receiving stable dc voltage from the power supply.

- When the RESTART button is pressed, the system boots.

There are two LEDs on the CPU console board. These can be seen by removing the left side panel of the enclosure. If the DC OK light on the control panel is not lit, the two LEDs on the CPU console board indicate which regulator supply to the backplane has failed.

```

Left LED = Regulator A

Right LED = Regulator B

```

LED is ON = +5 Vdc to the backplane is OK

LED is OFF = regulator or connection to regulator has failed.

#### NOTE

There should be at least one module in both an odd and even numbered backplane slot to draw enough current to start each regulator.

There is a DIP switch pack to the left of the LEDs that contains two switches. Both switches are normally OFF and are not used in VAXStation II systems.

### 1.3.3 Mass Storage Area

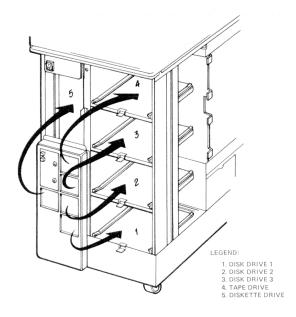

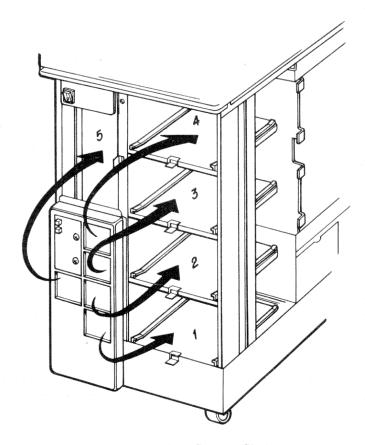

The front panel covers five shelves used for mounting 13.3 cm (5.25 in) mass storage devices. (Figure 1-8) The recommended maximum number of mass storage devices is four. These should be installed with two in shelves 1 and 2 and two in shelves 3, 4, or 5. Removable plates in front of shelves 3, 4, and 5 allow access to removable media devices.

Devices normally occupy the shelves as follows.

Figure 1-8 Mass Storage Shelves

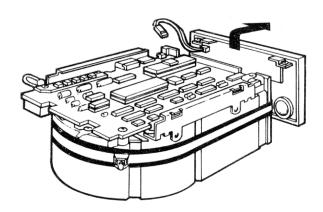

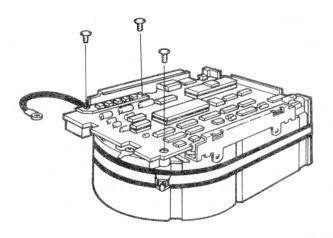

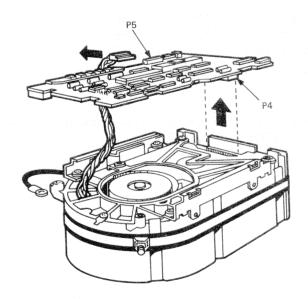

**1.3.3.1 Signal Distribution Board** – The Signal Distribution Board (M9058, Figure 1-9) is mounted in the bottom two (C and D) rows of backplane slot 13.

Figure 1-9 Signal Distribution Board

Up to four fixed disk drives, or an RX50 diskette drive and up to two fixed disk drives can be connected to the signal distribution board cabling. (Figure 1-10) The signal distribution board is connected to an RQDX3 mass storage controller module (M7555) in the card cage by a 50-conductor ribbon cable. The signal distribution board is also connected to the RD console boards behind the control panel by a 40-conductor ribbon cable.

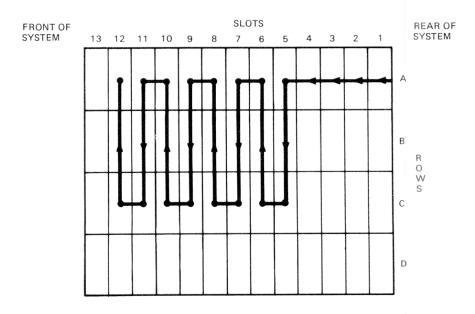

#### 1.3.4 Backplane Assembly

The BA123 has a four row by thirteen slot backplane that measures  $27.9 \times 19.9$  cm (11 in X 7.85 in). The backplane implements the extended LSI-11 bus (or Q22-Bus), which uses 22-bit addressing.

The first twelve slots of the backplane provide space for dual or quad-height modules that are compatible with the Q22-Bus.

A dual-height module has connectors that fit into two rows of a backplane slot. Two dual-height modules can occupy one backplane slot.

A quad-height module has connectors that fit into all four rows of a backplane slot. One quad-height module occupies one backplane slot.

#### NOTE

Dual-height modules in slots 5 through 11 and rows C and D of slot 12 require another dual-height module or an M9047 grant card in the other two rows of the slot.

Figure 1-11 shows the Q22-Bus interrupt and direct memory access (DMA) grant lines. The C and D rows of slots 1 through 4 implement a separate MicroVAX II local memory interconnect used to interface the system CPU and memory modules.

Four 120 ohm resistor packs between backplane slots twelve and thirteen are used to terminate the Q22-Bus.

The thirteenth slot of the backplane provides space for two dual-height modules (rows AB and CD). The Q22-Bus is not implemented in this slot. The CD rows are used for the signal distribution board. The AB rows can be used for a second signal distribution board. The thirteenth slot provides +5 Vdc, +12 Vdc, ground, and a signal (BDCOK) that indicates the dc voltage from the power supply is stable.

#### NOTE

This backplane is a "bounded" system. That is, an additional backplane cannot be connected to the system.

Figure 1-10 Signal Distribution Board Cabling

Figure 1-11 Backplane Grant Circuitry

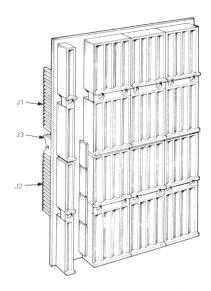

The backplane supports a maximum of 38 ac loads and 20 dc loads. The backplane balances the load on each of the power supply's two regulators. Figure 1-12 shows three J connectors on the backplane. J1 and J2 are 18-pin connectors that receive dc power and signals from two independent regulators in the power supply. J3 provides the connection between the CPU installed in the backplane and the CPU console board.

J1 is connected to regulator A, which supplies power to the odd-numbered slots and the resistor packs.

J2 is connected to regulator B, which supplies power to the even-numbered slots. J3 is a 10-pin connector for a cable to the CPU console board.

Figure 1-12 Backplane Connectors

The backplane has an eight layer PC board, which is arranged as follows.

- 1 Signal

- 2 Signal

- 3 Vdc from power supply regulator

- 4 Ground

- 5 Ground

- 6 +12 Vdc from power supply regulator

- 7 Signal

- 8 Signal

Chapter 4 explains the backplane configuration rules.

## 1.3.5 Power Supply

The power supply (Figure 1-13) is a 460-watt unit consisting of two regulators. Each regulator supplies power to one-half of the slots in the backplane and to the mass-storage devices inside the system.

Figure 1-13 Power Supply

The power supply provides protection against excess voltage and current, and protection against temporary fluctuations in the ac power supply. Table 1-2 lists the minimum and maximum currents supplied by each regulator.

#### NOTE

Total power used from each regulator must not exceed 230 W. This means that maximum current at +5 Vdc and +12 Vdc cannot be drawn at the same time. See the configuration worksheet in Chapter 4 for further information.

The power supply also has two separate +12 Vdc outputs that are independent of the main 460 W output. These are used to drive the two fans that are external to the power supply, and to provide power to the temperature sensor above the card cage.

The power supply contains a connector at the back for remote control of the power. The input power cable is protected by a circuit breaker. (Figure 1-14) There is an International Electrical Commission (IEC) ac input connector for compatibility with international power cables.

Two voltage ranges can be selected:

$$120 \text{ V} = 8 - 128 \text{ V} \text{ ac}$$

$240 \text{ V} = 176 - 256 \text{ V} \text{ ac}$

#### NOTE

In order to compensate for line cord voltage drop when the system is operating at maximum load, a minimum of 90 volts ac (88 – 128 V setting) should be present at the outlet for low-line operation.

Table 1-2 Regulator A and B Current and Power

| Regulator | Power<br>Maximum | Current at<br>Minimum |        | Current at<br>Minimum | 12 Vdc<br>Maximum |

|-----------|------------------|-----------------------|--------|-----------------------|-------------------|

| A         | 230 W            | 4.5 A                 | 36.0 A | 0.0 A                 | 7.0 A             |

| B         | 230 W            | 4.5 A                 | 36.0 A | 0.0 A                 | 7.0 A             |

Figure 1-14 Circuit Breaker, Voltage Select Switch, Connectors (Rear View)

**1.3.5.1 Electrical Distribution –** Figure 1-15 shows the electrical power distribution of the enclosure. The part numbers of the power cables are also shown.

NOTES: 1. (INCLUDES THE ON/OFF SWITCH) 17-00859-01

2. (INCLUDES INTERLOCK SWITCH) 17-00942-01

Figure 1-15 Electrical Distribution

#### 1.3.6 I/O Distribution Panel

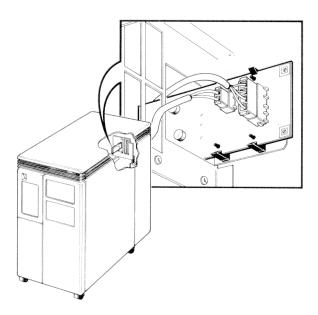

The I/O distribution panel is used for connecting the system to external devices. The rear door provides access to the I/O distribution panel. (Figure 1-16)

Each module that connects to an external device requires an internal cable, a filter connector, and an insert panel. Together, these three items are referred to as a cabinet kit.

Filter connectors are mounted in the insert panels. The insert panels install in cutouts in the I/O distribution panel. The CPU I/O distribution panel insert is typically mounted in cutout A. Unused cutouts are covered by removable plates.

Figure 1-16 Rear Door

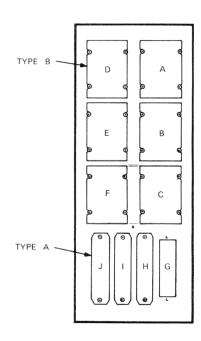

The rear I/O panel has ten cutouts. (Figure 1-17) Table 1-3 lists the cutout and corresponding panel sizes.

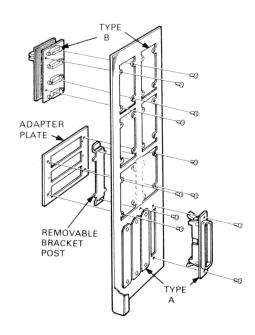

In addition, a removable bracket between the bottom two type B cutouts allows three more type A insert panels to be installed with an adapter plate. Figure 1-18 shows typical type A and type B insert panels, and the adapter plate.

Figure 1-17 Rear I/O Distribution Panel

Table 1-3 Cutout, Insert Panel Size

|            |                        | mm                             | in                                    |  |

|------------|------------------------|--------------------------------|---------------------------------------|--|

| Type A (4) | Cutout<br>Insert Panel | $15 \times 81$ $25 \times 102$ | $.6 \times 3.2$ $1.0 \times 4.0$      |  |

| Type B (6) | Cutout<br>Insert Panel | $57 \times 81$ $64 \times 84$  | $2.25 \times 3.2$<br>$2.5 \times 3.3$ |  |

Figure 1-18 I/O Insert Panels and Adapter Plate

#### 1.4 GRAPHICS SUBSYSTEM

The major physical units of the graphics subsystem are:

- Monitor

- Keyboard

- Mouse.

#### 1.4.1 VR260 Monitor

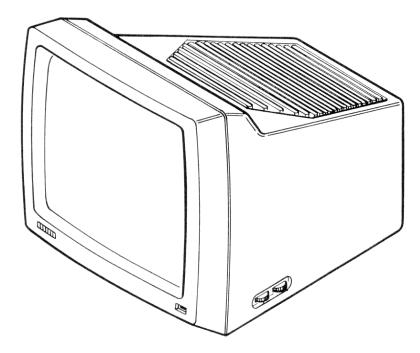

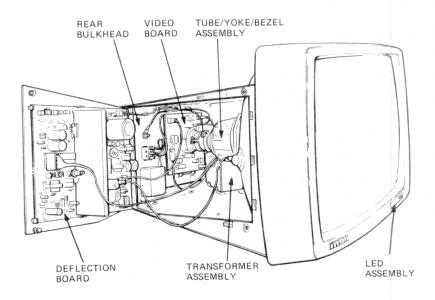

The VR260 is a 48 cm (19 in) diagonal, non-interlaced, 60 MHz, input bandwidth, monochrome monitor. (Figure 1-19) It can display graphics and text with a resolution of  $1024 \times 864$  pixels (horizontal  $\times$  vertical). It has a horizontal scan rate of 54 KHz and a 60 Hz refresh rate. Table 1-4 lists the monitor's physical and electrical specifications.

Figure 1-19 VR260 Monitor

Table 1-4 VR260 Monitor Physical and Electrical Specifications

| Height           | 38.10 cm (15.00 in)   |

|------------------|-----------------------|

| Width            | 45.72 cm (18.00 in)   |

| Depth            | 40.64 cm (16.00 in)   |

| Weight           | 20.50 kg (45.00 lb)   |

| Viewable<br>Area | 1024 	imes 864 pixels |

| AC Power         | 120 Vac at 1.0 A      |

| Requirement      | 240 Vac at 0.6 A      |

# 1.4.2 LK201 Keyboard

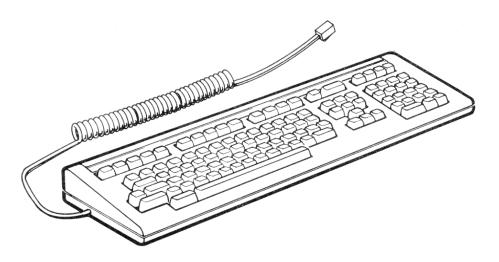

The VAXstation II keyboard, LK201-AA, (Figure 1-20) is connected to the VCB01 video controller subsystem through the I/O panel insert and a coiled, 4.78 m (19 ft), cable (BC18P-10). The keyboard's physical and electrical specifications are listed in Table 1-5.

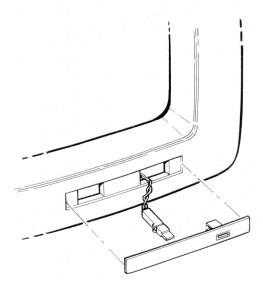

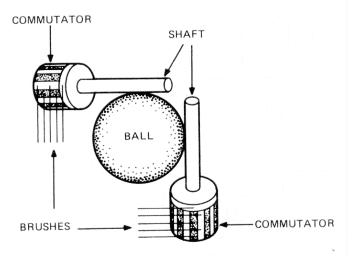

#### 1.4.3 VS10X Mouse

The mouse (Figure 1-21) is a hand-held device that moves a pointer displayed on the monitor screen. It is attached to and receives power from the VCB01 subsystem through the I/O panel insert and a 3.7 m (12 ft) cable. The mouse generates relative-position data (quadrature-encoded, X and Y axis), and includes three buttons for event signaling. The mouse's physical and electrical specifications are listed in Table 1-6.

Figure 1-20 LK201 Keyboard

Table 1-5 LK201-AA Keyboard Physical and Electrical Specifications

| Height<br>Width<br>Depth<br>Weight | 5.10 cm (2.00 in)<br>53.30 cm (21.00 in)<br>17.20 cm (6.75 in)<br>2.30 kg (5.00 lb) |  |

|------------------------------------|-------------------------------------------------------------------------------------|--|

| DC Power<br>Requirement            | +12.0 Vdc at 350 mA                                                                 |  |

Figure 1-21 VS10X Mouse Device

Table 1-6 VS10X Mouse Physical and Electrical Specifications

| Height<br>Width<br>Length<br>Weight | 3.30 cm (1.30 in)<br>7.00 cm (2.75 in)<br>9.50 cm (3.75 in)<br>0.50 kg (1.10 lb) |  |

|-------------------------------------|----------------------------------------------------------------------------------|--|

| DC Power<br>Requirement             | $+5.0 \text{ Vdc} \pm 10\% \text{ at} < 150 \text{ mA}$                          |  |

| Accuracy                            | 7.87 pulses/mm (200 pulses/in)                                                   |  |

| Rate of<br>Movement                 | 25.4 cm/s (10 in/s) or less                                                      |  |

This chapter describes the major functional components of the VAXstation II subsystems:

- 1. MicroVAX II processor

- 2. Graphics subsystem

- 3. Mass storage subsystem.

### 2.1 MicroVAX II PROCESSOR

In the base system, the MicroVAX II processor comprises the KA630 CPU module and an MS630 memory expansion module.

#### 2.1.1 KA630-A CPU

The KA630-A CPU includes:

MicroVAX processor chip, which provides a subset of the VAX instruction set and data types, as well as full VAX memory management.

### VAX data types:

- Byte, word, longword, quadword

- Character string

- Variable-length bit field.

- The remaining VAX data types are supported through software emulation.

#### VAX instruction set:

- Integer and variable

- Address

- Variable-length bit field

- Control and procedure call

- Queue

- MOVC3/MOVC5.

- The remaining VAX instructions, including floating point for the KA630-AB version, are supported through software emulation.

- 1 Mbyte of on-board memory, with support for one or two MS630 memory modules.

- Support for up to 4 Gbytes (2<sup>32</sup>) of virtual memory.

- Console SLU with externally selectable baud rate. The console SLU is accessed using four VAX IPRs (internal processor registers).

- Interval timer, with 10 ms interrupts. Interrupts are enabled via an IPR.

- 64-Kbyte boot/diagnostic ROM, which provides:

- A subset of the VAX console program

- Power-up diagnostics

- Boot programs for standard devices.

- Q22-Bus map/interface, provides DMA (direct memory access) for all local memory. The KA630-A processes Q22-Bus interrupt request levels BR7 through BR4.

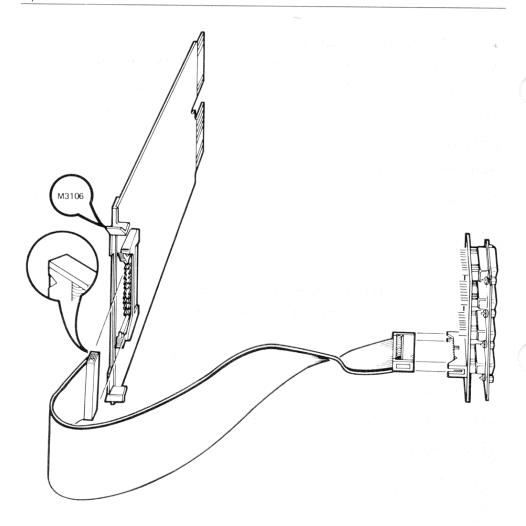

The KA630-A CPU communicates with mass storage and peripheral devices via the Q22-Bus. The KA630-A communicates with MS630 memory modules through a MicroVAX local memory interconnect in the CD rows of backplane slots 1 through 3, and through a cable between the CPU and MS630 memory modules.

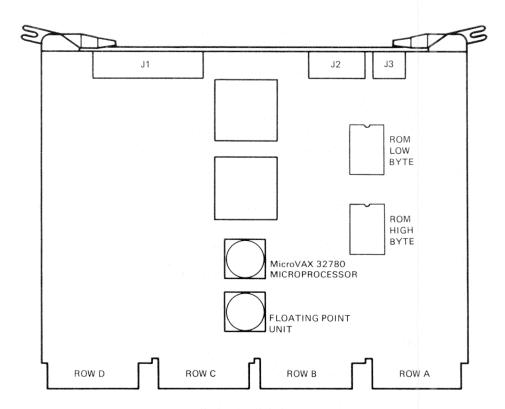

The KA630-A CPU module (Figure 2-1) has three connectors:

- J1 Connects to an MS630 memory module cable.

- J2 Connects to the configuration and display connector cable from the CPU patch panel insert.

- J3 Connects to the console SLU connector internal cable from the CPU patch panel insert.

## **CAUTION - CPU Slot Position**

A KA630-A CPU module must be installed only in backplane slot 1, 2, or 3 (all three contain the MicroVAX local memory interconnect). It must not be installed in slots 4 through 8.

Figure 2-1 KA630-A CPU Module

**2.1.1.1 Console Program** – The console program, resident in two ROM chips on the module, receives control whenever the processor halts. For the KA630-A CPU, a halt means only that processor control has passed to the console program, not that instruction execution stops. The processor halts as a result of:

- System power-up or Restart button pushed

- An external halt signal

- · Halt instruction execution

- A system error.

At power-up, the system enters one of three power-up modes. The mode is selected with a switch on the CPU patch panel insert (Paragraph 2.1.2). The console program then determines console device type and console language.

If the console device supports the MCS (multinational character set), the console program can be directed to output the console program in any one of 11 languages. The user language is recorded in battery backed-up RAM (Paragraph 2.1.2), which retains the language selection when the system is turned off.

If the console device does not support the MCS, there is no language prompt, and the console program defaults to English. The message "Performing normal system tests" is displayed. A diagnostic test countdown is displayed on the console terminal, in the CPU patch panel insert segmented-LED display, and in LEDs on the CPU module. These diagnostics test the CPU, memory system, and Q22-Bus interface. The diagnostic test codes and messages are described in Chapter 5.

If a halt has been caused by a condition other than power-up, the console program will branch directly to service the halt. Depending on the type of halt, the console program may branch to diagnostics, a restart sequence, a primary bootstrap routine, or console I/O mode.

If halts are enabled by the switch on the CPU patch panel insert (Paragraph 2.1.2), the console program will enter console I/O mode in response to any halt condition, including system power-up. Console I/O mode allows the user to control the system through the console terminal by use of a console command language (described in Appendix A). The console I/O mode prompt is >>>.

**2.1.1.2 Primary Bootstrap Program (VMB)** – If halts are disabled by the CPU patch panel switch, and the diagnostic tests are completed successfully, the console program will try to bootstrap (load and start) an operating system. The console program first searches for a 64-Kbyte error-free segment of system memory. Next, it copies VMB (the primary bootstrap program) from the console program ROM into the segment at base address +512. The console program then branches to VMB. VMB attempts to bootstrap an operating system from one of the devices listed in Table 2-1, starting at the top.

| Table 2-1 Console Program | m Boot Sequence |

|---------------------------|-----------------|

|---------------------------|-----------------|

| Priority | Controller          | Type - Designation                     | Q22-Bus CSR Address                                                                             |  |  |  |  |

|----------|---------------------|----------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| 1        | RQDX<br>RC25<br>KDA | MSCP (Disk) – DUAn<br>– DAAn<br>– DJAn | 17772150 (first)<br>Floating (additional)                                                       |  |  |  |  |

| 2        | TK50                | MSCP (Tape) – MUAn                     | 17774500 (first)<br>Floating (additional)                                                       |  |  |  |  |

| 3        | MRV11               | PROM – PRAn                            | Program searches for a valid signature block at 4K boundaries within the Q22-Bus address range. |  |  |  |  |

| 4        | DEQNA               | ETHERNET – XQAn                        | 17774440 (first)<br>17774460 (additional)                                                       |  |  |  |  |

When VMB determines that a controller is present, it searches in order of increasing unit number for a bootable unit with a removable volume. If it finds none, it will repeat the search for a nonremovable volume.

The system can also be directed to enter VMB through console I/O mode by use of the boot command, followed by the unit designation and number; for example, B DUA0.

When the operating system is booted, the processor no longer executes instructions from the console program ROM. The processor is then in program I/O mode, and terminal interaction is controlled by the operating system.

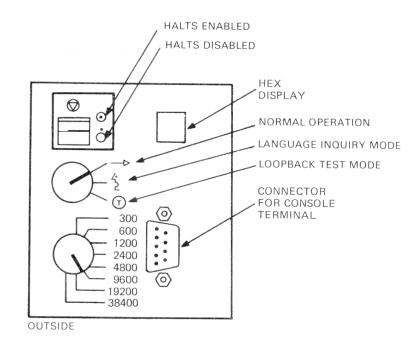

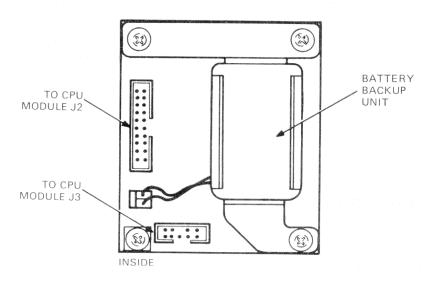

#### 2.1.2 CPU Patch Panel Insert

The CPU patch panel insert (Figure 2-2), mounted in the rear I/O distribution panel, contains:

- 3 switches

- 1 segmented-LED display

- · 1 external connector

- 2 internal connectors

- 1 BBU (battery backup unit).

Table 2-2 describes the CPU patch panel insert's switches.

Figure 2-2 CPU Patch Panel Insert

| Table 2-2 | CPU Patch | Panel Insert | Switches |

|-----------|-----------|--------------|----------|

|-----------|-----------|--------------|----------|

| rabic = =        | 01 0 1 0100 |                                                                                                                                                                   |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Switch           | Position    | Function                                                                                                                                                          |

| Halt<br>Enable   | Dot         | Factory setting; halts are disabled. On power-up or restart, the system will enter VMB at the completion of start-up diagnostics.                                 |

|                  | Circled dot | Halts are enabled. On power-up or restart, the system will enter console I/O mode at the completion of start-up diagnostics.                                      |

| Power-Up<br>Mode | Arrow       | Factory setting; Run. If the console terminal supports MCS, the user will be prompted for language only if the BBU has failed. Full start-up diagnostics are run. |

|                  | Face        | Language Inquiry. If the console terminal supports MCS, the user will be prompted for language on every power-up and restart. Full start-up diagnostics are run.  |

|                  | Circled T   | Test. ROM programs run wrap-around SLU tests.                                                                                                                     |

| Baud<br>Rate     | 1 through 8 | Factory-set to 4800 baud. Sets the baud rate of the console terminal serial line. The baud rate selection must match the console terminal's baud rate.            |

The segmented-LED displays the number of the currently executing power-up test or bootstrap procedure. If a failure occurs, the number displayed represents the FRU that is the most probable cause of the failure. Test numbers are defined in Chapter 5. The 9-pin external and internal SLU connectors connect the console terminal cable to the cable from connector J3 on the KA630-A CPU module.

The 20-pin internal configuration and display connector connects the three switches and the segmented-LED display to the cable from connector J2 on the KA630-A CPU module.

When system power is off, the BBU (battery backup unit) provides power to the TOY (time-of-year) clock chip on the KA630-A CPU module. The code for the user's language is stored in RAM on the TOY chip, and is lost if the BBU fails.

For more information, refer to the *KA630-AA CPU Module User's Guide* (EK-KA630-UG).

# 2.1.3 MS630 Memory Module

The MS630 memory module provides memory expansion for the KA630-A CPU module. It is available in three versions (Table 2-3), all populated with 256 K RAMs.

Table 2-3 MS630 Memory Modules

| Version  | Part<br>Number | Capacity | Height |  |  |

|----------|----------------|----------|--------|--|--|

| MS630-AA | M7607-AA       | 1 Mbyte  | Dual   |  |  |

| MS630-BA | M7608-AA       | 2 Mbyte  | Quad   |  |  |

| MS630-BB | M7608-BA       | 4 Mbyte  | Quad   |  |  |

One or two MS630 modules can be used in the VAXstation II. The MS630 modules interface with the KA630-A CPU through the MicroVAX local memory interconnect and an "over-the-top" cable. The MicroVAX local memory interconnect is implemented in the CD rows of backplane slots 1, 2, and 3. The over-the-top cable is connected to J1 on the KA630-A CPU and the corresponding 50-pin connector(s) on the MS630 module(s). There are no hardware settings on the MS630 module.

CAUTION – MS630 Memory Module Slot Position

An MS630-B module must be installed only in backplane slot 2

or 3. It must not be installed in slots 4 through 8. The MS630-AA

can be installed only in the CD rows of slots 2 and 3.

For an overview of module configuration, see Chapter 3, Paragraph 3.1.2.

## 2.2 GRAPHICS SUBSYSTEM

### 2.2.1 VCB01 Video Controller Module

The VCB01 controller kit includes the M7602-YA controller module, an I/O distribution panel insert, and a module-to-insert cable.

The VCB01 is a quad-height, Q22-Bus bit-mapped video option module (Figure 2-3) that provides workstation capability for Q22-Bus systems.

An on-board, 256-Kbyte, MOS RAM bit-map memory (also called video memory) resides in the Q22-Bus address space. In the VAXstation II, a subset of the bit-mapped video memory is displayed on the 48 cm (19 in) VR260 monochrome monitor. This subset is sometimes called screen memory. The VCB01 relies on the CPU to generate all images stored in video memory.

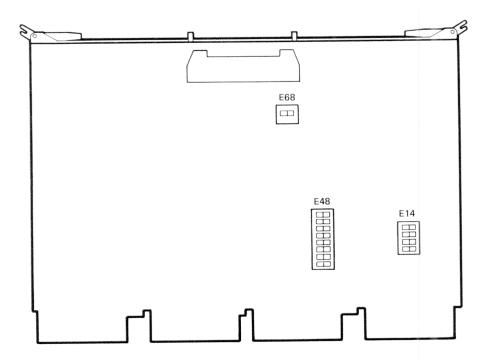

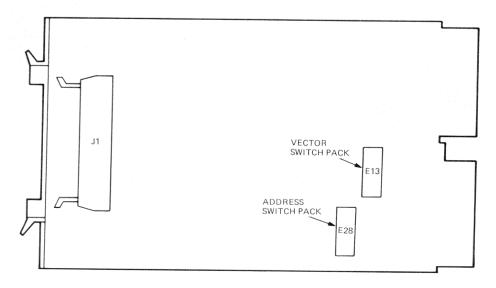

Figure 2-3 VCB01 Video Controller Module

The VCB01 also provides several basic I/O functions, including:

- Cursor controls

- Mouse interface

- Keyboard interface

- Primitives for VT100-style split-screen scrolling.

The VCB01 contains switches to select:

- MSA (memory starting address)

- CSR (control and status register) base address

- Display density.

**2.2.1.1 Memory Starting Address (MSA)** – Switches 1 through 4 of switch-pack E14 select the starting address for the 256-Kbyte block of MicroVAX physical memory where the VCB01 module resides. To take advantage of certain MicroVAX architectural features when programming bit-map operations, the video memory always resides in the topmost 256 Kbytes of the I/O physical address space. Therefore, all the MSA switches are set to OFF; that is, address bits <21:18> select the 256-Kbyte block starting at 3C0000 (hexadecimal). (Note that this is equivalent to address 3FFC0000 in the I/O physical address space. See Paragraph C.2.1.) Refer to Table 2-4.

Table 2-4 VCB01 MSA Selection

| Address Bit:     | A21 | A20 | A19 | A18 |          |

|------------------|-----|-----|-----|-----|----------|

| Switch E14:      | 1   | 2   | 3   | 4   |          |

| Switch Setting:* | 1   | 1   | 1   | 1   |          |

| MSA Address:     | 1   | \   | 7   |     | 000 000† |

<sup>\*</sup> 0 = off; 1 = on

**2.2.1.2 CSR Base Address** – In the system I/O page, 32 locations are allocated to the VCB01 module. These locations allow the CPU and VCB01 to exchange control and status information through hardware registers on the VCB01. As a group, these registers are called CSRs, but the first register is specifically named the CSR. Switches 1 through 7 of switch-pack E48 correspond to address bits <12:06> and select the base address for these registers. (Table 2-5) In the VAX-station II system, E48 switches S1:S7 are set to 1E80 (hexadecimal). (See Appendix C, Figure C-19.)

Table 2-5 CSR Base Address Select

| CSR Address:     | 1777 |     | 7   |     |     | 2   |     | 00† |

|------------------|------|-----|-----|-----|-----|-----|-----|-----|

| 00D 444          |      | \   |     |     | \   |     | /   |     |

| Switch Setting:* | 1    | 1   | 1   | 1   | 0   | 1   | 0   |     |

| Switch E48:      | 1    | 2   | 3   | 4   | 5   | 6   | 7   |     |

| Address Bit:     | A12  | A11 | A10 | A09 | A08 | A07 | A06 |     |

<sup>\*</sup> 0 = off; 1 = on

<sup>†</sup> <A17:A00> = 0

$<sup>\</sup>dagger < A05:A00 > = 0$

**2.2.1.3 Display Density** – The VCB01 module can drive either full-page or halfpage monitors, as selected by switch E68 and switch S8, respectively, of switch-pack E48. The VR260 monitor used in the VAXstation II system is a full-page monitor, and is selected as shown in Table 2-6. Half-page monitors are not supported.

# Table 2-6 VR260 Monitor Display Density Selection

E68 = On (C2) E48/S8 = Off

For more detailed information on the VCB01 video controller module see Appendix C.

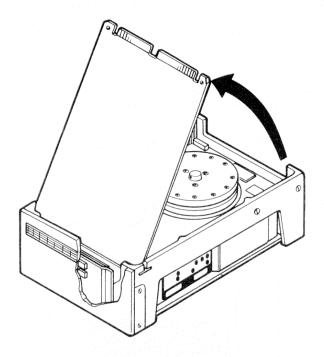

#### 2.2.2 VR260 Monitor

The VR260 monitor has three external controls (on/off, contrast, and brightness) and one indicator (power-on LED). Internal alignment controls and adjustments are described in Chapter 6.

The monitor has a self-contained power supply and its own ac power cord. It is connected to the system via the VCB01 I/O panel insert by the BC18P-10 cable. The keyboard and data pad are connected at the monitor end of this cable.

## 2.2.3 LK201 Keyboard

The LK201 keyboard is driven by a microprocessor and contains a set of microdiagnostics. Communication between the keyboard and the VCB01 module is full-duplex, serial/asynchronous at 4800 baud, and conforms to EIA standard RS423. The keyboard lead is terminated in a 4-pin modular connector that plugs into the monitor end of the BC18P-10 video cable.

#### 2.2.4 VS10X Mouse

The hand-held VS10X mouse controls the pointer image (icon) on the monitor screen. It provides relative pointer position to the VCB01 in the form of X-coordinate and Y-coordinate pulse outputs. Three push buttons on the mouse perform software-defined functions. The mouse is connected to the VCB01 I/O panel insert with a 3.7 m (12 ft) 10-conductor cable.

# 2.3 MASS STORAGE SUBSYSTEM

The base system's mass storage subsystem can be configured differently from that shown in Table 1-1. For an overview of ordering information and module configuration see Chapter 3.

### 2.3.1 RQDX3 Disk Controller

Order: RQDX3-BA

Controller kit includes:

• RQDX3 M7555 controller module

• 17-00861-1 50-pin signal cable

For more information, refer to the *RQDX3 Controller Module User's Guide* (EK-RQDX3-UG).

The dual-height RQDX3 controller module provides the interface between the Q22-Bus and the fixed disk and diskette drives. It is an intelligent controller with on-board microprocessors. Data is transferred using DMA; control and status communication between the host and controler uses MSCP (mass storage control protocol).

The RQDX3 can control up to four drives. Each fixed drive counts as one drive; each RX50 dual diskette drive counts as two.

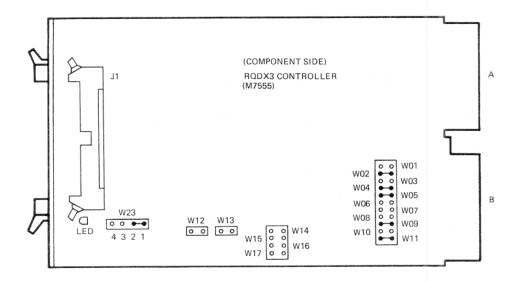

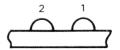

Figure 2-4 shows the jumper and LED locations for the RQDX3 controller module.

Figure 2-4 RQDX3 Controller Module

**2.3.1.1 CSR Address and Interrupt Vector** – The CSR address of the first RQDX3 module is fixed at 17772150 (factory-set). If a second RQDX3 is installed, its CSR address is floating, and set with jumpers A12:A2. (Table 2-7).

### NOTE - MSCP Device CSR Address

The RQDX3 controller module is an MSCP device. The first MSCP device in a system is assigned a CSR address of 17772150. If more than one MSCP device is installed, the CSR address of the second device must be set within the floating range 17760010 through 17763776.

Table 2-7

| Management                                         |           |              |     |     |     |     |     |     |     |     |          |

|----------------------------------------------------|-----------|--------------|-----|-----|-----|-----|-----|-----|-----|-----|----------|

| Address Bit/<br>Jumper:                            | A12       | A11          | A10 | A09 | A08 | A07 | A06 | A05 | A04 | A03 | A02      |

| Jumper Position:*<br>(factory-set)<br>CSR Address: | 1<br>1777 | 0            | 2   | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 0<br>0 † |

| Jumper Position:                                   | 0         | 0            | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 1   | 1        |

| CSR Address:                                       | 1776      | ,            | 0   |     | -   | 3   |     | \   | 3   |     | 4        |

| Jumper Position:                                   | 0         | 0            | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 1   | 1        |

| CSR Address:                                       | 1776      | · menonement | 0   |     | -   | 3   |     | -   | 5   |     | 4        |

| Jumper Position:                                   | 0         | 0            | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 1        |

**RQDX3** Controller Module CSR Address

1776

0

CSR Address:

The RQDX3 interrupt vector is set under program control. The first RQDX3 interrupt vector is fixed at 154. If a second RQDX3 is installed, its interrupt vector is floating.

4

**2.3.1.2 Logical Unit Number** – In addition to the CSR address and interrupt vector, the RQDX3 LUN (logical unit number) jumpers LUN0 through LUN7 must be configured. The jumpers represent a binary-weighted value and can be configured to assign any four LUNs to an RQDX3, starting with any LUN. The RQDX3 module is shipped with no LUN jumpers installed. No LUN jumpers installed assigns LUNs 0 through 3 to the module, and is the correct configuration for the first RQDX3 in a system. (Table 2-8) If a second RQDX3 is installed, jumper LUN2 would normally be installed, assigning LUNs4 through 7 to the second RQDX3; and so on.

<sup>\* 0 =</sup> removed; 1 = installed

<sup>†</sup> <A01:A00> = 0

Table 2-8 RQDX3 Controller Module LUN Jumpers

| Jumper:    | LUN7 | LUN6 | LUN5 | LUN4 | LUN3 | LUN2 | LUN1 | LUN0 | LUNs  |

|------------|------|------|------|------|------|------|------|------|-------|

| Value:     |      |      | 32   | 16   | 8    | 4    | 2    | 1    |       |

| Jumper     |      |      |      |      |      |      |      |      |       |

| Position:* | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 3:0   |

|            | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 4:7   |

|            | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 8:11  |

|            | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 12:15 |

|            | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 16:19 |

|            | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 20:23 |

|            | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 24:27 |

|            | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 28:31 |

|            | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 32:35 |

<sup>\*</sup> 0 = removed; 1 = installed

# 2.3.2 RD52 and RD53 Fixed Disk Drives

Order: RD5nA-AA

Disk kit (n = 2 or 3) includes:

• RD5n-A Disk drive

17-00282-00 20-wire signal distribution cable

17-00286-00 34-wire signal distribution cable

For more information, refer to the RD52-D, -R Fixed Disk Drive Subsystem Owner's Manual and the 113-UC/11C23-UE RD52 Upgrade Installation Guide.

The RD52 and RD53 are fixed disk drives with formatted storage capacities of 31 and 71 Mbytes, respectively.

In addition to the cables listed above, a cable from the power supply must be connected to each RD drive in the system. If an RD5n drive is added to the system, it must be formatted. The formatting utility is included in the maintenance section of the MicroVAX II Diagnostics Kit.

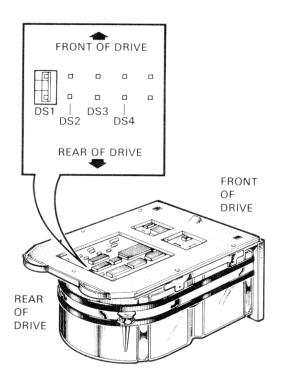

**2.3.2.1 RD52 Configuration** – The RD52 read/write PC board has five pairs of pins (Figure 2-5) that are used to select the drive. To configure an RD52 as drive DU0, place a jumper on pin-pair DS3.

Figure 2-5 RD52 Fixed Disk Drive

**2.3.2.2 RD53 Configuration** – The RD53 read/write PC board has four switches at its rear edge. With the rear of the drive at the left, the switches are numbered:

To configure an RD53 as drive DU0, press switch 3.

# 2.3.3 RX50 Diskette Drive

Order: RX50A-AA

Diskette drive kit includes:

RX50-AA

Diskette drive

• 17-00867-00

34-wire signal distribution cable

The RX50 drive (Figure 2-6) is a random-access, dual diskette storage device that uses two single-sided 13.3 cm (5.25 in) diskettes. It has a total formatted capacity of 818 Kbytes (409 Kbytes per diskette). The diskettes are inserted into slots behind the drive's two access doors. A light next to each slot indicates when the system is reading or writing the diskette in that slot.

One RQDX3 controller supports only one RX50 diskette drive.

Figure 2-6 RX50 Diskette Drive

### 2.3.4 TK50 Tape Drive Subsystem

Integral TK50 tape drive subsystem:

Order: TK50-AA

Tape drive and tape cartridge

TOK50-AA

M7546 controller module and internal cable

Stand-alone TK50 tape drive subsystem:

Order: TK50-DA, -DB (DA = 120 V, DB = 240 V line cord)

Tape drive and tape cartridge

TQK50-AB

M7546 controller module, internal cable, and filter connector

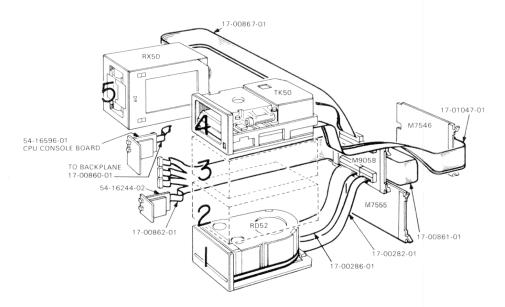

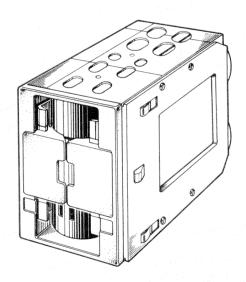

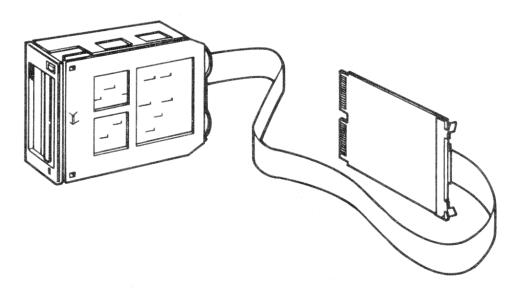

The TK50 is a streaming tape drive subsystem (Figure 2-7) that uses 95-Mbyte magnetic tape cartridges for backup data storage.

Figure 2-7 TK50 Tape Drive Subsystem

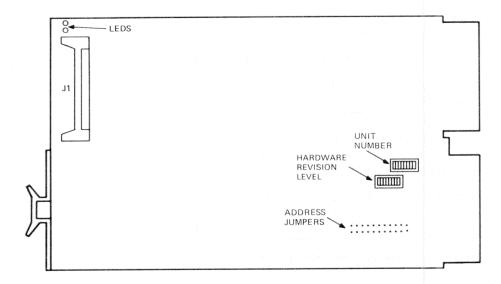

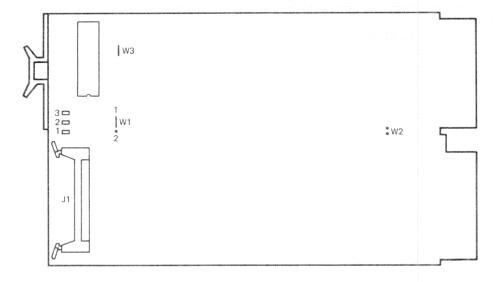

The M7546 controller module (Figure 2-8) provides the interface between the TK50-AA tape drive and the Q22-Bus.

Figure 2-8 M7546 Controller Module

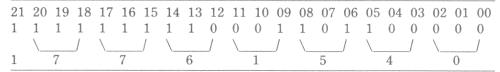

**2.3.4.1 M7546 Controller Module CSR Address and Interrupt Vector** – The M7546 controller module is a TMSCP (tape mass storage control protocol) device. The CSR address of the first M7546 module is fixed at 17774500 (factory-set). If a second TK50 subsystem is installed, the CSR address of the second M7546 module is floating in the range 17760010 through 17763776, and set with jumpers A12:A2. (Table 2-9)

Table 2-9 M7546 Controller Module CSR Address

| Address Bit/                    | The second secon |                                         |     |     | *************************************** |     |              | mana anakan kariniyi di ada ada ada ada ada ada ada ada ada |                                         |                       |      |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|-----|-----------------------------------------|-----|--------------|-------------------------------------------------------------|-----------------------------------------|-----------------------|------|

| Jumper:                         | A12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A11                                     | A10 | A09 | A08                                     | A07 | A06          | A05                                                         | A04                                     | A03                   | A02* |

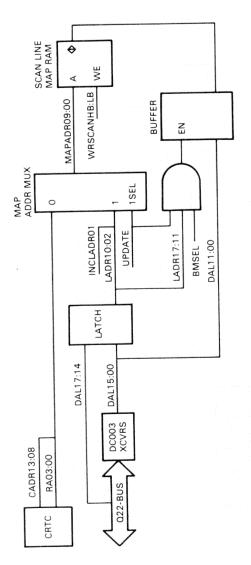

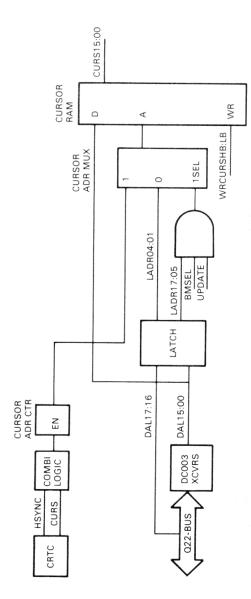

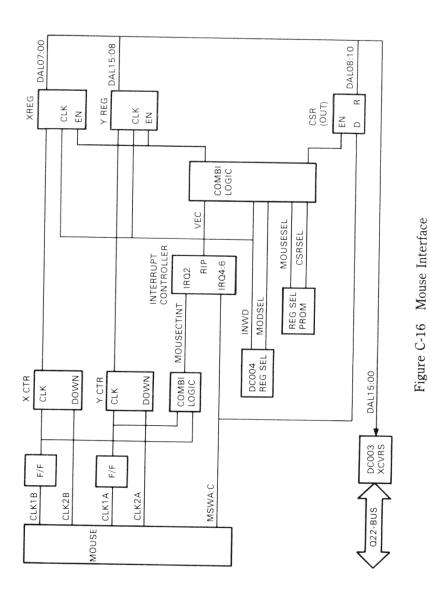

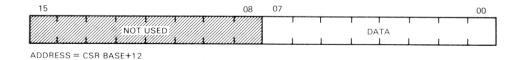

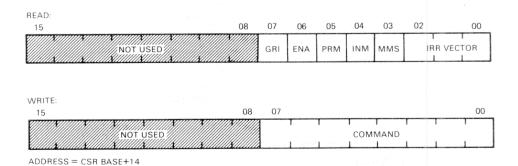

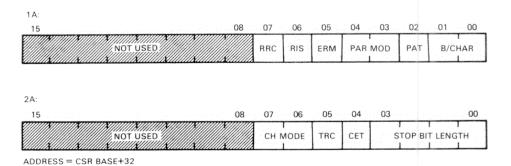

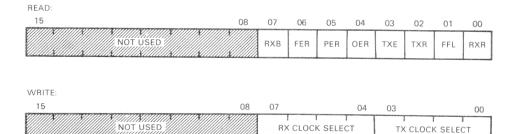

| Jumper Position:† (factory-set) | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                       | 0   | 0   | 1                                       | 0   | 1            | 0                                                           | 0                                       | 0                     | 0    |