# DEC 7000/10000 AXP VAX 7000/10000 Platform Technical Manual

Order Number EK-7000A-TM.001

This manual is a reference for Digital service engineers. It describes the platform architecture, the LSB bus, and the power, cabinet control, and cooling systems of the DEC 7000 AXP, DEC 10000 AXP, VAX 7000, and VAX 10000 systems.

digital equipment corporation maynard, massachusetts

#### **First Printing, August 1993**

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright © 1993 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

| Alpha AXP         | DECUS   | VAXBI        |

|-------------------|---------|--------------|

| AXP               | DWMVA   | VAXELN       |

| DEC               | OpenVMS | VMScluster   |

| DECchip           | ULTRIX  | XMI          |

| DEC LANcontroller | UNIBUS  | The AXP logo |

| DECnet            | VAX     | digital      |

OSF/1 is a registered trademark of the Open Software Foundation, Inc.

**FCC NOTICE:** The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

# Contents

| Preface | vii |

|---------|-----|

|---------|-----|

# Chapter 1 Platform Overview

| 1.1 | DEC 7000/VAX 7000 Cabinets                  | . 1-2 |

|-----|---------------------------------------------|-------|

| 1.2 | DEC 10000/VAX 10000 Cabinets                | . 1-2 |

| 1.3 | Cabinet Components                          | . 1-3 |

| 1.4 | LSB Card Cage                               | . 1-4 |

| 1.5 | Power, Cabinet Control, and Cooling Systems | . 1-5 |

| 1.6 | Plug-In Units                               |       |

# Chapter 2 LSB Bus

| 2.1     | Overview                         | 2-2    |

|---------|----------------------------------|--------|

| 2.1.1   | LSB Bus Specifications           | 2-2    |

| 2.1.2   | Module Identification            | 2-3    |

| 2.1.3   | Signals                          | 2-4    |

| 2.2     | Arbitration                      | 2-6    |

| 2.2.1   | Signals Used in Arbitration      | 2-6    |

| 2.2.2   | Arbitration Request Process      |        |

| 2.2.3   | Arbitration Grant Process        | 2-7    |

| 2.2.4   | Recognizing Command Cycles       | 2-8    |

| 2.2.5   | Processor Arbitration Scheme     | 2-8    |

| 2.2.6   | Memory Bank Contention           | 2-9    |

| 2.2.7   | IOP Arbitration Priority Scheme  | . 2-10 |

| 2.3     | Bus Cycles                       | . 2-11 |

| 2.3.1   | Command Cycle                    | . 2-11 |

| 2.3.2   | Data Cycle                       | . 2-13 |

| 2.3.3   | ECC Coding                       | . 2-13 |

| 2.4     | Bus Transactions                 | . 2-15 |

| 2.4.1   | Signals Used in Bus Transactions | . 2-15 |

| 2.4.2   | Timing Definition                | . 2-17 |

| 2.4.3   | Transaction Examples             | . 2-17 |

| 2.4.4   | Interrupts                       | . 2-18 |

| 2.4.4.1 | Vectored Interrupts              | . 2-18 |

| 2.4.4.2 | Non-Vectored Interrupts          | . 2-19 |

| 2.5     | Memory Bank Mapping              | . 2-20 |

| 2.5.1   | Memory Mapping Registers         | . 2-20 |

| 2.5.2   | Bank Selection                   | . 2-20 |

| 2.6     | Addressing                       | . 2-22 |

| 2.6.1   | Memory Map                       | . 2-22 |

| 2.6.2   | Register Map                     | . 2-23 |

| 2.6.3   | Mailboxes                                      | . 2-24         |

|---------|------------------------------------------------|----------------|

| 2.7     | Cache Memory                                   | . 2-27         |

| 2.7.1   | Cache States                                   |                |

| 2.7.2   | Cache State Changes                            | . 2-28         |

| 2.7.2.1 | Processor Actions                              | . 2-28         |

| 2.7.2.2 | Bus Actions                                    | . 2-29         |

| 2.7.2.3 | Write Operations                               |                |

| 2.8     | Registers                                      |                |

|         | LDEV — Device Register                         |                |

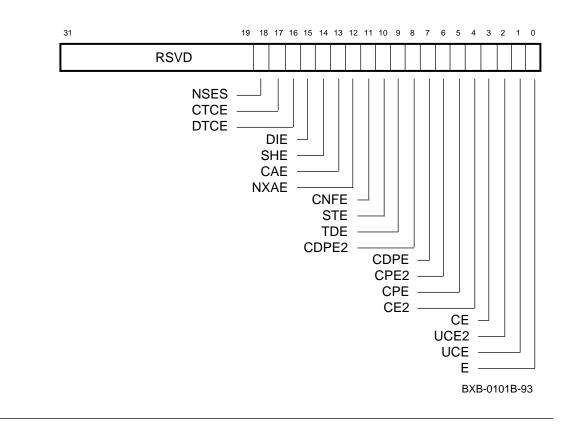

|         | LBER — Bus Error Register                      |                |

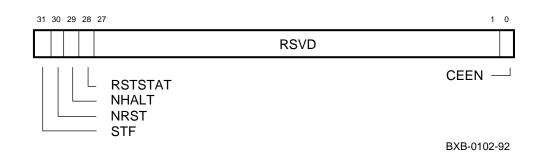

|         | LCNR — Configuration Register                  |                |

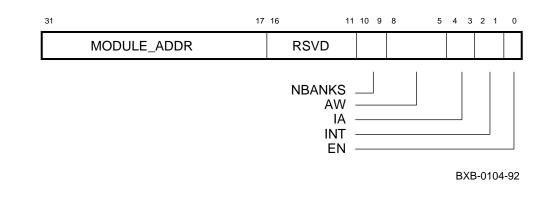

|         | LMMR0-7 — Memory Mapping Registers             |                |

|         | LBESR0–3 — Bus Error Syndrome Registers        |                |

|         | LBECR0, 1 — Bus Error Command Registers        |                |

|         | LILID0–3 — Interrupt Level 0–3 IDENT Registers |                |

|         | LCPUMASK — CPU Interrupt Mask Register         |                |

|         | LMBPR0–3 — Mailbox Pointer Registers           |                |

|         | LIOINTR — I/O Interrupt Register               |                |

|         | LIPINTR — Interprocessor Interrupt Register    |                |

| 2.9     | Console and Initialization                     |                |

| 2.9.1   | Console Lines                                  |                |

| 2.9.1.1 | Console Terminal Lines                         |                |

| 2.9.1.2 | RUN                                            |                |

| 2.9.1.3 | CONWIN                                         |                |

| 2.9.1.4 | EXP and SEL                                    |                |

| 2.9.1.5 | SECURE                                         |                |

| 2.9.1.6 | PIU Power Monitoring                           |                |

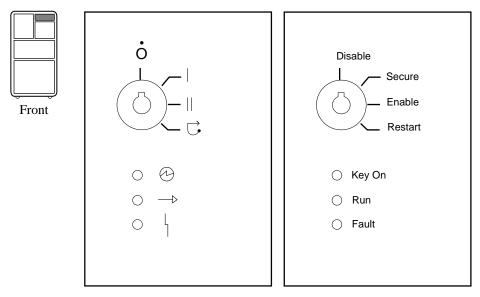

| 2.9.2   | Control Panel Controls and Indicators          |                |

| 2.9.3   | Initialization Mechanisms                      |                |

| 2.9.3.1 | Power-Up                                       |                |

| 2.9.3.2 | Power Failure                                  |                |

| 2.9.3.3 | System Reset                                   |                |

| 2.9.3.4 | Node Reset                                     |                |

| 2.9.4   | Self-Test                                      |                |

| 2.9.5   | Module Regulator Failure                       |                |

| 2.10    | Errors                                         |                |

| 2.10.1  | ECC Errors                                     |                |

| 2.10.1  | Parity Errors During C/A Cycles                |                |

| 2.10.2  | Parity Errors During CSR Data Cycles           |                |

| 2.10.3  | Double Errors                                  |                |

| 2.10.5  | Transmitter During Error                       |                |

| 2.10.6  | STALL Errors                                   |                |

| 2.10.7  | CNF Errors                                     |                |

| 2.10.7  | Nonexistent Address Errors                     |                |

| 2.10.8  | CA Errors                                      |                |

| 2.10.5  | SHARED Errors                                  |                |

| 2.10.10 | DIRTY Errors                                   |                |

| 2.10.11 | Data Transmit Check Errors                     |                |

| 2.10.12 | Control Transmit Check Errors                  |                |

| 2.10.13 | Node-Specific Error Summary                    |                |

| 2.10.14 | Monitoring ERR                                 |                |

| 2.10.15 | LSB Error Recovery                             |                |

| w.10.10 |                                                | . <i>⊷</i> -J0 |

# Chapter 3 Power, Cabinet Control, and Cooling Systems

| 3.1   | Power System               |  |

|-------|----------------------------|--|

| 3.1.1 | AC Input Box               |  |

| 3.1.2 | DC Distribution Box        |  |

| 3.1.3 | Power Regulator            |  |

| 3.1.4 | Uninterrupted Power Supply |  |

| 3.1.5 | Module Regulators          |  |

| 3.1.6 | 48V DC Bus                 |  |

| 3.2   | Cabinet Control System     |  |

| 3.2.1 | CCL Power Source           |  |

| 3.2.2 | Cabinet Serial Lines       |  |

| 3.2.3 | Power Sequencing           |  |

| 3.2.4 | Power Fail Operation       |  |

| 3.3   | Cooling System             |  |

|       |                            |  |

# Appendix A CCL Cables

# Appendix B EPU Calculations

# Figures

| 1-1  | LSB Card Cage                              | 1-4  |

|------|--------------------------------------------|------|

| 1-2  | Power System – DEC 7000/VAX 7000 Systems   | 1-5  |

| 1-3  | Power System — DEC 10000/VAX 10000 Systems | 1-6  |

| 1-4  | Cooling System Blower                      |      |

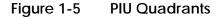

| 1-5  | PIU Quadrants                              |      |

| 2-1  | System Block Diagram                       |      |

| 2-2  | Command Cycle Format                       |      |

| 2-3  | Data Wrapping                              | 2-12 |

| 2-4  | LSB ECC Coding                             |      |

| 2-5  | Single Transaction Timing                  | 2-15 |

| 2-6  | Interleaved Transaction Timing (Best Case) | 2-15 |

| 2-7  | Simple STALL Timing                        | 2-17 |

| 2-8  | CSR Transaction Timing                     |      |

| 2-9  | Single STALL in Interleaved Transactions   | 2-17 |

| 2-10 | Best-Case Interleaved Transaction Timing   | 2-18 |

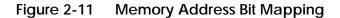

| 2-11 | Memory Address Bit Mapping                 | 2-22 |

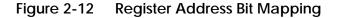

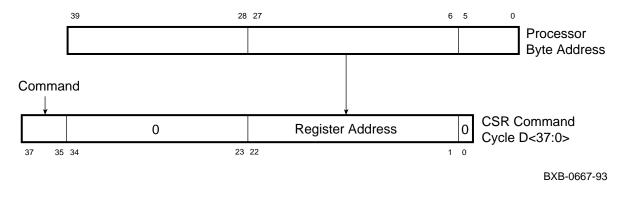

| 2-12 | Register Address Bit Mapping               | 2-22 |

| 2-13 | Wrapping of LSB Data                       | 2-23 |

| 2-14 | Register Address Map                       | 2-24 |

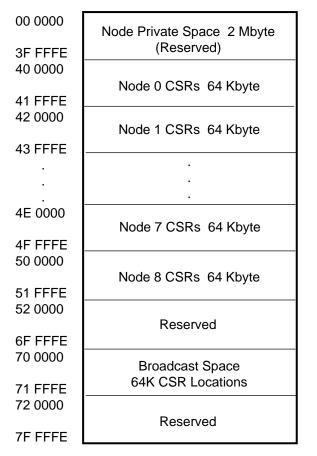

| 2-15 | Mailbox Data Structure                     | 2-25 |

| 2-16 | Control Panel                              | 2-51 |

| 3-1  | Airflow in System and Expander Cabinets    | 3-8  |

# Tables

| 1   | Operators Used in Code Fragments                | ix  |

|-----|-------------------------------------------------|-----|

|     | DEC 7000/10000 and VAX 7000/10000 Documentation |     |

| 3   | Related Documents                               | xi  |

| 1-1 | DEC 7000/VAX 7000 Cabinets                      | 1-2 |

|     |                                                 |     |

| 1-2  | DEC 10000/VAX 10000 Cabinets                             | . 1-2 |

|------|----------------------------------------------------------|-------|

| 1-3  | Cabinet Components                                       | . 1-3 |

| 1-4  | PIU Quadrant Restrictions                                | . 1-8 |

| 2-1  | LSB Node Identification                                  | . 2-4 |

| 2-2  | LSB Signal Types                                         | . 2-4 |

| 2-3  | LSB Signals                                              |       |

| 2-4  | PRIO Values After RESET                                  |       |

| 2-5  | Command Field                                            |       |

| 2-6  | Correspondence of Data Longwords to ECC Fields           |       |

| 2-7  | Bank Number as a Function of Interleave                  |       |

| 2-8  | LSB Node Base Addresses                                  |       |

| 2-9  | Mailbox Data Structure Format                            |       |

| 2-10 | Cache States                                             |       |

| 2-11 | Result of Processor Actions on Cache Line                |       |

| 2-12 | Result of Bus Actions on Cache Line                      |       |

| 2-13 | Register Bit Types                                       |       |

| 2-14 | LSB Registers                                            |       |

| 2-15 | LDEV Register Bit Definitions                            |       |

| 2-16 | LBER Register Bit Definitions                            |       |

| 2-17 | LCNR Register Bit Definitions                            |       |

| 2-18 | LMMR Register Bit Definitions                            |       |

| 2-19 | LBESR Register Bit Definitions                           |       |

| 2-20 | Syndromes for Single-Bit Errors                          |       |

| 2-21 | LBECR Register Bit Definitions                           |       |

| 2-22 | LILID Register Bit Definitions                           |       |

| 2-23 | LCPUMASK Register Bit Definitions                        |       |

| 2-24 | LMBPR0–3 Register Bit Definitions                        |       |

| 2-25 | LIOINTR Register Bit Definitions                         |       |

| 2-26 | LIPINTR Register Bit Definitions                         |       |

| 2-27 | EXP and SEL Coding                                       |       |

| 2-28 | Control Panel Keyswitch Positions                        |       |

| 2-29 | Control Panel Indicator Lights                           |       |

| 2-30 | Fault Matrix for Module Regulators                       |       |

| 3-1  | Equivalent Power Units — LSB and Cabinet                 |       |

| 3-2  | Equivalent Power Units — Plug-In Units                   |       |

| 3-3  | Input and Output Characteristics of the Module Regulator |       |

| A-1  | Cable Descriptions                                       |       |

| A-2  | CCL to LSB Cable                                         |       |

| A-3  | CCL to Control Panel Cable                               |       |

| A-4  | CCL to DC Distribution Box Cable                         |       |

| A-5  | CCL to Plug-in Unit Cable                                |       |

| A-6  | CCL to Blower Cable                                      |       |

| A-7  | CCL to Removable Media Cable                             |       |

| B-1  | Calculation of Equivalent Power Units — LSB and Cabinet  |       |

| B-2  | Calculation of Equivalent Power Units — Plug-In Units    |       |

| B-3  | Voltages of Options in Plug-In Units                     |       |

# **Intended Audience**

This manual is a reference for Digital service engineers. It describes the platform architecture, the LSB bus, and the power, cabinet control, and cooling systems of the DEC 7000 AXP, DEC 10000 AXP, VAX 7000, and VAX 10000 systems.

# **Document Structure**

This manual has three chapters and two appendixes, as follows:

- **Chapter 1, Platform Overview,** gives you a brief description of the system platform.

- Chapter 2, LSB Bus, provides information on the system bus.

- **Chapter 3, Power, Cabinet Control, and Cooling Systems,** describes these platform systems.

- The **Appendixes** give in-depth information on topics covered in the manual. Appendix A describes the cabinet control system cables. Appendix B provides information on system power requirements.

# **Conventions Used in This Document**

*Terminology.* Unless specified otherwise, the use of "system" refers to either a DEC 7000 AXP or VAX 7000 system. The DEC 7000 AXP systems use the Alpha AXP architecture. References in text use DEC 7000 to refer to DEC 7000 AXP systems.

*Book titles.* In text, if a book is cited without a product name, that book is part of the hardware documentation. It is listed in Table 2 along with its order number.

*Icons.* The icons shown below are used in illustrations for designating part placement in the system described. A shaded area in the icon shows the location of the component or part being discussed.

*Addresses.* All addresses in this document are specified in hexadecimal values, unless otherwise indicated.

*Coding conventions.* The LSB description in Chapter 2 uses code fragments to describe the operation of several aspects of the LSB architecture. The following conventions are observed:

- The letters B and C are used to represent arbitrary cycles in time. The text accompanying the code typically indicates whether the cycle is arbitrary or of a specific type (for example, a command cycle).

- For scalar signals, bit subscripts are used to indicate the value of the signal in other cycles relative to the reference cycle. For example, STALL<C-2> refers to the value of the STALL signal two cycles before cycle C.

- For vector signals, word subscripts are used to indicate the value of the signal in other cycles relative to the reference cycle. For example, REQ[C-2]<5:0> refers to the value of REQ<5:0> two cycles before cycle C.

Table 1 lists the operators used in the code fragments along with their meanings.

# Table 1 Operators Used in Code Fragments

| Operator    | Result                                                                                                                         |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|

| AND         | Bitwise AND                                                                                                                    |

| AND (unary) | AND of all bits in operand                                                                                                     |

| EQL         | Equal — 1 if operands are equal                                                                                                |

| GEQ         | Greater-than-or-equal — 1 if operand 1 is greater than or equal to operand 2                                                   |

| GTR         | Greater-than — 1 if operand 1 is greater than operand 2 $$                                                                     |

| NOT (unary) | Bitwise inverse                                                                                                                |

| OR          | Bitwise OR                                                                                                                     |

| OR (unary)  | OR of all bits in operand                                                                                                      |

| SL0         | Shift left and fill with zeros — shift operand 1 left<br>by the number of bits specified by operand 2 and<br>fill with zeros   |

| SL1         | Shift left and fill with ones — shift operand 1 left<br>by the number of bits specified by operand 2 and<br>fill with ones     |

| SR0         | Shift right and fill with zeros — shift operand 1<br>right by the number of bits specified by operand 2<br>and fill with zeros |

| SR1         | Shift right and fill with ones — shift operand 1<br>right by the number of bits specified by operand 2<br>and fill with ones   |

| SXT         | Sign extend — extend by replicating the most sig-<br>nificant bit                                                              |

| XOR         | Bitwise exclusive OR                                                                                                           |

| &           | Concatenate — operand 1 is the most significant bits; operand 2 is the least significant bits                                  |

| #           | Indicates base of operand; for example, 0001#2 is a binary operand                                                             |

| <>          | Encloses bit subscripts                                                                                                        |

| 0           | Encloses word subscript                                                                                                        |

# **Documentation Titles**

Table 2 lists the books in the DEC 7000/10000 and VAX 7000/10000 documentation sets. Table 3 lists other documents that you may find useful.

Table 2 DEC 7000/10000 and VAX 7000/10000 Documentation

| Title                                           | 7000 Systems<br>Order Number | 10000 Systems<br>Order Number |

|-------------------------------------------------|------------------------------|-------------------------------|

| Installation Kit                                | EK-7000B-DK                  | EK-1000B-DK                   |

| Site Preparation Guide                          | EK-7000B-SP                  | EK-1000B-SP                   |

| Installation Guide                              | EK-700EB-IN                  | EK-100EB-IN                   |

| Hardware User Information Kit                   | EK-7001B-DK                  | EK-1001B-DK                   |

| Operations Manual                               | EK-7000B-OP                  | EK-1000B-OP                   |

| Basic Troubleshooting                           | EK-7000B-TS                  | EK-1000B-TS                   |

| Service Information Kit—VAX 7000                | EK-7002A-DK                  | EK-1002A-DK                   |

| Platform Service Manual                         | EK-7000A-SV                  | EK-1000A-SV                   |

| System Service Manual                           | EK-7002A-SV                  | EK-1002A-SV                   |

| Pocket Service Guide                            | EK-7000A-PG                  | EK-1000A-PG                   |

| Advanced Troubleshooting                        | EK-7001A-TS                  | EK-1001A-TS                   |

| Service Information Kit—DEC 7000                | EK-7002B-DK                  | EK-1002B-DK                   |

| Platform Service Manual                         | EK-7000A-SV                  | EK-1000A-SV                   |

| System Service Manual                           | EK-7002B-SV                  | EK-1002B-SV                   |

| Pocket Service Guide                            | EK-7700A-PG                  | EK-1100A-PG                   |

| Advanced Troubleshooting                        | EK-7701A-TS                  | EK-1101A-TS                   |

| Reference Manuals                               |                              |                               |

| Console Reference Manual                        | EK-70C0B-TM                  |                               |

| KA7AA CPU Technical Manual                      | EK-KA7AA-TM                  |                               |

| KN7AA CPU Technical Manual                      | EK-KN7AA-TM                  |                               |

| MS7AA Memory Technical Manual                   | EK-MS7AA-TM                  |                               |

| I/O System Technical Manual                     | EK-70I0A-TM                  |                               |

| Platform Technical Manual                       | EK-7000A-TM                  |                               |

| Upgrade Manuals                                 |                              |                               |

| KA7AA CPU Installation Card                     | EK-KA7AA-IN                  |                               |

| KN7AA CPU Installation Card                     | EK-KN7AA-IN                  |                               |

| MS7AA Memory Installation Card                  | EK-MS7AA-IN                  |                               |

| KZMSA Adapter Installation Guide                | EK-KXMSX-IN                  |                               |

| DWLAA Futurebus+ PIU Installation Guide         | EK-DWLAA-IN                  |                               |

| DWLMA XMI PIU Installation Guide                | EK-DWLMA-IN                  |                               |

| DWMBB VAXBI Installation Guide                  | EK-DWMBB-IN                  |                               |

| H7237 Battery PIU Installation Guide            | EK-H7237-IN                  |                               |

| H7263 Power Regulator Installation Card         | EK-H7263-IN                  |                               |

| BA654 DSSI Disk PIU Installation Guide          | EK-BA654-IN                  |                               |

| BA655 SCSI Disk and Tape PIU Installation Guide | EK-BA655-IN                  |                               |

| Removable Media Installation Guide              | EK-TFRRD-IN                  |                               |

# Table 3 Related Documents

| Title                                                                          | Order Number |

|--------------------------------------------------------------------------------|--------------|

| General Site Preparation                                                       |              |

| Site Environmental Preparation Guide                                           | EK-CSEPG-MA  |

| System I/O Options                                                             |              |

| BA350 Modular Storage Shelf Subsystem Configuration Guide                      | EK-BA350-CG  |

| BA350 Modular Storage Shelf Subsystem User's Guide                             | EK-BA350-UG  |

| BA350-LA Modular Storage Shelf User's Guide                                    | EK-350LA-UG  |

| CIXCD Interface User Guide                                                     | EK-CIXCD-UG  |

| DEC FDDIcontroller 400 Installation/Problem Solving                            | EK-DEMFA-IP  |

| DEC LANcontroller 400 Installation Guide                                       | EK-DEMNA-IN  |

| DEC LANcontroller 400 Technical Manual                                         | EK-DEMNA-TM  |

| DSSI VAXcluster Installation and Troubleshooting Manual                        | EK-410AA-MG  |

| InfoServer 150 Installation and Owner's Guide                                  | EK-INFSV-OM  |

| KDM70 Controller User Guide                                                    | EK-KDM70-UG  |

| KFMSA Module Installation and User Manual                                      | EK-KFMSA-IM  |

| KFMSA Module Service Guide                                                     | EK-KFMSA-SV  |

| RRD42 Disc Drive Owner's Manual                                                | EK-RRD42-OM  |

| RF Series Integrated Storage Element User Guide                                | EK-RF72D-UG  |

| TF85 Cartridge Tape Subsystem Owner's Manual                                   | EK-OTF85-OM  |

| TLZ06 Cassette Tape Drive Owner's Manual                                       | EK-TLZ06-OM  |

| Operating System Manuals                                                       |              |

| Alpha Architecture Reference Manual                                            | EY-L520E-DP  |

| DEC OSF/1 Guide to System Administration                                       | AA-PJU7A-TE  |

| DECnet for OpenVMS Network Management Utilities                                | AA-PQYAA-TK  |

| Guide to Installing DEC OSF/1                                                  | AA-PS2DA-TE  |

| OpenVMS Alpha Version 1.5 Upgrade and Installation Manual                      | AA-PQYSB-TE  |

| VMS Upgrade and Installation Supplement: VAX 7000–600 and VAX 10000–600 Series | AA-PRAHA-TE  |

| VMS Network Control Program Manual                                             | AA-LA50A-TE  |

| VMSclusters and Networking                                                     |              |

| HSC Installation Manual                                                        | EK-HSCMN-IN  |

| SC008 Star Coupler User's Guide                                                | EK-SC008-UG  |

| VAX Volume Shadowing Manual                                                    | AA-PBTVA-TE  |

| Peripherals                                                                    |              |

| Installing and Using the VT420 Video Terminal                                  | EK-VT420-UG  |

| LA75 Companion Printer Installation and User Guide                             | EK-LA75X-UG  |

# **Chapter 1**

# **Platform Overview**

This chapter provides an overview of the power and packaging for DEC 7000/10000 and VAX 7000/10000 systems. The following sections are included in this chapter:

- DEC 7000/VAX 7000 Cabinets

- DEC 10000/VAX 10000 Cabinets

- Cabinet Components

- LSB Card Cage

- Power, Cabinet Control, and Cooling Systems

- Plug-In Units

# 1.1 DEC 7000/VAX 7000 Cabinets

The DEC 7000/VAX 7000 cabinet variants are listed in Table 1-1.

#### Table 1-1 DEC 7000/VAX 7000 Cabinets

| Number   | Description                        |

|----------|------------------------------------|

| H9F00–AA | System cabinet, 120/208 V, 60 Hz   |

| H9F00–AB | System cabinet, 380–415 V, 50 Hz   |

| H9F00–AC | System cabinet, 202 V, 50–60 Hz    |

| H9F00–BA | Expander cabinet, 120/208 V, 60 Hz |

| H9F00–BB | Expander cabinet, 380–415 V, 50 Hz |

| H9F00–BC | Expander cabinet, 202 V, 50–60 Hz  |

The system cabinet contains an LSB card cage, power system, cabinet control system, cooling system, and plug-in units. The expander cabinet contains the same components less the LSB card cage. A DEC 7000/VAX 7000 system can consist of a system cabinet alone or a system cabinet with one or two expander cabinets.

# 1.2 DEC 10000/VAX 10000 Cabinets

The DEC 10000/VAX 10000 cabinet variants are listed in Table 1-2.

## Table 1-2 DEC 10000/VAX 10000 Cabinets

| ·        |                                    |

|----------|------------------------------------|

| Number   | Description                        |

| H9F00–CA | System cabinet, 120/208 V, 60 Hz   |

| H9F00–CB | System cabinet, 380–415 V, 50 Hz   |

| H9F00–CC | System cabinet, 202 V, 50–60 Hz    |

| H9F00–DA | Expander cabinet, 120/208 V, 60 Hz |

| H9F00–DB | Expander cabinet, 380–415 V, 50 Hz |

| H9F00–DC | Expander cabinet, 202 V, 50–60 Hz  |

| H9F00-AE | Battery cabinet, left              |

| H9F00–AF | Battery cabinet, right             |

|          |                                    |

The system cabinet contains an LSB card cage, power system, cabinet control system, cooling system, and battery plug-in units. The expander cabinet contains a power system, cabinet control system, cooling system, I/O plug-in units, and disk plug-in units. The battery cabinet contains battery plug-in units for the expander cabinet. A minimum DEC 10000/VAX 10000 system consists of the system cabinet, one expander cabinet, and one battery cabinet. A second expander cabinet and battery cabinet can be added.

# 1.3 Cabinet Components

Table 1-3 lists the cabinet components that are described in this manual.

# Table 1-3 Cabinet Components

| Component                | Description                                                                                                                                                                      |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSB                      | System bus and centerplane enclosure in which the processor, memory, and I/O port modules reside.                                                                                |

| DC distribu-<br>tion box | Connects the AC service line, 48V DC power regula-<br>tors, uninterruptible power supply batteries, and the<br>cabinet control logic module.                                     |

| Power regula-<br>tors    | Generate 48V DC from the AC line or from a 48V bat-<br>tery power source.                                                                                                        |

| Plug-in units            | Contain I/O buses, disk and tape storage, or batteries.                                                                                                                          |

| Control panel            | Provides indicators and switches for controlling and<br>monitoring cabinet operation. It also provides the ca-<br>ble connection for the console device. System cabinet<br>only. |

| Cabinet control<br>logic | Contains the logic to operate the power and cooling<br>systems. Each system and expander cabinet has a<br>cabinet control logic (CCL) module.                                    |

| Blower                   | Cooling airflow for the cabinet.                                                                                                                                                 |

# 1.4 LSB Card Cage

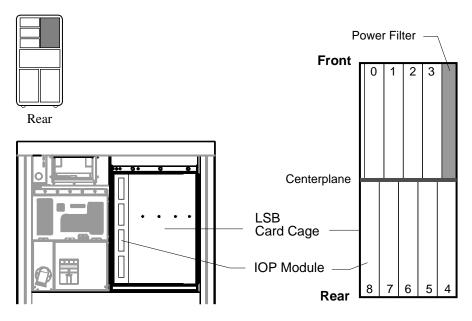

The LSB card cage, shown in Figure 1-1, has nine slots grouped around a centerplane. One slot is dedicated to the IOP module; the other eight slots hold processor, memory, or filler modules. The LSB bus is described in Chapter 2.

# Figure 1-1 LSB Card Cage

BXB-0055C-93

# 1.5 Power, Cabinet Control, and Cooling Systems

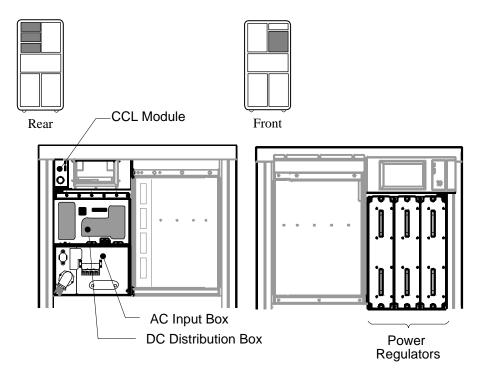

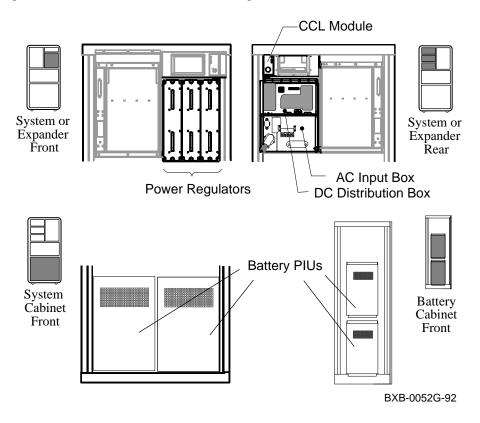

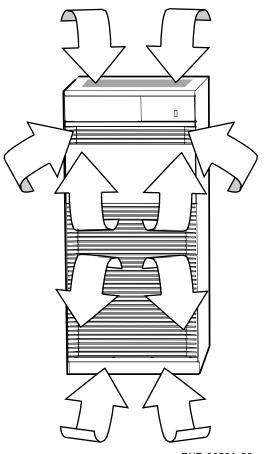

The power, cabinet control, and cooling systems are identical in the system and expander cabinets. The power system consists of an AC input box, a DC distribution box, one or more power regulators, the cabinet control logic (CCL) module, and batteries (optional in DEC 7000/VAX 7000 systems; included in DEC 10000/VAX 10000 systems). The power system is shown in Figures 1-2 and 1-3. The cooling system consists of a blower and the cabinet control logic module. The blower is shown in Figure 1-4. The power, cabinet control, and cooling systems are described in Chapter 3.

## Figure 1-2 Power System — DEC 7000/VAX 7000 Systems

BXB-0052-92

# Figure 1-3 Power System – DEC 10000/VAX 10000 Systems

# Figure 1-4 Cooling System Blower

BXB-0022C-92

# 1.6 Plug-In Units

I/O buses, disks, and batteries are housed in the system and expander cabinets in plug-in units (PIUs). PIU quadrants are designated for specific types of PIUs; the location of these quadrants is shown in Figure 1-5. The PIUs that may be located in each quadrant are listed in Table 1-4.

# Table 1-4 PIU Quadrant Restrictions

| PIU                | Quadrant              | Restrictions                                                                                              |

|--------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|

| XMI                | 1 and 2 or<br>3 and 4 | If a VAXBI is connected, the XMI<br>PIU must be in quadrants 1 and 2.<br>Requires two PIU quadrants.      |

| Futurebus+         | 2 or 4                | Must be in the rear of the cabinet.<br>Requires one PIU quadrant.                                         |

| VAXBI              | 3 and 4               | Must be in the same cabinet as the<br>XMI to which it is connected.<br>Requires two PIU quadrants.        |

| DSSI disk          | Any                   | For proper airflow, arrow on rear<br>panel must point toward blower.<br>Requires one PIU quadrant.        |

| SCSI disk and tape | Any                   | For proper airflow, arrow on rear<br>panel must point toward blower.<br>Requires one PIU quadrant.        |

| Battery            | 1 and 2 or<br>3 and 4 | In DEC 7000/VAX 7000 systems,<br>can be located in quadrants 3 and 4<br>only. Requires two PIU quadrants. |

# Chapter 2

# LSB Bus

The LSB is the system bus for the DEC 7000/10000 and VAX 7000/10000 systems. The LSB bus is defined by the protocol that a node on the bus must follow, the electrical environment of the bus, the backplane, and the logic used to implement the protocol.

This chapter describes the LSB bus and includes these sections:

- Overview

- Arbitration

- Bus Cycles

- Bus Transactions

- Memory Bank Mapping

- Addressing

- Cache Memory

- Registers

- Console and Initialization

- Errors

# 2.1 Overview

The LSB is a limited length, nonpended, synchronous bus. It is 128 bits wide and uses distributed arbitration.

All transactions on the LSB bus occur in a set of fixed cycles relative to an arbitration cycle, and as many as three transactions can be in progress at one time. To accomplish this, the bus arbitrates on a dedicated set of control signals; arbitration may be overlapped with data transfer. Data and address are multiplexed on the same set of signals.

The LSB protocol supports writeback caches.

### 2.1.1 LSB Bus Specifications

| Memory transfer length | 64 bytes       |

|------------------------|----------------|

| Data path width        | 128 bits       |

| Bus cycle time         | 20 ns          |

| Usable bandwidth       | 640 Mbytes/sec |

A node on the LSB is a module. The LSB can support from one to six processor nodes, one to seven memory nodes, and a single I/O port node, which is the interface to I/O plug-in units.

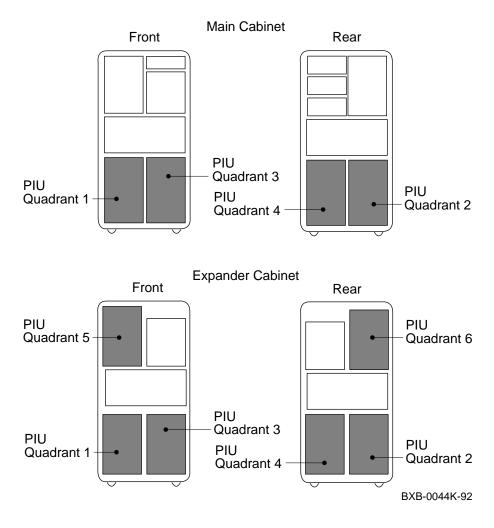

A block diagram of a typical system using the LSB is shown in Figure 2-1.

## Figure 2-1 System Block Diagram

### 2.1.2 Module Identification

The LSB bus has slots for nine nodes. These nodes are identified in Table 2-1. Each processor or memory module receives NID<2:0> on its backplane connector to identify its slot. The NID<2:0> signals are selectively connected to GND on the backplane to identify the slot, as specified in Table 2-1.

The I/O port module is always node 8. It occupies a special slot in the backplane that is physically incompatible with the other slots. Since it always occupies the same slot, it does not need NID signals to determine its node number.

| Table 2-1 LSB Node Identification |

|-----------------------------------|

|-----------------------------------|

| Node Number | Module              | NID<2>         | NID<1>         | NID<0>         |

|-------------|---------------------|----------------|----------------|----------------|

| 0           | Processor or memory | Open           | Open           | Open           |

| 1           | Processor or memory | Open           | Open           | GND            |

| 2           | Processor or memory | Open           | GND            | Open           |

| 3           | Processor or memory | Open           | GND            | GND            |

| 4           | Processor or memory | GND            | Open           | Open           |

| 5           | Processor or memory | GND            | Open           | GND            |

| 6           | Processor or memory | GND            | GND            | Open           |

| 7           | Processor or memory | GND            | GND            | GND            |

| 8           | I/O port            | Not applicable | Not applicable | Not applicable |

# 2.1.3 Signals

All LSB data and control signals are implemented in negative logic. Signals are asserted low; that is, when a signal is asserted (TRUE or 1), the open drain driver pulls the line low. In the absence of an assertion, the bus terminator pulls the line high, so the signal is deasserted (FALSE or 0).

## Table 2-2 LSB Signal Types

| Туре  | Description                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OD    | Open drain – May be driven by one or more modules. If not driven, the wire de-<br>faults to a deasserted level.                                                     |

| CLK   | Clock – Input only. It is driven from outside the LSB environment.                                                                                                  |

| STRAP | Selectively connected to GND on the backplane to provide slot identification to the module.                                                                         |

| TTL   | Standard TTL level signal that is driven by logic external to the LSB environment.                                                                                  |

| OC    | Open collector – Standard TTL level signal that may be driven by one or more modules. The pullup is supplied by logic external to the LSB environment (CCL module). |

| Signal       | Wires | Туре  | Description                           |

|--------------|-------|-------|---------------------------------------|

| D<127:0>     | 128   | OD    | Data and command/address <sup>1</sup> |

| ECC<27:0>    | 28    | OD    | Error correction for data cycles      |

| REQ<9:0>     | 10    | OD    | Arbitration request                   |

| STALL        | 1     | OD    | Responder stall                       |

| ERR          | 1     | OD    | Error detected by any module          |

| SHARED       | 1     | OD    | Data is cached                        |

| DIRTY        | 1     | OD    | Memory data is stale                  |

| CNF          | 1     | OD    | Responder confirmation                |

| CA           | 1     | OD    | Command/address cycle                 |

| LOCKOUT      | 1     | OD    | Lock out new requests                 |

| CRD          | 1     | OD    | Corrected read data                   |

| PH0          | 1     | CLK   | Clock phase 0 (sine) <sup>2</sup>     |

| PH90         | 1     | CLK   | Clock phase 90 (cosine) <sup>2</sup>  |

| NID<2:0>     | 3     | STRAP | Slot identification <sup>3</sup>      |

| LSB_RESET    | 1     | OC    | Reset everything                      |

| CCL_RESET    | 1     | OC    | Initiate reset sequence               |

| BAD          | 1     | OC    | Self-test not successful              |

| LOCTX        | 1     | OC    | Local console terminal transmit       |

| LOCRX        | 1     | TTL   | Local console terminal receive        |

| PSTX         | 1     | OC    | Power supply status transmit          |

| PSRX         | 1     | TTL   | Power supply status receive           |

| EXP_SEL      | 2     | OC    | Expander select                       |

| SECURE       | 1     | OC    | Secure console                        |

| LDC PWR OK   | 1     | TTL   | Local disk converter OK               |

| PIU MOD A OK | 1     | TTL   | Plug-in unit module A OK              |

| PIU MOD B OK | 1     | TTL   | Plug-in unit module B OK              |

| RUN          | 1     | OC    | System run indicator                  |

| CONWIN       | 1     | OC    | Console win status                    |

|              |       |       |                                       |

# Table 2-3 LSB Signals

$^1$  Only D<38:0> are used during command cycles and CSR data cycles.

<sup>2</sup> Separate copies of the PH0 and PH90 signals are distributed to each module.

$^3$  NID<2:0> are hardwired on the backplane to provide an individual code for each slot.

# 2.2 Arbitration

The LSB bus uses a distributed arbitration scheme. Processor modules and the IOP module use ten signals, REQ<9:0>, to request the bus. All nodes independently monitor these lines to determine whether a transaction has been requested, and if so, which node wins the right to send a command cycle to start the transaction. The arbitration process ensures that transactions start only at specified times, and that only one node starts a transaction in any cycle. If the bus is idle, a request may be initiated in any cycle. If a transaction is in progress, requests may be made only during every fifth cycle to guarantee that new transactions do not interfere with transactions already in progress.

Arbitration control is pipelined. The arbitration sequence is:

- 1. A node places an arbitration request by asserting a REQ line.

- 2. All bus nodes determine which node won the arbitration. Because of the pipelining, other nodes may request the bus during this cycle, but these additional REQ assertions are ignored.

- 3. The winner of the bus arbitration may start a transaction.

#### 2.2.1 Signals Used in Arbitration

Arbitration is controlled by these signals:

- REQ<9:0>

- CA

- STALL

- ERR

- RESET

REQ<5> is the highest priority request, and REQ<0> is the lowest. REQ<5> and REQ<0> are allocated to the IOP module. REQ<4:1> and REQ<9:6> are allocated to processor modules. The REQ<9:6,4:1> lines are dynamically reallocated among the processor modules using a leastrecently-granted algorithm (see Section 2.2.5).

The CA, STALL, and ERR signals also influence arbitration. The arbitration logic monitors these signals to ensure that a new transaction is not started when it could result in cycle overlaps with transactions still in progress. The RESET signal sets priority to the default (power-up) state.

#### 2.2.2 Arbitration Request Process

Nodes can request the bus during any cycle when it is idle or during every fifth cycle when it is in use. To request the bus, a module asserts its assigned REQ line. This section describes an algorithm for determining when a module is permitted to assert its REQ line.

Each node implements an allocation mask, ALLOC<16:0>, that indicates which future cycles are not available for command cycles. This mask is updated to track the allocation of cycles to existing and new transactions, and to account for stalls (STALL cycle) and errors (ERR signal). The higher numbered bits of ALLOC<16:0> represent the cycles farthest into the future.

ALLOC<16:0> is updated at the end of each cycle B using the following formula<sup>1</sup>:

```

ALLOC<16:0>=(ALLOC<16:0> SR0 (NOT STALL<B-2>)) OR !SHIFT

((SXT CA<B-1>) AND (00011110111101111#2

SL0 STALL<B-2>)) OR !ALLOCATE

((SXT (ERR<B-1> OR RESET<B-1>)) AND 111111111111111112);

!RESET

```

This equation shifts the allocation mask right on each non-STALL cycle, sets some of the mask bits during each command cycle, and sets all the mask bits when ERR is asserted.

A module may assert its assigned REQ<sup>2</sup> signal in any cycle C if the following conditions are met:

| ASSERT_REQUEST <c> =</c>         |                                    |

|----------------------------------|------------------------------------|

| MODULE_REQUEST AND               |                                    |

| (CA <c-3> OR</c-3>               | ! (ignore REQ in CA cycle)         |

| (REQ[C-3]<9:0> EQL 0))           | AND ! no prior request             |

| (REQ[C-2]<9:0> EQL 0)            | AND ! no prior request             |

| (NOT CA <c-2>)</c-2>             | AND ! no prior request             |

| (NOT ASSERT_REQUEST <c-1>)</c-1> | AND ! don't do it twice            |

| (NOT ALLOC[C]<2>)                | AND ! sync with prev. transactions |

| BANK_PERMITTED;                  | ! if mem bank is idle              |

REQ[C-3], REQ[C-2], CA<C-2>, and ASSERT\_REQUEST<C-1> block the request, to assure that no additional requests are issued after the first request on an idle bus. (Due to the bus control pipelining, one additional request may occur in the cycle after the first request on an idle bus. The protocol for arbitration grant assures that this request is ignored.) ALLOC is monitored to synchronize requests with bus transactions that are already in progress.

The BANK\_PERMITTED condition assures that the cache block to be referenced does not match that of any other transactions currently in progress. (The computation of BANK\_PERMITTED is explained in Section 2.2.6.)

## 2.2.3 Arbitration Grant Process

When a node wins arbitration, it asserts CA and drives a command on the bus two cycles after it requests the bus. (The module also drives its node ID onto REQ<3:0> to facilitate bus monitoring.)

Specifically, a module may assert CA and drive a command on D<38:0> during any cycle C if the following conditions are met:

ARB\_WIN is detected in the module that has asserted the highestnumbered REQ signal during cycle C-2.

REQ[C-3], CA<C-2>, CA<C-3>, and CA<C-4> block the grant, to assure that no additional command cycles are issued immediately after the first-

<sup>&</sup>lt;sup>1</sup> See page viii for information about coding conventions.

<sup>&</sup>lt;sup>2</sup> REQ<3:0> are also asserted during command cycles to facilitate bus monitoring. These equations describe only the REQ assertions used for arbitration.

command cycle on an idle bus, and to minimize the likelihood of bus collisions in the presence of arbitration-related failure modes.

#### 2.2.4 Recognizing Command Cycles

Each node monitors the bus for command cycles. A module must interpret any cycle C as a command cycle if the following conditions are met:

```

COMMAND_DETECTED<C> = CA<C>AND

(REQ[C-2]<9:0> GTR 0) AND

(NOT CA<C-1>) AND

(NOT CA<C-2>) AND

(NOT CA<C-2>) AND

(NOT CA<C-3>) AND

(NOT CA<C-4>);

VALID_COMMAND_DETECTED<C> = COMMAND_DETECTED<C> AND

(XOR D[C]<38:0>)

```

Assertion of the CA signal indicates the presence of a command cycle. The state of REQ and CA during prior cycles is monitored to minimize the like-lihood of bus collisions in the presence of arbitration-related failures.

A command cycle is recognized only if odd parity is observed over D<38:0> during the command cycle. If a parity error occurs during the command cycle, the command cycle is ignored.

### 2.2.5 Processor Arbitration Scheme

All processor modules share the use of REQ<9:6,4:1>. Each of these signals is assigned to only one processor module. (If the maximum number of processor modules is not installed, REQ<9:6,4:1> signals are allocated to those installed according to the algorithm specified here.)

In the absence of errors, the arbitration algorithm always puts the processor that was least recently granted the bus at the highest priority. This is achieved by giving a processor module the lowest priority whenever it wins the bus and moving the other modules up in priority by one.

To track its current priority, each processor module keeps a priority register, PRIO<9:6,4:1>. The PRIO register is updated at the end of each cycle (C in the algorithm) as shown here:

```

CACPU = CA[C] AND

! CPU command cycle

(NOT REQ[C-2]<5>) AND

(REQ[C-2]<9:6,4:1> GTR 0) AND

NOT (CA[C-1] OR CA[C-2] OR CA[C-3] OR CA[C-4]);

CASE1 = ERR[C] OR ERR[C-1] OR ERR[C-2] OR RESET; ! abort

CASE2 = CACPU AND

! higher CPU won arb

(REQ[C-2]<5,9:6,4:1> GEQ (PRIO<9:6,4:1> SLO 1)) AND

NOT CASE1;

CASE3 = CACPU AND

! this CPU arbed and

! won

(OR (REQ[C-2]<9:6,4:1> AND PRIO<9:6,4:1>)) AND

NOT (CASE2 OR CASE1);

CASE4 = NOT

! none of the above

(CASE1<0> OR CASE2<0> OR CASE3<0>);

PRIO < 9:6.4:1 > =

((SXT CASE1) AND (0001#2 SL0 NID<2:0>)) ! slot ID + 1

OR

((SXT CASE2) AND (PRIO<9:6,4:1> SLO 1)) ! shift PRIO

OR

((SXT CASE3) AND 0000001#2)

! lowest PRIO

OR

((SXT CASE4) AND PRIO<9:6,4:1>);

! PRIO unchanged

```

The effect of this logic is to reset the PRIO from the decoded node ID after RESET or error (see Table 2-4), to increase a processor module's priority whenever a higher priority processor module wins the bus, and to force a module's priority to the lowest level after it wins the bus.

This least-recently-granted priority scheme guarantees that a processor module is not locked out from bus access indefinitely by other processor requests.

#### Table 2-4 PRIO Values After RESET

| NID<2:0> | PRIO<9:6,4:1> |  |

|----------|---------------|--|

| 000      | 0000 0001     |  |

| 001      | 0000 0010     |  |

| 010      | 0000 0100     |  |

| 011      | 0000 1000     |  |

| 100      | 0001 0000     |  |

| 101      | 0010 0000     |  |

| 110      | 0100 0000     |  |

| 111      | 1000 0000     |  |

#### 2.2.6 Memory Bank Contention

Nodes arbitrate for access to memory banks. A memory bank consists of 144 DRAMs and is the smallest section of memory that can be interleaved.

A node is permitted to arbitrate for memory access only when the node previously accessing the same memory bank has completed its access. The memory bank is computed from the memory address. For purposes of this algorithm, all CSR accesses and Private commands are treated as references to bank 0. Thus, the memory bank contention system effectively prevents interleaving of CSR accesses and Private commands.

To determine whether arbitration is permitted, a node must keep command history information and update it at the end of each cycle C according to the following algorithm:

```

BANK2<5:0> =

((SXT CA<C>) AND BANK1<5:0>)) OR !conditional load

((SXT (NOT CA<C>)) AND BANK2<5:0>);

BANK1<5:0> =

((SXT CA<C>) AND COMMAND_BANK<5:0>)) OR !conditional load

((SXT (NOT CA<C>)) AND BANK1<5:0>);

BANK2_CYCLES_REMAIN<3:0> =

!count down from 13

((SXT CA<C>) AND (BANK1_CYCLES_REMAIN<3:0> - (NOT STALL<C>))) OR

((SXT ((NOT CA<C>) AND (BANK2_CYCLES_REMAIN<3:0> GTR 0))) AND

(BANK2_CYCLES_REMAIN<3:0> - (NOT STALL<C>)));

BANK1 CYCLES REMAIN<3:0> =

!count down from 13

((SXT CA<C>) AND (13#10 - (NOT STALL<C>)) OR

((SXT ((NOT CA<C>) AND (BANK1_CYCLES_REMAIN<3:0> GTR 0))) AND

(BANK1_CYCLES_REMAIN<3:0> - (NOT STALL<C>)));

BANK_PERMITTED = NOT

! does either active bank match?

((((MODULE_REQUEST_BANK<5:0> EQL BANK2<5:0>)

AND

```

```

(BANK2_CYCLES_REMAIN<3:0> GTR 0))

OR

((((MODULE_REQUEST_BANK<5:0> EQL BANK1<5:0>)

AND

(BANK1_CYCLES_REMAIN<3:0> GTR 0)));

```

This algorithm stores the identity of the preceding two banks that have passed on the bus and counts the number of remaining cycles downward during non-stalled cycles to determine when the transactions have completed. The bank for a new module request is compared against the banks of any transactions still in progress, and the arbitration is suppressed if there is a match.

Although the memory bank scheme can force short delays to arbitration for a specific bank, it cannot cause indefinite lockouts, if the requester maintains a continuous request for one bank until serviced.

## 2.2.7 IOP Arbitration Priority Scheme

The IOP module uses REQ<0> and REQ<5> to arbitrate for the bus; this means that it arbitrates at either the highest priority or the lowest priority. To avoid lockout of processors, the IOP module limits its use of high priority arbitration.

Specifically, the IOP module may not block any memory bank indefinitely by asserting REQ<5> during each available arbitration opportunity to that bank. To prevent lockouts, after the IOP accesses a memory bank once using REQ<5>, it must use REQ<0> for the next request to that bank. (If the REQ<0> arbitration is lost, the IOP may resume arbitration at REQ<5>.)

# 2.3 Bus Cycles

An LSB bus cycle is one cycle of the LSB clock. During a bus cycle, one bit is transferred on each of the bus lines. There are three types of LSB cycles:

- Command cycles

- Data cycles

- Null (unused) cycles

A bus transaction consists of one command cycle and four data cycles, separated by ten or more unrelated cycles.

## 2.3.1 Command Cycle

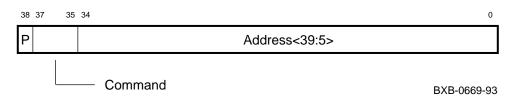

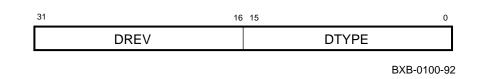

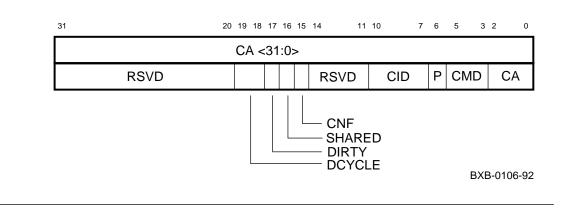

During a command cycle, the commanding node asserts CA and drives D<38:0> with command and address information. The format of D<38:0> is shown in Figure 2-2. The commanding node drives its node ID onto REQ<3:0> to provide unambiguous identification of the commanding node for hardware monitoring and debug purposes. Table 2-5 decodes the command field shown in Figure 2-2.

#### Figure 2-2 Command Cycle Format

## Table 2-5 Command Field

| Command Field                                                                                                                                                                                                         | Command                                                                                     |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| 000                                                                                                                                                                                                                   | ${f Read}-{f Read}$ the contents of the specified block                                     |  |

| 001                                                                                                                                                                                                                   | Write — Write to the specified block                                                        |  |

| 010                                                                                                                                                                                                                   | Reserved                                                                                    |  |

| 011                                                                                                                                                                                                                   | <b>Write Victim</b> <sup>1</sup> — Write of a dirty <sup>2</sup> cache block to main memory |  |

| 100                                                                                                                                                                                                                   | <b>Read CSR</b> — Read the contents of a register                                           |  |

| 101                                                                                                                                                                                                                   | Write CSR — Write to a register                                                             |  |

| 110                                                                                                                                                                                                                   | Reserved                                                                                    |  |

| 111                                                                                                                                                                                                                   | <b>Private</b> — Local operation (see page 2-12)                                            |  |

| <sup>1</sup> Victim — the only copy of a dirty cache block. This block must be flushed from cache and written to main memory to make room for a new cache block that will occupy the same physical location in cache. |                                                                                             |  |

| $^2$ Dirty — a cache block that has been modified.                                                                                                                                                                    |                                                                                             |  |

#### **Data Wrapping**

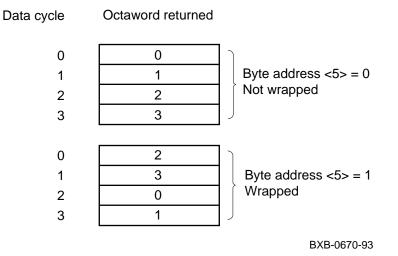

For memory transactions, the address field contains bits  $\langle 39:5 \rangle$  of the byte address. Byte address bits  $\langle 39:6 \rangle$  (D $\langle 34:1 \rangle$ ) uniquely specify the 64-byte cache block to be transferred. Byte address bit  $\langle 5 \rangle$  (D $\langle 0 \rangle$ ) specifies 32-byte wrapping as shown in Figure 2-3.

#### Figure 2-3 Data Wrapping

Byte address bit <5> (D<0>) is valid for both Read and Write transactions, and both memory reads and writes are wrapped.

For CSR requests, the address field uniquely specifies the longword CSR to be accessed.

#### Parity

D<38> is driven with odd parity over D<37:0>. That is, if the number of bits asserted in D<37:0> is even, D<38> is asserted; otherwise it is de-asserted. Modules check D<38> during command cycles to verify that the parity is correct. If the parity is incorrect, the module asserts ERR within four cycles and ignores the command.

$D{<}127{:}39{>}$  and ECC ${<}27{:}0{>}$  contain arbitrary values during command cycles.

#### **Private Command**

The Private command enables modules to use LSB cycles for local operations. Private transactions have good parity in the command cycle. The corresponding data cycles are ignored by other modules. Other modules ignore the content of Private transactions but treat them as normal transactions for arbitration and timing purposes.

A module using a Private transaction may drive arbitrary data on the bus during data cycles. The module must assert CNF during the appropriate cycle, but it may drive arbitrary information onto the SHARED and DIRTY lines during the shared/dirty cycle. If STALL is driven during the appropriate cycles, the data cycles are delayed as they are in other bus transactions.

## 2.3.2 Data Cycle

Each transaction has four data cycles. During memory data cycles, D<127:0> contain read or write data. Similarly, ECC<27:0> contain the ECC corresponding to the data in D<127:0>. If the data is sourced from a memory that uses the same ECC coding scheme as the LSB, the ECC information may be passed from that source without intermediate checking and correction.

In general, nodes receiving memory data cycles must check ECC<27:0>. However, if the data destination is a memory covered by the same ECC coding scheme, the data may be passed unchecked.

During stalled data cycles, D<127:0> and ECC<7:0> may hold arbitrary data. In the case of CSR transactions, bad parity is sent. In the case of memory transactions, the data and ECC may be arbitrary, and the ECC code may be bad or good. (The inclusion of the cycle count bits in the ECC code assures that bad data is not mistaken for good data, even in the presence of faults on the STALL line.)

During a Read CSR or Write CSR transaction, D<38:0> are driven in the first data cycle. D<37:0> contain data, and D<127:39> contain arbitrary data. D<38> has odd parity over D<37:0>. (If the number of bits asserted in D<37:0> is even, D<38> is asserted; otherwise it is deasserted.) The ECC<27:0> signals contain arbitrary values during Read CSR and Write CSR data cycles. During the remaining data cycles of a CSR transaction, D<127:0> and ECC<27:0> are not driven.

Nodes receiving CSR data cycles must check D<38> of the first data cycle for correct parity. If the parity is not correct, the module must assert ERR within four cycles.

## 2.3.3 ECC Coding

Figure 2-4 shows the ECC scheme for checking and correcting memory data cycles. The 128-bit data path is divided into four longwords, and the ECC field is divided into four corresponding check words. Figure 2-4 shows the coding scheme for D<31:0> and ECC<6:0>.

#### Figure 2-4 LSB ECC Coding

| ECC    |                                                                                       | /cle<br>ount |

|--------|---------------------------------------------------------------------------------------|--------------|

|        | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 | 1 0          |

| 6 XOR  | x x x x x x x x x x x x x x x x x x x                                                 | Х            |

| 5 XOR  | x x x x x x x x x x x x x x x x x x x                                                 | Х            |

| 4 XOR  | x x x x x x x x x x x x x x x x x x x                                                 | Х            |

| 3 XNOR | x x x x x x x x x x x x x x x x x x x                                                 | Х            |

| 2 XNOR | x x x x x x x x x x x x x x x x x x x                                                 |              |

| 1 XOR  | x x x x x x x x x x x x x x x x x x x                                                 | Х            |

| 0 XOR  | x x x x x x x x x x x x x x x x x x x                                                 |              |

BXB-0671-93

The same coding scheme is used for each of the other three longwords. The ECC field for each longword is computed from a logical XOR of all table columns corresponding to ones in the longword; bits <3:2> of the result are then inverted. (Inversion of ECC<3:2> assures that a null bus cycle is not mistaken for an error-free or correctable-error data cycle.) Two cycle count bits are included to facilitate detection of sequencing errors resulting from open circuits on the STALL line. The cycle count bits are 00, 01, 10, and 11, during the first, second, third, and fourth data cycles, respectively. The correspondence of data longwords to ECC fields is shown in Table 2-6.

#### Table 2-6 Correspondence of Data Longwords to ECC Fields

| Data Longword | ECC Field  |

|---------------|------------|

| D<31:0>       | ECC<6:0>   |

| D<63:32>      | ECC<13:7>  |

| D<95:64>      | ECC<20:14> |

| D<127:96>     | ECC<27:21> |

# 2.4 Bus Transactions

All transactions use the same format. Each transaction starts with a command cycle and ends with four data cycles. These five fixed cycles are relative to the arbitration cycles. A minimum of ten cycles separates the command cycle from the data cycles. As many as three transactions can be in progress at one time. Figure 2-5 shows a single transaction on an idle bus.

#### Figure 2-5 Single Transaction Timing

|                | 1                 | 2           | 3           | 4           | 5     |

|----------------|-------------------|-------------|-------------|-------------|-------|

| cycle          | 01234567890123456 | 78901234567 | 89012345678 | 39012345678 | 89012 |

| ARB            | x                 |             |             |             |       |

| Command        | X                 |             |             |             |       |

| CNF<br>SHR/DIR | X                 |             |             |             |       |

| STALL          |                   |             |             |             |       |

| Data           |                   | xxxx        | •••••       |             |       |

Figure 2-6 shows transaction timing for consecutive interleaved transactions with no STALLs. Note that three transactions are interleaved on the bus.

#### Figure 2-6 Interleaved Transaction Timing (Best Case)

|         | 1           |          | 2          | 3           | 4           | 5    |

|---------|-------------|----------|------------|-------------|-------------|------|

| cycle   | 01234567890 | 12345678 | 9012345678 | 39012345678 | 90123456789 | 9012 |

| ARB     | 2.          | 3        | 45         | .6          |             |      |

| CA      | 1           | 23       |            | 6           |             |      |

| Command | 1           | 23       |            | 6           |             |      |

| CNF     | 1.          | 2        | 34         | .56         |             |      |

| SHR/DIR |             | 12       |            | 56          |             |      |

| STALL   |             |          |            |             |             |      |

| Data    |             | 11       | 11.2222.33 | 333.4444.55 | 55.6666     |      |

#### 2.4.1 Signals Used in Bus Transactions

#### Command/Address (CA)

The CA signal is asserted by the bus commander to indicate that the current cycle is a command cycle. This signal is monitored by all nodes.

#### Confirm (CNF)

The confirm (CNF) signal is asserted by the node targeted by the transaction, typically the node that will supply data for a Read transaction or accept data for a Write transaction.

For memory transactions, CNF is asserted by the selected memory module. Processors are not required to assert CNF when they assert DIRTY and supply read data from their caches.

For CSR transactions, CNF is asserted by the targeted device. For Write CSR transactions that target multiple modules (for example, a Write to

LIOINTR), more than one responder may assert CNF. Typically, a targeted node is required to assert CNF for a CSR request and is required to supply read data or accept write data. However, for a Write CSR to the LMBPR register, the IOP may indicate a busy condition by failing to assert CNF.

The STxC instruction is used to access the LMBPR register. The lack of CNF assertion signals that the instruction has failed. Operating system software replays the STxC instruction in a loop with a timeout counter to enable detection of hard LSB errors without lockout problems in multiprocessor systems.

In Private transactions, CNF is asserted by the commander.

The CNF signal is typically asserted three cycles after CA, but the assertion may be delayed by STALLs.

#### SHARED and DIRTY (SHR/DIR)

The SHARED and DIRTY signals are asserted by processors to indicate the state of their cache entry for the specified address. SHARED and DIRTY must not be asserted for CSR transactions. The SHARED and DIRTY signals are typically asserted five cycles after the command cycle, but the assertion may be delayed by STALLs.

These signals are described in Section 2.7.

STALL

The STALL signal is used by any module during any transaction to indicate that the data cycles will be delayed by one or more cycles. Because the delayed data cycles could interfere with bus cycles of other transactions, the occurrence of STALL influences the timing of other transactions. Specifically, assertion of STALL during a specific cycle B causes the insertion of a dead cycle at cycle B+2 into every bus transaction that is active during cycle B+2.

STALL is asserted only during the ninth cycle after CA, which, itself, may be delayed by prior STALLs. That is, STALL cycles are not counted when determining which is the ninth cycle after CA. STALL may be repeated for multiple cycles.

#### LOCKOUT

A processor module asserts LOCKOUT after it has failed to gain access to a lock variable (for example, if a VAX 7000/10000 byte-update sequence fails repeatedly). When one or more processors assert LOCKOUT, other processors delay new outgoing requests until LOCKOUT is released. This allows the processor or processors asserting lockout to complete their access without interference.

#### Corrected Read Data (CRD)

The corrected read data (CRD) signal is used by memory modules to signal that the data supplied in response to an LSB Read command had a correctable error when it was retrieved from storage. The node supplying the data performs the correction (for example, by ECC), and the data supplied on the LSB and its ECC are correct. Processor nodes use this signal to initiate an exception to notify the operating system of this event.

### 2.4.2 Timing Definition

The positions of the various cycles for a transaction can be computed as follows:

```

V_CA_D<B> = VALID_COMMAND_DETECTED<B>; ! as defined earlier

CYCLE_AFTER_CA<15:1> =

(CYCLE_AFTER_CA<14:1> SR0 (NOT STALL<B-2>)) &

V_CA_D<B>;

((SXT V_CA_D<B>) AND 1000000000#2);

DATA_CYCLE<B+1> = CYCLE_AFTER_CA<15:11> GTR 0;

CNF_CYCLE<B+1> = CYCLE_AFTER_CA<5>;

SHR_CYCLE<B+1> = CYCLE_AFTER_CA<3>;

STALL_CYCLE<B+1> = CYCLE_AFTER_CA<9> OR STALL<B>;

```

### 2.4.3 Transaction Examples

### Figure 2-7 Simple STALL Timing

|         | 1                 | 2          | 3          | 4           | 5       |

|---------|-------------------|------------|------------|-------------|---------|

| cycle   | 01234567890123456 | 5789012345 | 6789012345 | 56789012345 | 6789012 |

| ARB     | X                 |            |            |             |         |

| CA      | X                 |            |            |             |         |

| Command | X                 |            |            |             |         |

| CNF     | XX                |            |            |             |         |

| SHR/DIR | X                 |            |            |             |         |

| STALL   |                   | .111       |            |             |         |

| Data    |                   | XXXX       |            |             |         |

### Figure 2-8 CSR Transaction Timing

|         |                   | 1       |      | 2      | 3          | 4           | 5        |

|---------|-------------------|---------|------|--------|------------|-------------|----------|

| cycle   | 01234567          | 8901234 | 5678 | 901234 | 5678901234 | 15678901234 | 56789012 |

| ARB     | X                 |         |      |        |            |             |          |

| CA      | X.                |         |      |        |            |             |          |

| Command | X.                |         |      |        |            |             |          |

| CNF     |                   | .X      |      |        |            |             |          |

| SHR/DIR |                   |         |      |        |            |             |          |

| STALL   |                   |         |      |        |            |             |          |

| Data    | • • • • • • • • • |         | •••X |        |            |             |          |

### Figure 2-9 Single STALL in Interleaved Transactions

|         | 1                | 2           | 3          | 4           | 5      |

|---------|------------------|-------------|------------|-------------|--------|

| cycle   | 0123456789012345 | 67890123456 | 5789012345 | 67890123456 | 789012 |

| ARB     | 123.             | 45          | б          |             |        |

| CA      |                  | 34          | .56        |             |        |

| Command | 12               | 34          | .56        |             |        |

| CNF     |                  | 4           | 5 6        |             |        |

| SHR/DIR |                  | 23          | .45        | .6          |        |

| STALL   |                  |             |            |             |        |

| Data    |                  | 1111.2222   | 2.3333.444 | 4.5555.6666 |        |

#### Figure 2-10 Best-Case Interleaved Transaction Timing

|                  | 1                 | 2           | 3          | 4          | 5         |

|------------------|-------------------|-------------|------------|------------|-----------|

| cycle            | 01234567890123456 | 78901234567 | 8901234567 | 8901234567 | 89012     |

| ARB              | 123               |             |            |            |           |

| Command          | 123               | 5.          | 6          |            | • • • • • |

| SHR/DIR<br>STALL |                   |             | 56.        |            |           |

| Data             |                   |             |            |            |           |

### 2.4.4 Interrupts

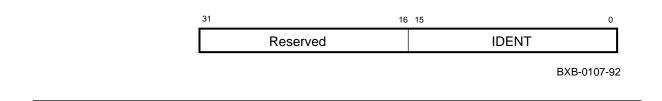

LSB nodes interrupt each other by writing to defined CSRs. Two interrupt mechanisms are provided through registers in the LSB CSR space in processors and the IOP module:

- *Vectored interrupts* are the traditional I/O adapter interrupts. The interrupt service routine is specified as a function of an IDENT vector supplied by the adapter. The operating system loads the value of this IDENT vector into each I/O adapter at system initialization.

- *Non-vectored or implied vector interrupts* have architecturally defined mechanisms for entering the relevant interrupt service routine and therefore do not require any additional information. Interprocessor interrupts, system error interrupts, and corrected read data interrupts are examples of non-vectored interrupts.

The LSB interrupt mechanism can target a maximum of four processors, while the LSB supports a maximum of six processors. Both KN7AA and KA7AA processor modules use the node ID to determine if a node is eligible to become one of the four possible interrupt targets.

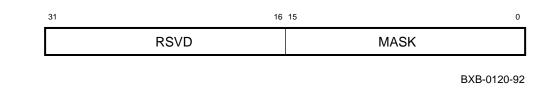

### 2.4.4.1 Vectored Interrupts