# VAX 7000/10000 KA7AA CPU Technical Manual

Order Number EK—KA7AA—TM.001

The KA7AA is a VAX CPU module designed for the LSB platform. It is based on the NVAX+ microprocessor and is used in the VAX 7000 and VAX 10000 computer systems. It supports up to seven MS7AA memory modules in a uniprocessor configuration and one IOP module per system. Used in a single-processor system, the KA7AA module achieves a minimum scalar performance equivalent to that of more than 20 VAX 11/780 systems. A multiprocessor system supports up to six KA7AA CPU modules.

#### First Printing, December 1992

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright © 1992 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

Alpha AXP DECUS VAXBI

AXP DWMVA VAXELN

DEC OpenVMS VMScluster

DECchip ULTRIX XMI

DEC LANcontroller UNIBUS The AXP logo DECnet VAX digital

$\ensuremath{\mathsf{OSF/1}}$  is a registered trademark of the Open Software Foundation, Inc.

**FCC NOTICE:** The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

# **Contents**

| rrerace |                                   | xi   |

|---------|-----------------------------------|------|

|         |                                   |      |

| Chapter | 1 CPU Module Overview             |      |

| 1.1     | NVAX+ CPU Chip                    | 1-3  |

| 1.2     | Backup Cache (B-Cache)            |      |

| 1.3     | LSB Interface (LEVI)              |      |

| Chapter | 2 CPU Chip                        |      |

| 2.1     | Data Types                        | 2-2  |

| 2.2     | Instruction Set                   |      |

| 2.3     |                                   | 2-2  |

| 2.4     | Address Space                     |      |

| 2.4.1   | Virtual Address Space             |      |

| 2.4.2   | Physical Address Space            |      |

| 2.5     | Memory Management                 |      |

| 2.5.1   | System Space Address Translation  |      |

| 2.5.2   | Process Space Address Translation | 2-5  |

| 2.5.2.1 | P0 Region Address Translation     | 2-5  |

| 2.5.2.2 | P1 Region Address Translation     | 2-5  |

| 2.5.3   | Page Table Entry Format           | 2-6  |

| 2.5.4   | Translation Buffer                | 2-7  |

| 2.5.5   | Memory Management Control         | 2-7  |

| 2.6     | Exceptions and Interrupts         | 2-9  |

| 2.6.1   | Exceptions                        | 2-10 |

| 2.6.1.1 | Arithmetic Exceptions             | 2-11 |

| 2.6.1.2 | Memory Management Exceptions      | 2-12 |

| 2.6.1.3 | Emulated Instruction Exceptions   | 2-13 |

| 2.6.1.4 | System Failure Exceptions         | 2-14 |

| 2.6.2   | Interrupts                        | 2-15 |

| 2.6.2.1 | External Interrupt Requests       | 2-16 |

| 2.6.2.2 | Internal Interrupt Requests       | 2-16 |

| 2.7     | System Control Block              | 2-18 |

| 2.8     | Process Structure                 | 2-22 |

| 2.9     | Functional Partitions             | 2-25 |

| 2.9.1   | Ibox                              |      |

| 2.9.2   | Ebox and Microsequencer           | 2-27 |

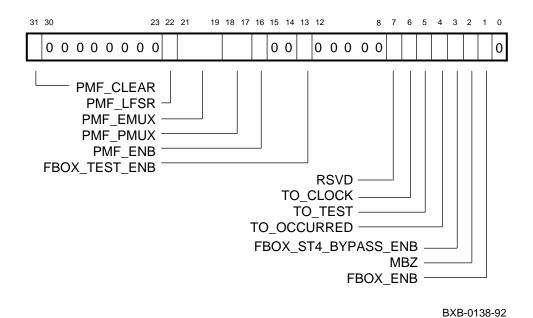

| 2.9.3   | Fbox                              |      |

| 2.9.4   | Mbox                              |      |

| 2.9.5   | Cbox                              |      |

| 2.10    | General Purpose Registers         | 2-30 |

| 2.11    | Internal Processor Registers                                      | 2-31 |

|---------|-------------------------------------------------------------------|------|

| 2.11.1  | Identification Registers                                          |      |

|         | CPUID—CPU Identification Register                                 | 2-36 |

|         | SID—System Identification Register                                |      |

| 2.11.2  | Ibox Registers                                                    |      |

|         | VMAR—VIC Memory Address Register                                  |      |

|         | VTAG—VIC Tag Register                                             | 2-40 |

|         | VDATA—VIC Data Register                                           |      |

|         | ICSR—Ibox Control and Status Register                             |      |

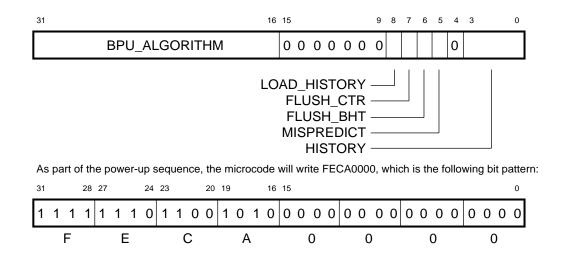

|         | BPCR—Branch Prediction Control Register                           | 2-43 |

| 2.11.3  | Ebox Registers                                                    |      |

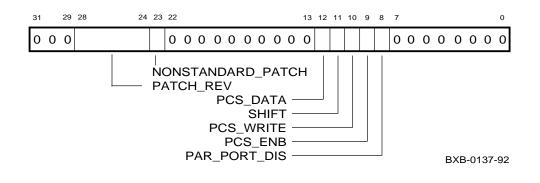

|         | PCSCR—Patchable Control Store Control Register                    |      |

|         | ECR—Ebox Control Register                                         | 2-48 |

| 2.11.4  | Mbox Registers                                                    |      |

|         | MP0BR—Mbox P0 Base Register                                       |      |

|         | MP0LR—Mbox P0 Length Register                                     |      |

|         | MP1BR—Mbox P1 Base Register                                       |      |

|         | MP1LR—Mbox P1 Length Register                                     |      |

|         | MSBR—Mbox System Base Register                                    |      |

|         | MSLR—Mbox System Length Register                                  |      |

|         | MMAPEN—Mbox Map Enable Register                                   |      |

|         | PAMODE—Physical Address Mode Register                             |      |

|         | MMEADR—MME Address Register                                       |      |

|         | MMEPTE—MME PTE Address Register                                   |      |

|         | MMESTS—MME Status Register                                        |      |

|         | TBADR—Translation Buffer Parity Address Register                  |      |

|         | TBSTS—Translation Buffer Parity Status Register                   |      |

|         | PCADR—P-Cache Parity Error Address Register                       |      |

|         | PCSTS—P-Cache Parity Status Register                              |      |

|         | PCCTL—P-Cache Control Register                                    |      |

|         | PCTAG—P-Cache Tag Registers                                       |      |

|         | PCDAP—P-Cache Data Parity Registers                               |      |

| 2.11.5  | Cbox Registers                                                    |      |

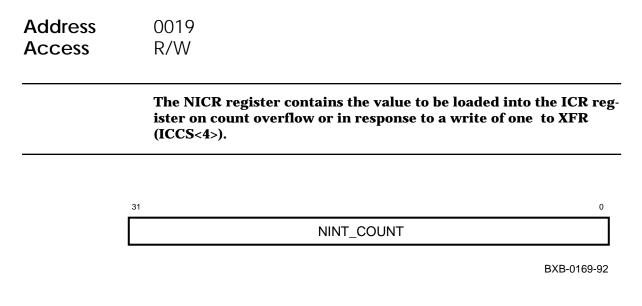

| ۵.11.5  | ICCS—Interval Count Control and Status Register                   |      |

|         | NICR—Next Interval Count Register                                 |      |

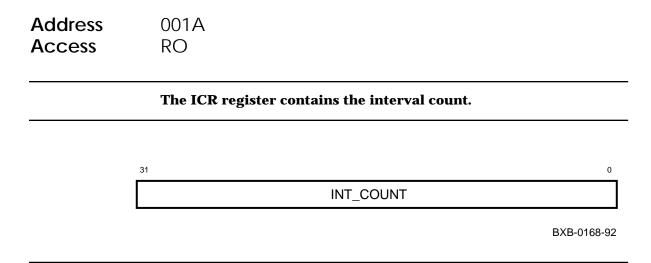

|         | ICR—Interval Count Register                                       |      |

|         | · · · · · · · · · · · · · · · · · · ·                             |      |

|         | TODR—Time-of-Day Register                                         |      |

|         | BIU_CTL—BIU Control Register DIAG_CTL—Diagnostic Control Register |      |

|         |                                                                   |      |

|         | BC_TAG—B-Cache Error Tag Register                                 |      |

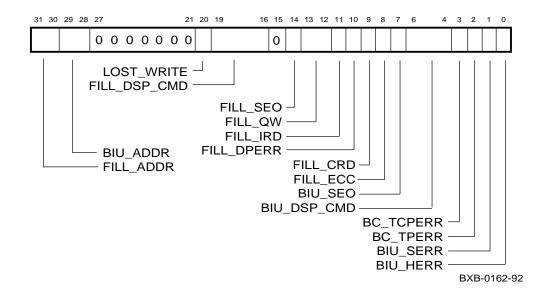

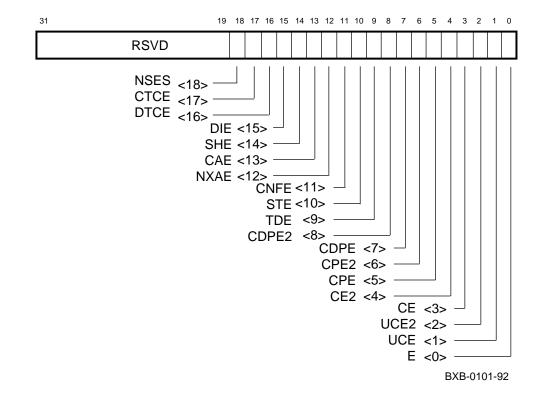

|         | BIU_STAT—BIU Status Register                                      |      |

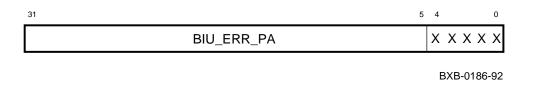

|         | BIU_ADDR—BIU Address Register                                     |      |

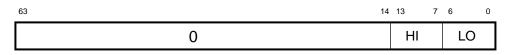

|         | FILL_SYND—Fill Syndrome Register                                  |      |

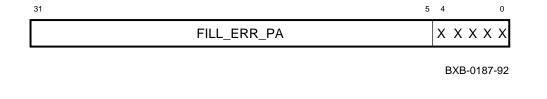

|         | FILL_ADDR—Fill Address Register                                   |      |

|         | BEDECC—Software ECC Register                                      |      |

|         | CHALT—Console Halt Register                                       | 2-96 |

| Chapter | 3 Cache Subsystem                                                 |      |

| 3.1     | Virtual Instruction Cache                                         | 3-3  |

| 3.2     | Primary Cache                                                     |      |

| 3.3     | Backup Cache                                                      |      |

| 3.3.1   | B-Cache States                                                    |      |

| 3.3.2   | B-Cache State Changes                                             |      |

| 3.4     | Cache Backmaps                                                    |      |

| 3.4.1                 | P-Map                                                |      |

|-----------------------|------------------------------------------------------|------|

| $3.4.2 \\ 3.5$        | B-Map<br>Victim Buffer                               |      |

| 3.6                   | Write Policy                                         |      |

| 3.7                   | B-Cache Operating Modes                              |      |

| 3.8                   | Cache Initialization                                 |      |

|                       |                                                      |      |

| Chapte                | r 4 LSB Bus Interface                                |      |

| 4.1                   | LEVI Address Path                                    | 4-2  |

| 4.2                   | LEVI Data Path                                       |      |

| 4.3                   | LEVI Controllers                                     |      |

| 4.3.1                 | LEVI Processor Controller                            |      |

| 4.3.2                 | LEVI Data Controller                                 |      |

| 4.3.3                 | LSB Controller                                       |      |

| 4.4                   | Interfacing Rules                                    |      |

| 4.4.1                 | Dual-Ported Access Synchronization                   |      |

| 4.4.2                 | LSB Arbitration                                      |      |

| 4.5                   | Address Space Mapping                                |      |

| $4.6 \\ 4.6.1$        | LEVI Transactions                                    |      |

| $\frac{4.6.1}{4.6.2}$ | LSB-Initiated Transactions                           |      |

| 4.6.2                 | Transaction Ordering                                 |      |

| 5.1                   | r 5 Console Overview  CPU Console Hardware           |      |

| 5.1.1                 | Serial ROM                                           |      |

| 5.1.2                 | Serial Port                                          |      |

| 5.1.3                 | FEPROMS                                              |      |

| 5.1.4                 | EEPROM                                               |      |

| 5.1.5<br>5.1.5.1      | UARTs Ctrl/P Character Detection and Halt Protection |      |

| 5.1.5.1               | UART Register Addressing                             |      |

| 5.1.6                 | Watch Chip                                           |      |

| 5.2                   | Console Program Invocation                           |      |

| 5.3                   | Console Registers                                    |      |

|                       | Gbus\$WHAMI                                          |      |

|                       | Gbus\$LEDs                                           |      |

|                       | Gbus\$PMask                                          | 5-11 |

|                       | Gbus\$Intr                                           | 5-13 |

|                       | Gbus\$Halt                                           |      |

|                       | Gbus\$LSBRST                                         |      |

|                       | Gbus\$Misc                                           |      |

|                       | Gbus\$RMode                                          |      |

|                       | Gbus\$LTagRW                                         | 5-21 |

| Chapte                | r 6 I/O Operations                                   |      |

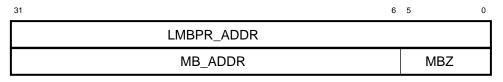

| 6.1                   | Mailbox Data Structure                               | 6-1  |

| 6.2                   | Mailbox Operation                                    |      |

| 6.3                   | Device Interrupt Handling                            |      |

| 6.4                   | I/O Operation Registers                              | 6-4  |

|                | LMBOX—LSB Mailbox Register                  | 6-5          |

|----------------|---------------------------------------------|--------------|

| Chapter        | 7 CPU Module Registers                      |              |

| 7.1            | Register Mapping                            | 7-9          |

| 7.2            | Register Descriptions                       |              |

| 7.2            | LDEV—Device Register                        |              |

|                | LBER—Bus Error Register                     |              |

|                | LCNR—Configuration Register                 |              |

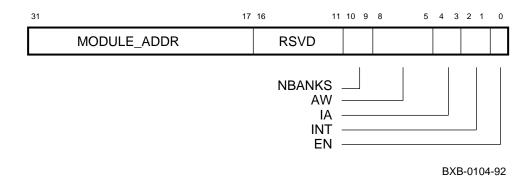

|                | LMMR0-7—Memory Mapping Registers            |              |

|                | LBESR0-3—Bus Error Syndrome Registers       |              |

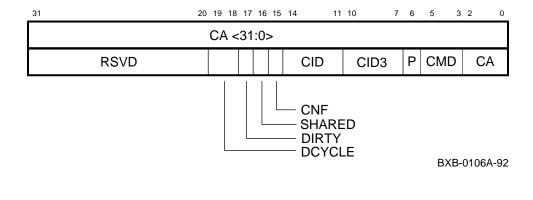

|                | LBECR0,1—Bus Error Command Registers        |              |

|                | LIOINTR—I/O Interrupt Register              |              |

|                | LIPINTR—Interprocessor Interrupt Register   |              |

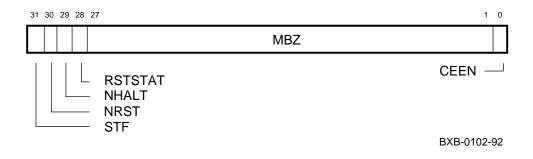

|                | LMODE—Mode Register                         |              |

|                | LMERR—Module Error Register                 |              |

|                | LLOCK—Lock Address Register                 |              |

|                | LDIAG—LSB Diagnostic Control Register       |              |

|                | LTAGA—Tag Address Register                  |              |

|                | LTAGW—Tag Write Data Register               |              |

|                | LCON0,1—Console Communication Registers     |              |

|                | LPERF—Performance Counter Control Register  |              |

|                | LCNTR0,1—Performance Counter Registers      |              |

|                | LMISSADDR—Last Miss Address Register        |              |

| 8.1<br>8.2     | Initialization Overview                     | 8-2          |

| 8.2.1<br>8.2.2 | SROM Operation                              |              |

| 8.2.3          | Additional Power-Up Testing                 |              |

| 8.2.3          | Console Entry                               |              |

| 8.3.1          | Boot Processor Arbitration                  |              |

| 8.3.2          | Boot Processor System Setup                 |              |

| 8.3.3          | Operating System Startup                    |              |

| •              | 9 Error Handling                            |              |

| 9.1            | Software Error Handling                     |              |

| 9.1.1          | Error State Collection                      |              |

| 9.1.2          | Error Analysis                              |              |

| 9.1.3          | Error Recovery                              |              |

| 9.1.3.1        | Cache Coherence in Error Handling           |              |

| 9.1.3.2        | Cache Enable, Disable, and Flush Procedures |              |

| 9.1.3.3        | Extracting Data from the B-Cache            |              |

| 9.1.3.4        | Cache and TB Test Procedures                |              |

| 9.1.4<br>9.2   | Error Retry                                 |              |

| 9.2<br>9.3     | Error Reports                               |              |

|                | Console Halt and Halt Interrupt             |              |

| 9.4            | Machine Checks                              |              |

| 9.4.1 $9.4.2$  |                                             |              |

| J.4.L          | MCHK_INT.ID_VALUE                           | <b>9-2</b> 4 |

| 9.4. |                                                         |      |

|------|---------------------------------------------------------|------|

| 9.4. | 4 MCHK_MOVC_STATUS                                      | 9-24 |

| 9.4. | 5 MCHK_ASYNC_ERROR                                      | 9-24 |

| 9.4. | 6 MCHK_SYNC_ERROR                                       | 9-25 |

| 9.4. | 7 Inconsistent Status in Machine Checks                 | 9-31 |

| 9.5  | Hard Error Interrupts                                   | 9-32 |

| 9.6  | Soft Error Interrupts                                   | 9-40 |

| 9.7  | Kernel Stack Not Valid Exception                        | 9-43 |

| 9.8  | System Environment Errors                               | 9-44 |

| 9.8. | 1 Error Categories                                      | 9-44 |

| 9.8. | e e e e e e e e e e e e e e e e e e e                   |      |

| 9.8. | 1.2 Asynchronous Errors                                 | 9-44 |

| 9.8. | 2 Environment Error Sources                             | 9-45 |

| 9.8. | 2.1 LEVI Errors                                         | 9-45 |

| 9.8. | 2.2 LSB Errors                                          | 9-46 |

|      |                                                         |      |

| Exam | nples                                                   |      |

| 2-1  | BIU_CTL Read                                            | 2-81 |

| 2-2  | BIU_CTL Write                                           |      |

| 2-3  | DIAG_CTL Read                                           | 2-84 |

| 2-4  | DIAG_CTL Write                                          |      |

| 9-1  | Memory Storage Allocation to the Error State            | 9-3  |

| 9-2  | Collection Error State                                  |      |

|      | ure 1-1 Block Diagram of a VAX 7000 or VAX 10000 System |      |

|      | ure 1-2 KA7AA CPU Module Block Diagram                  |      |

|      | ure 2-1 Virtual Address Space Layout                    |      |

|      | ure 2-2 Physical Address Space Layouts                  |      |

|      | ure 2-3 SBR and SLR Registers                           |      |

|      | ure 2-4 P0BR and P0LR Registers                         |      |

|      | ure 2-5 P1BR and P1LR Registers                         |      |

|      | ure 2-6 PTE Format (21-Bit PFN)                         |      |

|      | ure 2-7 PTE Format (25-Bit PFN)                         |      |

|      | ure 2-8 Memory Management Control Registers             |      |

|      | ure 2-9 Minimum Stack Frame                             |      |

|      | ure 2-10 Expanded Stack Frame                           |      |

|      | ure 2-11 Arithmetic Exception Stack Frame               |      |

|      | ure 2-12 Memory Management Exception Stack Frame        |      |

|      | ure 2-13 Emulated Instruction Trap Stack Frame          |      |

|      | ure 2-15 Interrupt Control Registers                    |      |

|      | ure 2-16 System Control Block Base Register             |      |

|      | ure 2-17 System Control Block Vector                    |      |

|      | ure 2-18 Process Control Block                          |      |

|      | ure 2-19 Processor Status Longword                      |      |

|      | ure 2-19 Processor Status Longword                      |      |

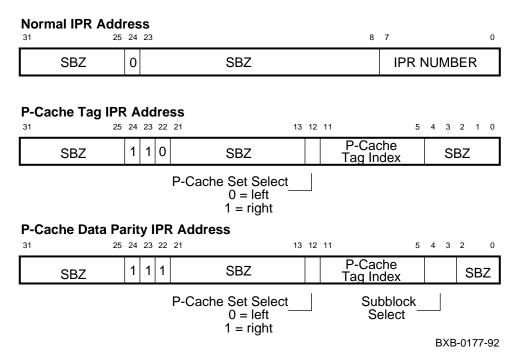

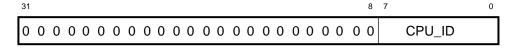

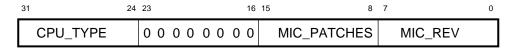

|      | ure 2-21 IPR Address Formats                            |      |

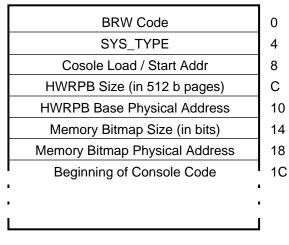

|      | ure 2-22 Console Dispatch Data Structure                |      |

|      | ure 2-23 SYS_TYPE Parameters                            |      |

|      | ure 3-1 KA7AA CPU Module Cache Organization.            |      |

|      | ure 4-1 LEVI Block Diagram                              |      |

|      | ure 6-1 Mailbox Data Structure                          |      |

| ı ıg |                                                         |      |

|              | 6-2 Mailbox Pointer Structure                    |      |

|--------------|--------------------------------------------------|------|

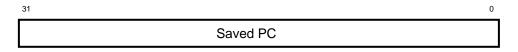

| Figure       | 9-1 Console Saved PC                             | 9-11 |

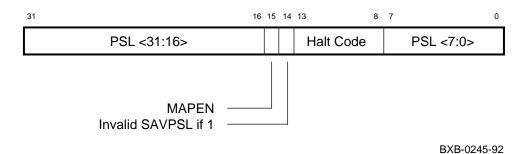

| Figure       | 9-2 Console Saved PSL                            | 9-11 |

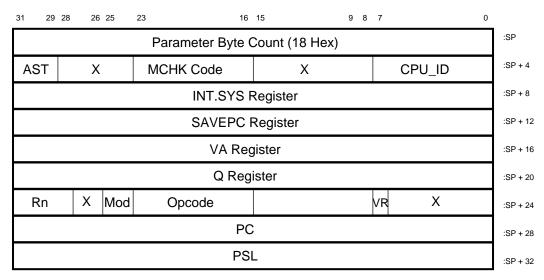

| Figure       | 9-3 Machine Check Exception Stack Frame          | 9-14 |

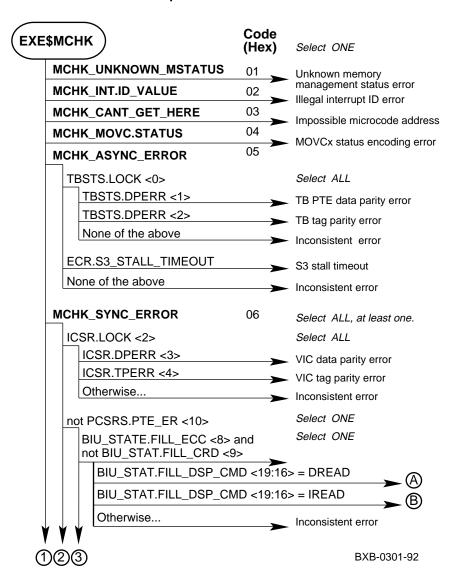

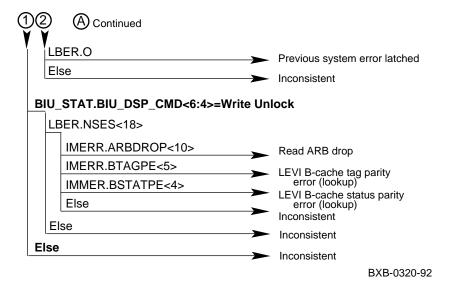

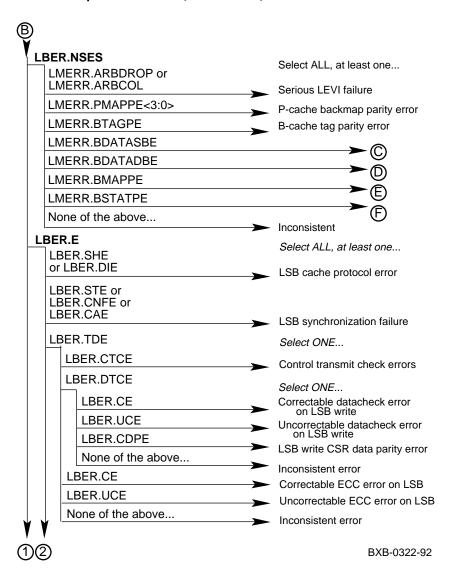

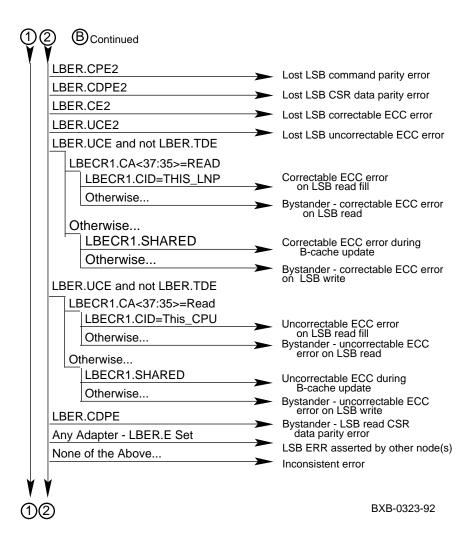

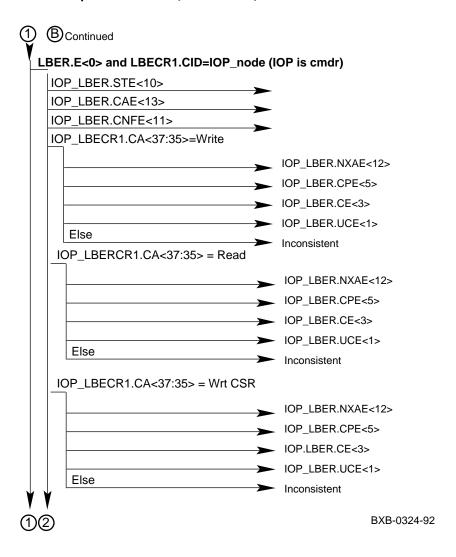

| Figure       | 9-4 Machine Check Exception Parse Tree           | 9-17 |

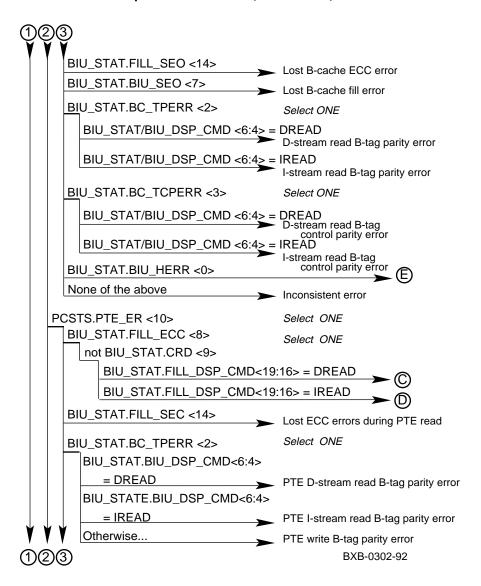

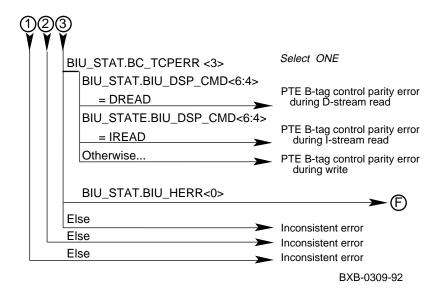

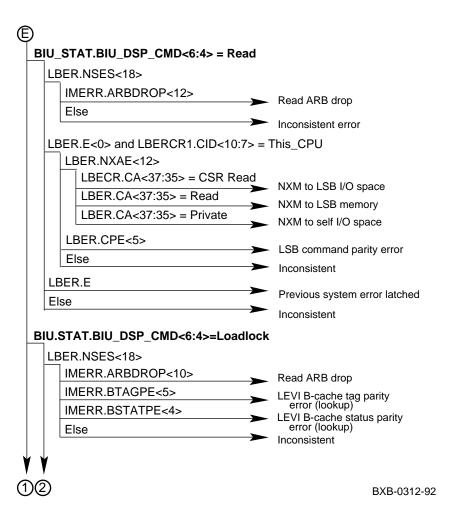

| Figure       | 9-5 Hard Error Interrupt Parse Tree              | 9-32 |

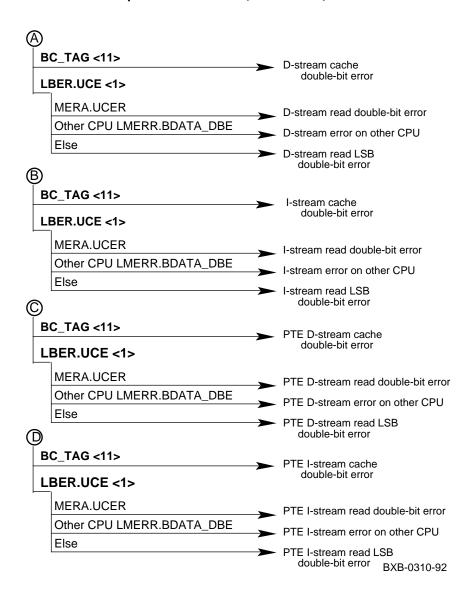

|              | 9-6 Soft Error Interrupt Parse Tree              |      |

| 8            | 1                                                |      |

| Talalaa      |                                                  |      |

| Tables       |                                                  |      |

| 1            | DEC 7000/10000 and VAX 7000/10000 Documentation  | xiii |

| 1-1          | NVAX+ CPU Chip Functional Units                  |      |

| 2-1          | KA7AA Module Exceptions                          |      |

| 2-2          | Arithmetic Exception Codes                       |      |

| 2-2<br>2-3   | Memory Management Exceptions                     |      |

| 2-3<br>2-4   | Emulated Instruction Trap Stack Frame Parameters |      |

|              |                                                  |      |

| 2-5          | External Interrupt Requests                      |      |

| 2-6          | Internal Interrupt Requests                      |      |

| 2-7          | Software Interrupt Requests                      |      |

| 2-8          | System Control Block Vector Bit Functions        |      |

| 2-9          | System Control Block Layout                      |      |

| 2-10         | Processor Status Longword Bits                   |      |

| 2-11         | General Purpose Register Usage                   |      |

| 2-12         | IPR Address Space Decoding                       |      |

| 2-13         | KA7AA Internal Processor Registers               |      |

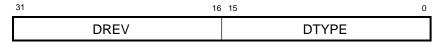

| 2-14         | Identification Registers                         |      |

| 2-15         | CPUID Register Bit Definitions                   |      |

| 2-16         | SID Register Bit Definitions                     |      |

| 2-17         | Ibox Registers                                   | 2-38 |

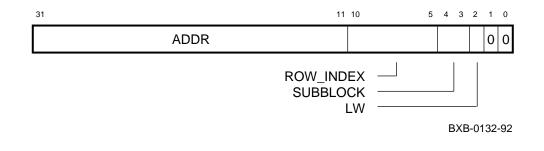

| 2-18         | VMAR Register Bit Definitions                    | 2-39 |

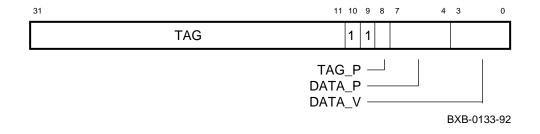

| 2-19         | VTAG Register Bit Definitions                    | 2-40 |

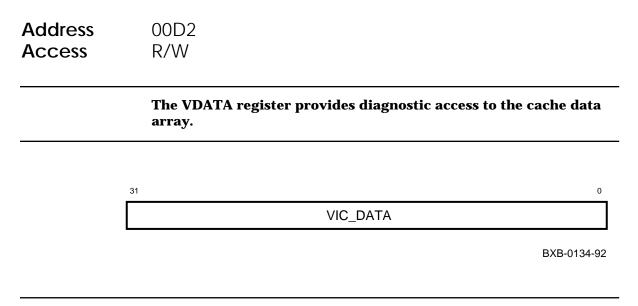

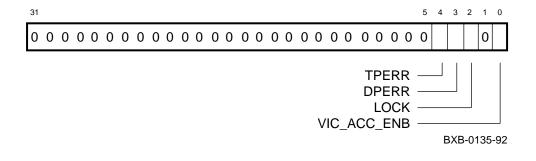

| 2-20         | VDATA Register Bit Definitions                   | 2-41 |

| 2-21         | ICSR Register Bit Definitions                    | 2-42 |

| 2-22         | BPCR Register Bit Definitions                    |      |

| 2-23         | BPCR Write Actions                               |      |

| 2-24         | Ebox Registers                                   |      |

| 2-25         | PCSCR Register Bit Definitions                   |      |

| 2-26         | Ebox Control Register Bit Definitions            |      |

| 2-27         | Mbox Registers                                   |      |

| 2-28         | MP0BR Register Bit Definitions                   |      |

| 2-29         | MP0LR Register Bit Definitions                   |      |

| 2-30         | MP1BR Register Bit Definitions                   |      |

| 2-31         | MP1LR Register Bit Definitions                   |      |

| 2-32         | MSBR Register Bit Definitions                    |      |

| 2-33         | MSLR Register Bit Definitions                    |      |

| 2-34         | MMAPEN Register Bit Definition                   |      |

| 2-34         | PAMODE Register Bit Definition                   |      |

|              |                                                  |      |

| 2-36<br>2-37 | MMEADR Register Bit Definitions                  |      |

|              | MMEPTE Address Register Bit Definitions          |      |

| 2-38         | MMESTS Register Bit Definitions                  |      |

| 2-39         | TBADR Register Bit Definitions                   |      |

| 2-40         | TBSTS Register Bit Definitions                   |      |

| 2-41         | PCADR Register Bit Definitions                   |      |

| 2-42         | PCSTS Register Bit Definitions                   |      |

| 2-43         | PCCTL Register Bit Definitions                   | 2-68 |

| 2-44 | PCTAG Register Bit Definitions                  | 2-70 |

|------|-------------------------------------------------|------|

| 2-45 | PCDAP Register Bit Definitions                  |      |

| 2-46 | Cbox Registers                                  |      |

| 2-47 | ICCS Register Bit Definitions                   |      |

| 2-48 | NICR Register Bit Definitions                   |      |

| 2-49 | ICR Register Bit Definitions                    |      |

| 2-50 | TODR Register Bit Definitions                   |      |

| 2-51 | BIU_CTL Register Bit Definitions                |      |

| 2-52 | DIAG_CTL Register Bit Definitions               |      |

| 2-53 | BC_TAG Register Bit Definitions                 |      |

|      |                                                 |      |

| 2-54 | BIU_STAT Register Bit Definitions               |      |

| 2-55 | BIU_ADDR Register Bit Definitions               |      |

| 2-56 | FILL_SYND Register Bit Definitions              |      |

| 2-57 | Syndromes for Single-Bit Errors                 |      |

| 2-58 | FILL_ADDR Register Bit Definitions              |      |

| 2-59 | BEDECC Register Bit Definitions                 |      |

| 2-60 | CHALT Register Bit Definitions                  |      |

| 2-61 | SYS_TYPE Parameter Definitions                  |      |

| 3-1  | Virtual Instruction Cache Attributes            |      |

| 3-2  | Primary Cache Attributes                        |      |

| 3-3  | B-Cache States                                  | 3-6  |

| 3-4  | Effect of Processor Action on B-Cache Line      | 3-7  |

| 3-5  | Effect of LSB Bus Action on B-Cache Line        | 3-8  |

| 3-6  | KA7AA CPU Module Response to Incoming Addresses | 3-8  |

| 3-7  | Selection of the B-Cache Operating Mode         |      |

| 4-1  | LSB Command Field Encodings                     |      |

| 4-2  | Processor-LEVI Actions During Transactions      |      |

| 5-1  | Gbus Components                                 |      |

| 5-2  | Console Registers                               |      |

| 5-3  | Gbus\$WHAMI Register Bit Definitions            |      |

| 5-4  | Gbus\$LEDs Register Bit Definitions             |      |

| 5-5  | Gbus\$PMask Register Bit Definitions            |      |

| 5-6  | Gbus\$Intr Register Bit Definitions             |      |

| 5-7  | Gbus\$Halt Register Bit Definitions             |      |

| 5-8  | Gbus\$Misc Register Bit Definitions             |      |

| 6-1  | Mailbox Data Structure                          |      |

| 6-2  | Mailbox Pointer Structure                       |      |

| 6-3  |                                                 |      |

|      | KA7AA CPU Interrupts                            |      |

| 6-4  | LMBOX Register Bit Definitions                  |      |

| 7-1  | LSB Node Space Base Addresses                   |      |

| 7-2  | CPU Module Registers                            |      |

| 7-3  | LDEV Register Bit Definitions                   |      |

| 7-4  | LBER Register Bit Definitions                   |      |

| 7-5  | LCNR Register Bit Definitions                   |      |

| 7-6  | LMMR Register Bit Definitions                   |      |

| 7-7  | LBESR Register Bit Definitions                  |      |

| 7-8  | Syndromes for Single-Bit Errors                 |      |

| 7-9  | LBECR Register Bit Definitions                  |      |

| 7-10 | LIOINTR Register Bit Definitions                | 7-16 |

| 7-11 | LSB Interrupt Mapping                           | 7-17 |

| 7-12 | LIPINTR Register Bit Definitions                |      |

| 7-13 | LMODE Register Bit Definitions                  |      |

| 7-14 | LMERR Register Bit Definitions                  |      |

| 7-15 | LLock Register Bit Definitions                  |      |

| 7-16 | LDIAG Register Bit Definitions                  |      |

| 7-17 | LTAGA Register Bit Definitions                  |      |

| 7-18 | LTAGW Register Bit Definitions         | 7-30 |

|------|----------------------------------------|------|

| 7-19 | LCON Register Bit Definitions          |      |

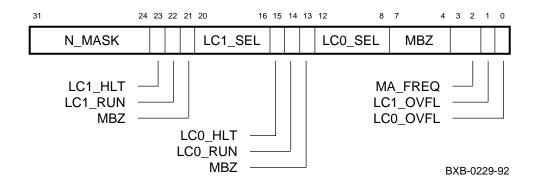

| 7-20 | LPERF Register Bit Definitions         | 7-33 |

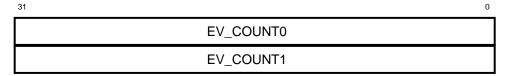

| 7-21 | LCNTR Register Bit Definitions         | 7-37 |

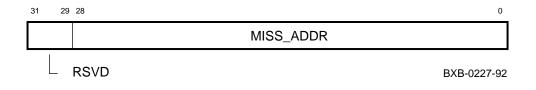

| 7-22 | LMISSADDR Register Bit Definitions     |      |

| 9-1  | Error Categories by SCB Entry Points   | 9-10 |

| 9-2  | Console Halt Codes                     | 9-12 |

| 9-3  | CPU State Initialized on Console Halt  | 9-13 |

| 9-4  | Machine Check Stack Frame Fields       | 9-15 |

| 9-5  | Machine Check Codes in the Stack Frame | 9-16 |

|      |                                        |      |

## Intended Audience

This manual is written for developers of system and application software based on the LSB platform of VAX computer systems. It assumes machine level programming knowledge and familiarity with the OpenVMS VAX operating system.

#### **Document Structure**

The material is presented in nine chapters.

- Chapter 1, **CPU Module Overview**, presents an overall introduction to the KA7AA CPU module.

- Chapter 2, **CPU Chip**, describes the functions and operations of the central processor of the KA7AA CPU module. It discusses such topics as addressing, memory management, exceptions and interrupts, functional partitions of the CPU chip, and internal processor registers.

- Chapter 3, Cache Subsystem, describes the elements and operations

of the cache hierarchy, which includes the virtual instruction cache,

the primary cache, and the backup cache.

- Chapter 4, LSB Bus Interface, describes the functions and operations

of the LEVI gate arrays that provide the CPU module interface to the

LSB bus. It discusses processor-initiated and LSB bus-initiated transactions, LEVI address and data paths, and the LEVI controllers.

- Chapter 5, Console Overview, gives a brief description of the various elements that comprise the console. It also describes the Gbus registers, which perform console control, diagnostic, and interrupt-related functions.

- Chapter 6, **I/O Operations**, describes the mailbox data structure, the operation of the mailbox, interrupt handling, and the I/O registers.

- Chapter 7, CPU Module Registers, lists the LSB required and CPUspecific registers, and provides bit-level functional descriptions of each register.

- Chapter 8, **Initialization**, gives an overview of the CPU module initialization, describes the methods and process of initialization, system configuration, and bootstrapping of the operating system.

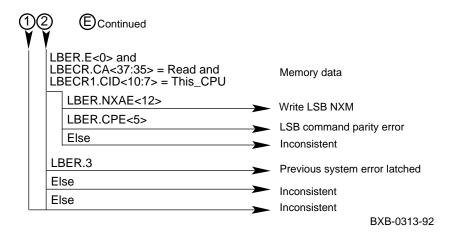

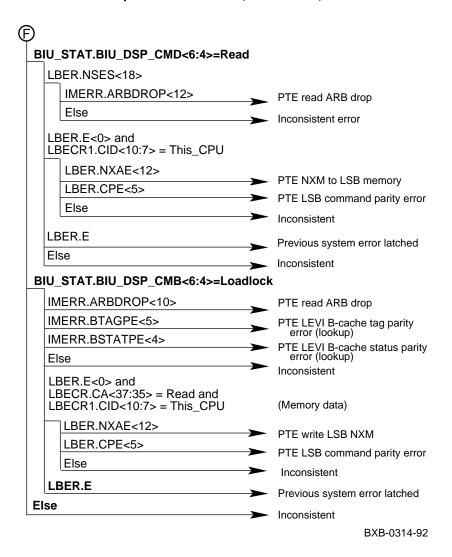

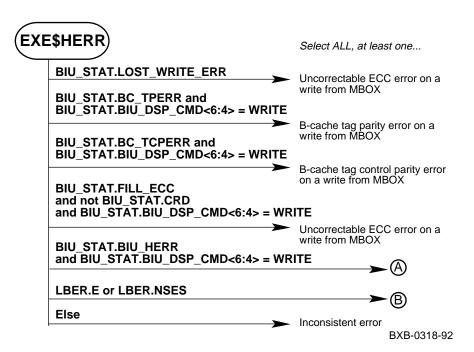

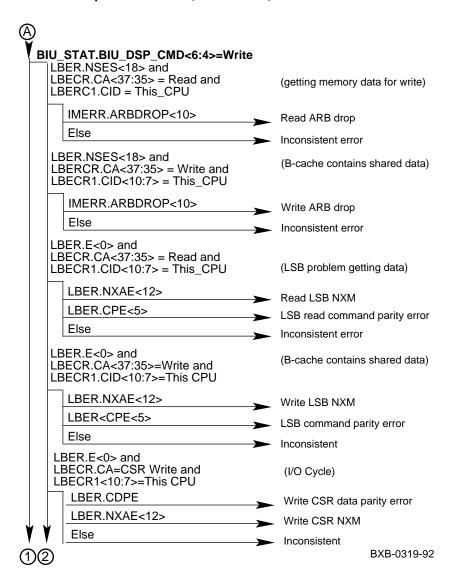

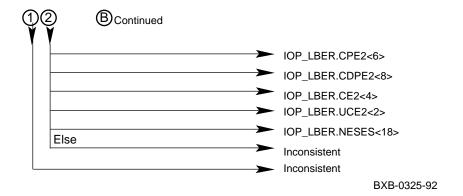

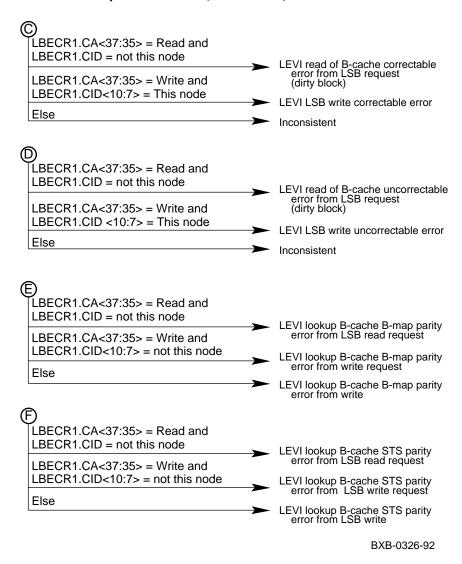

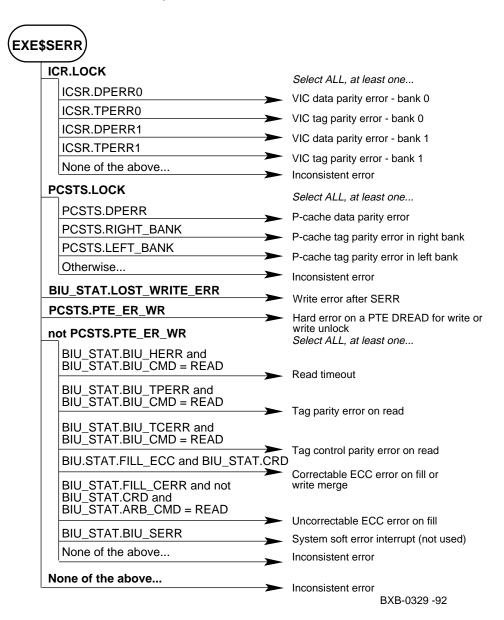

- Chapter 9, **Error Handling**, describes how the KA7AA module handles various types of errors. It discusses error analysis and recovery, machine check exceptions, and sources of error interrupts. Parse trees included in this chapter help isolate errors to particular causes.

## **Conventions Used in This Document**

#### **Results and Operations**

Results of operations termed UNPREDICTABLE must not be used by software.

Operations termed UNDEFINED do not cause the processor to hang, that is, reach a state from which there is no transition to a normal state of instruction execution. Nonprivileged software cannot invoke UNDEFINED operations.

#### **Register and Bit Designations**

Certain conventions are followed in register descriptions and in references to bits and bit fields:

- Registers are referred to with their mnemonics, such as VMAR register. The full name of a register (for example, VIC Memory Address Register) is spelled out only at the top of the register description page, or when the register is first introduced.

- Acronyms are used in register description tables to indicate the access type of the bit(s).

| Acronym | Access Type                                                                                                                                                                                                                |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RC      | Read to clear. The value is written by hardware and remains unchanged until read by software or microcode.                                                                                                                 |

| RO      | Read only. May be read by software, microcode, or hardware. Written by hardware. Software or microcode writes are ignored.                                                                                                 |

| R/W     | Read/write. May be read and written by software, microcode, or hardware.                                                                                                                                                   |

| R0      | Reads as zero. Read only. Writes are ignored.                                                                                                                                                                              |

| WO      | Write only. May be written by software or microcode. It is read by hardware. Reads by software or microcode return an unpredictable value.                                                                                 |

| W1C     | Write 1 to clear. The value may be read by software or microcode. Software or microcode writes of 1 to the position cause hardware to clear the bit. Software or microcode writes of 0 do not modify the state of the bit. |

| W1S     | Write 1 to set. May be read and written by software, microcode, or hardware. Set by software or microcode with a write of 1.                                                                                               |

Bits and fields are enclosed in angle brackets. For example, bit <31>;

bits <31:16>. For clarity of reference, bits are usually specified by their numbers or names enclosed in angle brackets adjacent to the register mnemonic, such as VMAR<31:11> or VMAR<ADDR>, which are equivalent designations.

When the value of a bit position is given explicitly in a register diagram, the information conveyed is as follows:

| Bit Value | Meaning                                                                                           |

|-----------|---------------------------------------------------------------------------------------------------|

| 0         | Reads as zero; ignored on writes.                                                                 |

| 1         | Reads as one; ignored on writes.                                                                  |

| X         | Does not exist in hardware. The value of the bit is UNPREDICTABLE on reads and ignored on writes. |

- Fields (in registers or data structures) noted as must be zero (MBZ)

must never be filled by software with a nonzero value. If the processor

encounters a nonzero value in an MBZ field, a Reserved Operand Exception occurs.

- Fields (in registers or data structures) noted as should be zero (SBZ) should be filled by software with a zero value. A nonzero value in an SBZ field produces UNPREDICTABLE results.

- The entry in the Type column of a register description table may include the initialization values of the bits. For example, entry "R/W, 0" indicates a read/write bit that is initialized to zero.

## **Documentation Titles**

Table 1 lists the books in the DEC 7000/10000 and VAX 7000/10000 documentation sets.

Table 1 DEC 7000/10000 and VAX 7000/10000 Documentation

|                                  | 7000 Systems | 10000 Systems |

|----------------------------------|--------------|---------------|

| Title                            | Order Number | Order Number  |

| Installation Kit                 | EK-7000B-DK  | EK-1000B-DK   |

| Site Preparation Guide           | EK-7000B-SP  | EK-1000B-SP   |

| Installation Guide               | EK-700EB-IN  | EK-100EB-IN   |

| Hardware User Information Kit    | EK-7001B-DK  | EK-1001B-DK   |

| Operations Manual                | EK-7000B-OP  | EK-1000B-OP   |

| Basic Troubleshooting            | EK-7000B-TS  | EK-1000B-TS   |

| Service Information Kit—VAX 7000 | EK-7002A-DK  | EK-1002A-DK   |

| Platform Service Manual          | EK-7000A-SV  | EK-1000A-SV   |

| System Service Manual            | EK-7002B-SV  | EK-1002A-SV   |

| Pocket Service Guide             | EK-7000A-PG  | EK-1000A-PG   |

| Advanced Troubleshooting         | EK-7001A-TS  | EK-1001A-TS   |

Table 1 DEC 7000/10000 and VAX 7000/10000 Documentation (Continued)

| Title                                              | 7000 Systems<br>Order Number | 10000 Systems<br>Order Number |

|----------------------------------------------------|------------------------------|-------------------------------|

| Reference Manuals                                  |                              |                               |

| Console Reference Manual                           | EK-70C0B-TM                  |                               |

| KA7AA CPU Technical Manual                         | EK-KA7AA-TM                  |                               |

| KN7AA CPU Technical Manual                         | EK-KN7AA-TM                  |                               |

| MS7AA Memory Technical Manual                      | EK-MS7AA-TM                  |                               |

| I/O System Technical Manual                        | EK-70I0A-TM                  |                               |

| Platform Technical Manual                          | EK-7000A-TM                  |                               |

| Upgrade Manuals                                    |                              |                               |

| KA7AA CPU Installation Card                        | EK-KA7AA-IN                  |                               |

| KN7AA CPU Installation Card                        | EK-KN7AA-IN                  |                               |

| MS7AA Memory Installation Card                     | EK-MS7AA-IN                  |                               |

| KZMSA Adapter Installation Guide                   | EK-KXMSX-IN                  |                               |

| DWLMA XMI PIU Installation Guide                   | EK-DWLMA-IN                  |                               |

| DWMBB VAXBI PIU Installation Guide                 | EK-DWMBB-IN                  |                               |

| H7237 Battery PIU Installation Guide               | EK-H7237-IN                  |                               |

| H7263 Power Regulator Installation Card            | EK-H7263-IN                  |                               |

| Futurebus+ PIU Installation Guide                  | EK-DWLAA-IN                  |                               |

| BA654 DSSI Disk PIU Installation Guide             | EK-BA654-IN                  |                               |

| BA655 SCSI Disk and Tape PIU Installation<br>Guide | EK-BA655-IN                  |                               |

| Removable Media Installation Guide                 | EK-TFRRD-IN                  |                               |

# **CPU Module Overview**

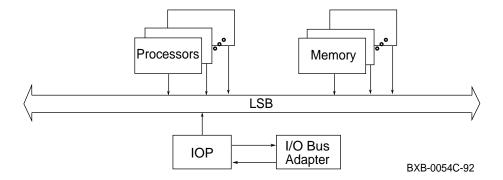

The KA7AA CPU module is designed around the NVAX+ microprocessor chip (P/N DC262) and communicates with main memory and I/O subsystems by way of the LSB bus. Figure 1-1 shows how the KA7AA CPU module fits in a VAX computer system based on the LSB bus.

Figure 1-1 Block Diagram of a VAX 7000 or VAX 10000 System

The CPU module supports the VAX base instruction group of 242 instructions and associated data types, an address space of 4 gigabytes, and provides full memory management.

A floating-point accelerator and a three-level hierarchical instruction and data cache structure allow the CPU module to achieve a minimum scalar single-CPU performance of more than 20 times that of a VAX 11/780 on an average workload.

The CPU module includes VAX-compatible macrocoded console firmware. Microcode and on-board ROMs permit booting from supported devices and provide self-test diagnostics on power-up.

A multiprocessor VAX 7000 or VAX 10000 system can be configured with up to six CPU modules. All backplane slots except slot 8, which is dedicated to the IOP module, can be used interchangeably with memory modules, allowing an array of configurations tailored to specific application requirements. It is strongly recommended, however, that the first CPU module be placed in slot 0.

The KA7AA CPU module is comprised of three major sections:

- CPU chip (NVAX+)

- Backup cache (B-cache)

- LSB interface (LEVI)

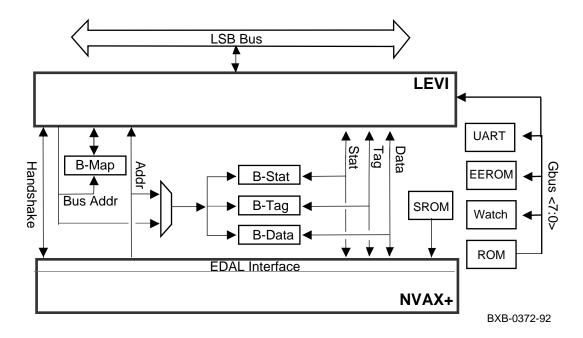

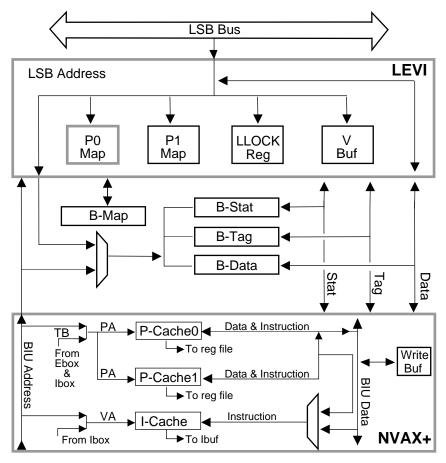

Figure 1-2 shows the major sections of the CPU module.

Figure 1-2 KA7AA CPU Module Block Diagram

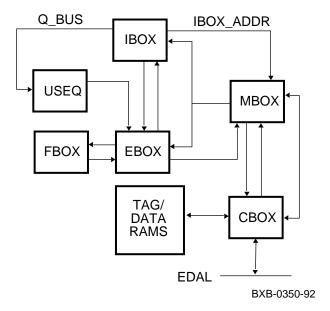

# 1.1 NVAX+ CPU Chip

The NVAX+ processor is a single-chip macropipelined implementation of the VAX architecture and the VAX base instruction group. It is partitioned into five functional units, or boxes, as listed in Table 1-1.

Table 1-1 **NVAX+ CPU Chip Functional Units**

| NVAX+ Unit | Functional Description                                                                                                                                                                                 |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ibox       | <b>Instruction box.</b> Prefetches, decodes, parses, and queues VAX instructions for execution.                                                                                                        |  |  |

| Ebox       | <b>Execution box</b> . Executes, together with the microsequencer, instructions received from the Ibox.                                                                                                |  |  |

| Fbox       | <b>Floating-point accelerator box.</b> Executes floating-point and integer multiply VAX instructions received from the Ebox.                                                                           |  |  |

| Mbox       | <b>Memory management box.</b> Performs all virtual to physical address translations, for the Ibox and Ebox. The Mbox also handles Cbox requests for cache fills and invalidates for the primary cache. |  |  |

| Cbox       | <b>Cache control box</b> . Initiates access to the backup cache (B-cache) and issues memory requests.                                                                                                  |  |  |

#### The NVAX+ CPU chip includes:

- Translation buffer: 96 entries, fully associative

- Virtual instruction cache (VIC): Two Kbytes, direct-mapped, virtually addressed, I-stream only

- Primary cache (P-cache): Eight Kbytes, 2-way set associative, physically addressed, write through, mixed I-stream and D-stream, 32-byte block and fill size

- Control store: 1600 61-bit microwords

- EDAL interface: Cache and memory subsystem interface

The macroinstruction pipelined design of the NVAX+ CPU chip allows significant parallel processing. NVAX+ pipelines macroinstruction decode and operand fetch with macroinstruction execution. Pipeline efficiency is increased by queuing up instruction information and operand values for later use by the execution unit. Thus, when the macropipeline is operating smoothly, the instruction unit (Ibox), which parses instructions and fetches operands, is running several macroinstructions ahead of the execution unit (Ebox). Branch predictions allow quicker execution of loops in software. Outstanding writes to registers or memory locations are kept in a scoreboard to ensure that data is not read before it has been written.

## 1.2 Backup Cache (B-Cache)

The external backup cache (B-cache) is a 4-Mbyte superset of the P-cache. It is a physically addressed, direct mapped, write back, mixed I-stream and D-stream cache with a block and fill size of 64 bytes. It consists of three sets of RAMs:

B-data

B-tag

B-stat

Each block of data (B-data) has a tag (B-tag) and three status bits (B-stat) associated with it. The status bits are Valid, Dirty, and Shared.

The B-cache has controllable data RAM access time. The CPU module supports cache access times of 2, 3, and 4 times the NVAX+ chip cycle time.

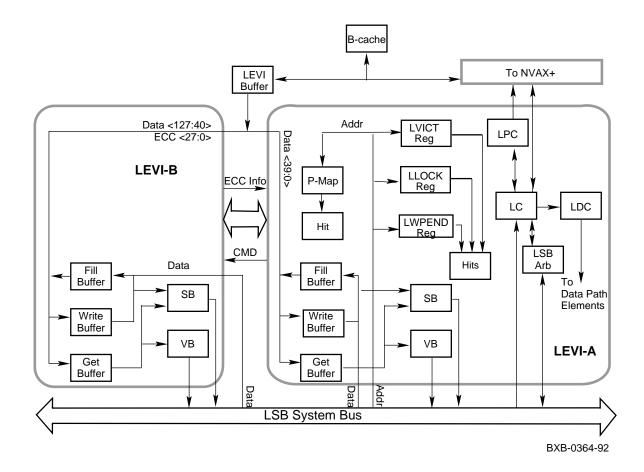

## 1.3 LSB Interface (LEVI)

The interface to the LSB bus is called LEVI, which consists of two chips: LEVI-A and LEVI-B. LEVI-A contains most LSB required registers, implements all command execution, LSB arbitration, and B-cache manipulation functions. It also contains a P-cache backmap (P-map) to allow the CPU to do invalidate filtering and to make intelligent update vs. invalidate decisions in response to LSB write traffic. LEVI-A uses an external RAM structure to implement a backmap of the B-cache to filter bus traffic from the B-cache while still maintaining cache coherence.

LEVI-B completes the 128-bit data path between the NVAX+ and the LSB bus. An 8-bit communication bus between LEVI-A and LEVI-B provides a path that allows LEVI-B to perform look-aside ECC checking on incoming memory traffic.

# Chapter 2

# **CPU Chip**

The NVAX+ CPU chip is the central processor of the KA7AA CPU module. It executes the VAX base instruction group and provides full VAX memory management. This chapter provides a summary of the architectural features and functional elements of the NVAX+ CPU chip. Sections include:

- Data types

- Instruction set

- Address space

- Memory management

- Exceptions and interrupts

- System control block

- Process structure

- Functional partitions

- General purpose registers

- · Internal processor registers

For more information on some of these topics, consult the *VAX Architecture Reference Manual*.

## 2.1 Data Types

The NVAX+ CPU chip supports the following subset of VAX data types:

Byte

Word

Longword

Quadword

Variable-length bit field

**Character string**

Absolute queues

Self-relative queues

**D\_floating**

F\_floating

**G\_floating**

The remaining VAX data types (octaword, H\_floating, trailing numeric string, leading separate numeric string, and packed decimal string) are supported by macrocode emulation.

## 2.2 Instruction Set

The NVAX+ hardware supports the following instruction classes:

Integer arithmetic and logical

Address

Variable-length bit field

Control

Procedure call

Miscellaneous

Queue

Character string

Operating system support

D\_floating

F\_floating

**G\_floating**

A subset of the VAX instruction group is emulated by NVAX+ microcode. See the *VAX Architecture Reference Manual* for detailed descriptions of the VAX instruction set.

2.3

## 2.4 Address Space

The memory space that a programmer uses is a single logical structure of contiguous pages. It is called "virtual memory" and is referenced in virtual address space. The memory space that the operating system allocates to a process is a structure of noncontiguous pages called "physical memory" and is referenced in the physical address space. The operating system uses the page mapping scheme because in a multiuser and multitasking environment no available block in physical memory may be large enough to accommodate a block of contiguous pages generated in virtual memory.

## 2.4.1 Virtual Address Space

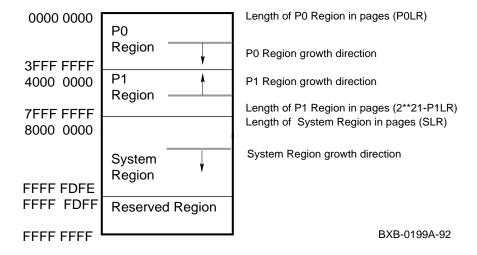

Software can reference a 32-bit virtual address. This address width allows access to a virtual address space of 4 gigabytes (2\*\*32 locations). The virtual address space is divided into two sections, process space and system space. The process space is further partitioned into two regions, P0 and P1. All the virtual address space except a reserved region in the system space is accessible to software. Figure 2-1 shows the virtual address space layout.

*NOTE: NVAX+ implements the VAX extended system region address space. The extension allows the chip to address 2<sup>22</sup>-1 pages of system space.*

Figure 2-1 Virtual Address Space Layout

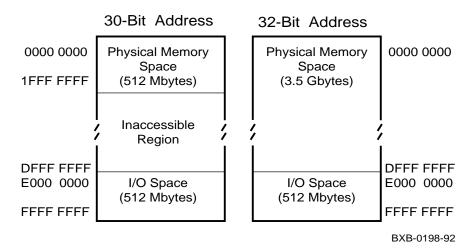

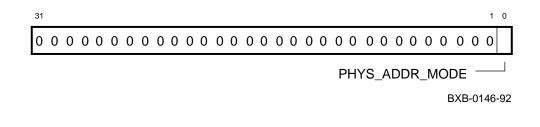

## 2.4.2 Physical Address Space

The NVAX+ CPU generates 32-bit physical addresses. This address width can access 4 gigabytes of physical address space. Memory space occupies the first seven-eighths (3.5 Gbytes) of the physical address space. I/O space occupies the last one-eighth (512 Mbytes) of the physical address space and can be distinguished from memory space by the fact that bits <31:29> of the physical address are all ones.

The NVAX+ CPU chip can also run in a 30-bit address mode if selected by the programmer. In this mode the NVAX+ CPU chip can reference only

one gigabyte of total address space, evenly divided into memory space and I/O space. Figure 2-2 shows the physical address space layouts.

Figure 2-2 Physical Address Space Layouts

During power-up, microcode configures the NVAX+ CPU chip to generate 30-bit physical addresses. Operating system initialization code can reconfigure the CPU module to generate either 30-bit or 32-bit physical addresses by writing to the Mode bit (<0>) in the PAMODE register (IPR231).

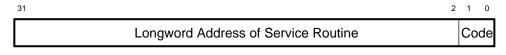

# 2.5 Memory Management

Memory management is the translation of virtual addresses (contiguous page addresses used by the programmer) into physical addresses (noncontiguous page addresses in physical memory space). The central processor extracts the virtual page number (VPN) from the virtual address (bits <29:9>) and generates a page frame number (PFN), which makes up bits <31:9> of the physical address. The physical address is then formed by appending bits <8:0> of the virtual address (address of the byte within the page) to the PFN.

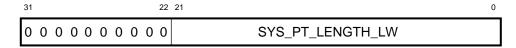

## 2.5.1 System Space Address Translation

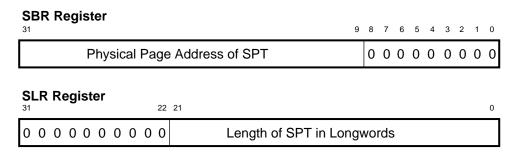

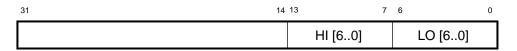

A virtual address in system space is mapped by the system page table (SPT), which is defined by the System Base Register (SBR) and the System Length Register (SLR). The SBR register contains the page-aligned physical address of the SPT. The SLR contains the size of the SPT in longwords, that is, the number of page table entries (PTE). The PTE addressed by the SBR register maps the first page of the system virtual address space, that is, virtual byte address 8000 0000 (hex). Figure 2-3 shows the SBR and SLR registers.

NOTE: When the CPU module is configured to generate 30-bit physical addresses, SBR<31:30> are ignored.

Figure 2-3 SBR and SLR Registers

BXB-0178-92

### 2.5.2 Process Space Address Translation

A virtual address with bit <31>=0 is an address in the process virtual address space. Process space is divided into two equal sized, separately mapped regions. If virtual address bit <30>=0, the address is in region P0. If virtual address bit <30>=1, the address is in region P1.

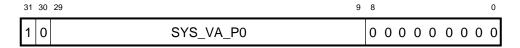

### 2.5.2.1 PO Region Address Translation

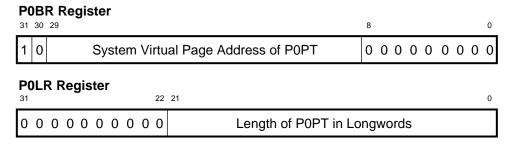

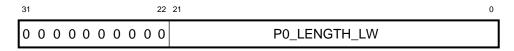

The P0 region of the address space is mapped by the P0 page table (P0PT), which is defined by the P0 Base Register (P0BR) and the P0 Length Register (P0LR). The P0BR register contains the system page-aligned virtual address of the P0 page table. The P0LR register contains the size of the P0PT in longwords, that is, the number of PTEs. The PTE addressed by the P0BR register maps the first page of the P0 region of the virtual address space, that is, the virtual byte address 0. Figure 2-4 shows the P0BR and P0LR registers.

Figure 2-4 POBR and POLR Registers

BXB-0195-92

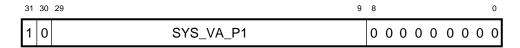

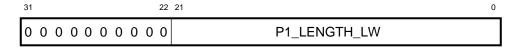

### 2.5.2.2 P1 Region Address Translation

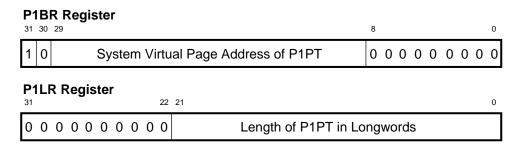

The P1 region of the address space is mapped by the P1 page table (P1PT), which is defined by the P1 Base Register (P1BR) and the P1 Length Register (P1LR). Because P1 space grows toward smaller addresses, and because a consistent hardware interpretation of the base and length register-

sis desirable, the P1BR register and the P1LR register describe the portion of P1 space that is not accessible. Note that the P1LR register contains the number of nonexistent PTEs. The P1BR contains the page-aligned virtual address of what would be the PTE for the first page of P1, that is, virtual byte address 4000 0000 (hex). The address in the P1BR register is not necessarily an address in system space, but all the addresses of PTEs are in system space. Figure 2-5 shows the P1BR and P1LR registers.

Figure 2-5 P1BR and P1LR Registers

BXB-0195A-92

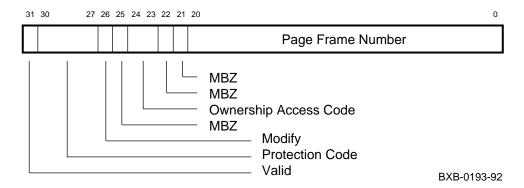

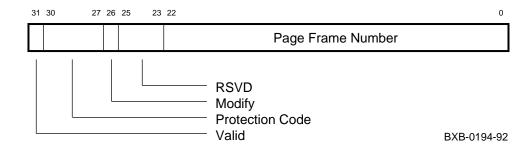

## 2.5.3 Page Table Entry Format

When the CPU module is configured to generate 30-bit physical addresses, it interprets PTEs in the 21-bit PFN format shown in Figure 2-6.

Figure 2-6 PTE Format (21-Bit PFN)

If the CPU module is configured to generate 32-bit physical addresses, it interprets PTEs in the 25-bit PFN format shown in Figure 2-7.

Figure 2-7 PTE Format (25-Bit PFN)

Note that bits <24:23> of the 25-bit PFN format are ignored by the NVAX+ CPU chip.

#### 2.5.4 Translation Buffer

The NVAX + CPU chip implements a 96-entry, fully associative, fast access translation buffer to minimize memory accesses when repeatedly referencing the same memory pages. Each entry stores a PTE for translating virtual addresses to physical addresses in either process space or system space. The translation buffer caches the PTEs of recent virtual address translations. It is accessed in parallel with each memory reference.

Each translation buffer entry is divided into two parts: a 26-bit tag register and a 29-bit PTE register. The tag register is used to store the VPN of the virtual page that the corresponding PTE register maps. The tag register also contains a valid bit (TBV) that indicates a valid VPN in the tag.

During virtual-to-physical address translation, the contents of the 96 tag registers are compared with the VPN field (bits <31:9>) of the virtual address of the reference. If there is a match with one of the tag registers and the TBV bit indicates a valid entry, the translation buffer sends the correct physical address contained in the corresponding PTE register to the cache. If no match occurs, the PTE that maps the page is fetched from memory through the normal memory access stages (P-cache, B-cache, and then main memory) and the translation buffer is updated by replacing the entry at the location indicated by the replacement pointer.

Translation buffer entries are replaced using a not-last-used (NLU) algorithm. This algorithm guarantees that the replacement pointer is not pointing at the last translation buffer entry to be used. This is accomplished by rotating the replacement pointer to the next sequential translation buffer entry. Both D-stream and I-stream references can cause the NLU algorithm to execute.

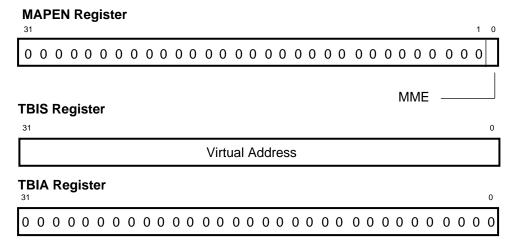

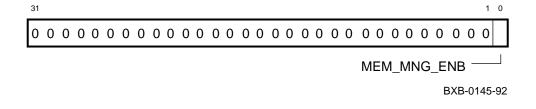

## 2.5.5 Memory Management Control

Three processor registers control memory management:

- Memory Management Enable Register (MAPEN), IPR56

- Translation Buffer Invalidate Single Register (TBIS), IPR58

- Translation Buffer Invalidate All Register (TBIA), IPR57

Bit <0> of the MAPEN register enables memory management if set to a one and disables memory management if written with a zero. The MAPEN register is written to with a Move To Processor Register (MTPR) instruction. It is read with a Move From Processor Register (MFPR) instruction.

The TBIS register controls single-entry invalidation in the translation buffer. Entries that map a particular virtual address are invalidated by writing the virtual address to the TBIS register using the MTPR instruction.

The TBIA register controls total translation buffer invalidation. Writing a zero into the TBIA register invalidates the entire translation buffer. Figure 2-8 shows the three memory control registers.

CAUTION: All affected process pages must be invalidated in the translation buffer whenever software changes one of the following:

- A valid PTE for the system or the current process region

- A system PTE that maps any part of the current process page table

Otherwise, address translations point to wrong locations in memory.

Figure 2-8 Memory Management Control Registers

BXB-0201-92

The base and length of the P0, P1, and S0 page tables are changed by writing the appropriate address or length to the P0BR, P0LR, P1BR, P1LR, SBR, or SLR register. The entire translation buffer is flushed when a change is made to any of these six registers.

When a process context is loaded with the Load Process Context (LDPCTX) instruction, all translation buffer entries that map process space pages are automatically invalidated. System-space mappings are preserved.

To determine if the translation buffer contains a valid translation for a particular virtual page, write a virtual address within that page to TBCHK using an MTPR instruction. If the translation buffer contains a valid translation for the page, the condition code V bit (PSL<1>) would be set.

A full invalidation of the translation buffer, whether performed with an explicit write to the TBIA register, or as an implied clear due to writes to the MAPEN register or any base/length register, resets the NLU pointer to the first location in the translation buffer.

NOTE: The contents of the translation buffer are UNPREDICTABLE whenever memory management is disabled. The entire translation buffer contents should be flushed before memory management is enabled. The console firmware performs this function as the system is booted.

# 2.6 Exceptions and Interrupts

At certain times during the operation of a system, events may occur that break the explicit flow of instructions in the current process and require execution of external software routines. Two types of events can cause such a break: exceptions and interrupts.

An exception is an event related to the currently executing process and invokes a software routine in the context of the current process. Exception handlers are often system routines, not process routines.

An interrupt is an event caused by some activity outside the current process and invokes a software routine outside the context of the current process.

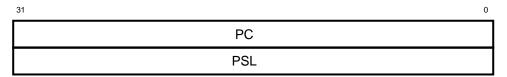

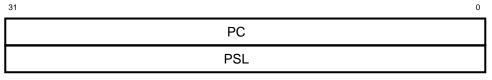

The CPU chip reports exceptions and interrupts by constructing a frame on the stack and then dispatching to the service routine through an event-specific vector in the system control block (SCB, Section 2.7). The minimum stack frame for any interrupt and exception is a program counter/processor status longword (PC/PSL) pair, as shown in Figure 2-9.

Figure 2-9 Minimum Stack Frame

BXB-0188-92

The minimum stack frame is used for all interrupts. Certain exceptions expand the stack frame by pushing additional parameters on the stack above the PC/PSL pair, as shown in Figure 2-10.

Figure 2-10 Expanded Stack Frame

| 31 |             | 0 |

|----|-------------|---|

|    | Parameter n |   |

|    |             |   |

|    | Parameter 1 |   |

|    | PC          |   |

|    | PSL         |   |

BXB-0191-92

## 2.6.1 Exceptions

There are three types of exceptions:

- Traps

- Faults

- Aborts

A **trap** occurs at the end of an instruction. Therefore, the PC saved on the stack is the address of the next instruction that would normally have been executed had the trap not occurred.

A **fault** occurs during the execution of an instruction and leaves the registers and memory in a consistent state, so that eliminating the fault condition and restarting the instruction gives correct results. The PC saved on the stack points to the instruction that faulted.

An **abort** occurs during the execution of an instruction and leaves the value of the registers and memory UNPREDICTABLE, so that the instruction cannot be restarted, completed, simulated, or undone. In most cases the NVAX+ microcode attempts to convert an abort into a fault by restoring the state preceding the start of the instruction that caused the abort.

This section lists VAX standard exceptions and discusses their implementation on the KA7AA CPU module. The standard exceptions are described in the *VAX Architecture Reference Manual*.

The VAX architecture recognizes six categories of exceptions. Table 2-1 lists the types of exceptions in each category. Specific characteristics are found in the following exceptions implemented on the NVAX+ chip:

- Arithmetic

- · Memory management

- Emulated instruction

- System failure

Table 2-1 KA7AA Module Exceptions

| Exception Category               | Туре                                                                                                                                                  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Arithmetic traps/faults          | Integer overflow trap Integer divide-by-zero trap Subscript range trap Floating overflow fault Floating divide by zero fault Floating underflow fault |  |

| Memory management exceptions     | Access control violation fault (ACV)<br>Translation not valid fault (TNV)<br>Modify fault (M)                                                         |  |

| Operand reference exceptions     | Reserved addressing mode fault<br>Reserved operand fault or abort                                                                                     |  |

| Instruction execution exceptions | Emulated instruction fault<br>Extended function (XFC) fault<br>Change-mode trap<br>Breakpoint fault                                                   |  |

| Tracing exceptions               | Trace fault                                                                                                                                           |  |

| System failure exceptions        | Kernel stack not valid abort<br>Interrupt stack not valid fault<br>Console error halt<br>Machine check abort                                          |  |

## 2.6.1.1 Arithmetic Exceptions

Arithmetic exceptions are detected during the execution of integer or floating-point arithmetic instructions. Figure 2-11 shows the arithmetic exception stack frame.

Figure 2-11 Arithmetic Exception Stack Frame

| 31 |           | 0 |

|----|-----------|---|

|    | Type Code |   |

|    | PC        |   |

|    | PSL       |   |

BXB-0189-92

The exception is reported as either a trap or a fault, depending on the specific event. Table 2-2 shows the encoding of arithmetic exceptions.

Table 2-2 Arithmetic Exception Codes

| Code (Hex) | Туре  | Exception               |

|------------|-------|-------------------------|

| 1          | Trap  | Integer overflow        |

| 2          | Trap  | Integer divide-by-zero  |

| 7          | Trap  | Subscript range         |

| 8          | Fault | Floating overflow       |

| 9          | Fault | Floating divide-by-zero |

| A          | Fault | Floating underflow      |

# 2.6.1.2 Memory Management Exceptions

Memory management exceptions are detected during a memory reference and are always reported as faults. The memory management exceptions and the associated SCB vectors are listed in Table 2-3.

**Table 2-3** Memory Management Exceptions

| Exception                                                                   | SCB Vector (Hex) |

|-----------------------------------------------------------------------------|------------------|

| Access control violation (ACV) Translation not valid (TNV) Modify fault (M) | 20<br>24<br>3C   |

All memory management exceptions push the same frame on the stack, as shown in Figure 2-12.

Figure 2-12 Memory Management Exception Stack Frame

| 31 |                                           | 2 1 0 |

|----|-------------------------------------------|-------|

|    | MBZ                                       | MPL   |

|    | Some Virtual Address in the Faulting Page |       |

|    | PC                                        |       |

|    | PSL                                       |       |

BXB-0190-92

The M, P, and L bits of the parameter pointed to by the stack pointer reflect bits <2:0> of the MMESTS register, which are described in Table 2-38.

## 2.6.1.3 Emulated Instruction Exceptions

The NVAX+ chip implements the VAX base instruction group in hardware and provides microcode support for macrocode emulation of certain other instructions. Two types of emulation exceptions depend on the state of PSL<FPD>. If FPD is zero at the beginning of the instruction, then the exception is reported through SCB vector C8 (hex) as a trap, with the stack frame shown in Figure 2-13.

Figure 2-13 Emulated Instruction Trap Stack Frame

| 31 |             | 0 |

|----|-------------|---|

|    | Opcode      |   |

|    | Old PC      |   |

|    | Specifier 1 |   |

|    | Specifier 2 |   |

|    | Specifier 3 |   |

|    | Specifier 4 |   |

|    | Specifier 5 |   |

|    | Specifier 6 |   |

|    | Specifier 7 |   |

|    | Specifier 8 |   |

|    | New PC      |   |

|    | PSL         |   |

BXB-0192-92

Table 2-4 describes the emulated instruction stack frame parameters.

Table 2-4 Emulated Instruction Trap Stack Frame Parameters

| Parameter  | Function                                                                                                                  |

|------------|---------------------------------------------------------------------------------------------------------------------------|

| Opcode     | Zero-extended opcode of the emulated instruction.                                                                         |

| Old PC     | Program counter of the opcode of the emulated instruction.                                                                |

| Specifiers | Address of the specified operand for specifiers of either access type write (.wx) or address (.ax).                       |

|            | Operand value for specifiers of access type read (.rx).                                                                   |

|            | For read-type operands whose size is smaller than a longword, the remaining bits are UNPREDICTABLE.                       |

|            | For those instructions that do not have eight specifiers, the remaining specifier longwords contain UNPREDICTABLE values. |

| New PC     | Program counter of the instruction following the emulated instruction.                                                    |

| PSL        | PSL saved at the time of the trap.                                                                                        |

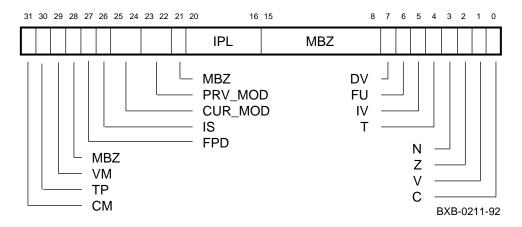

If PSL<FPD> (see Figure 2-19) is one at the beginning of the instruction, then the exception is reported through SCB vector CC (hex) as a fault, with the stack frame as shown in Figure 2-14. In this case, PC is the opcode of the emulated instruction.

Figure 2-14 Emulated Instruction Fault Stack Frame

BXB-0188-92

## 2.6.1.4 System Failure Exceptions

A machine check exception is reported through SCB vector 04 (hex) when the NVAX+ chip detects an error condition. The frame pushed on the stack for a machine check indicates the type of error and provides internal state information that may help identify the cause of the error. Machine check exceptions are discussed at length in Chapter 9 (Error Handling).

In certain microcode flows, the NVAX+ microcode may detect an inconsistency in internal state, a kernel-mode HALT, or a system reset. In these instances, the microcode initiates a hardware restart sequence which passes control to the console program. This process is called console halt.

When a console halt occurs, the NVAX+ microcode saves the current CPU state, partially initializes the CPU, and passes control to the console program at the physical address contained in the CHALT register.

During a hardware restart sequence, the stack pointer is saved in the appropriate stack pointer (0 through 4), the current PC is saved in IPR42 (SAVPC register), and the current PSL, halt code, and validity flag are

saved in IPR43 (SAVPSL register). Console halts are discussed at length in Chapter 9 (Error Handling).

## 2.6.2 Interrupts

The interrupt section receives interrupt requests from both internal and external sources. When an interrupt request is generated, the NVAX+ chip compares the request with the current IPL of the CPU. If the new request is of higher priority, an internal request is generated. At the completion of the current instruction, or at selected points during the execution of interruptable instructions, a microcode interrupt handler is invoked to process the request. The microcode handler determines the highest priority interrupt, updates the IPL, pushes a PC/PSL pair on the stack, and dispatches to a macrocode interrupt handler through the appropriate location in the SCB.

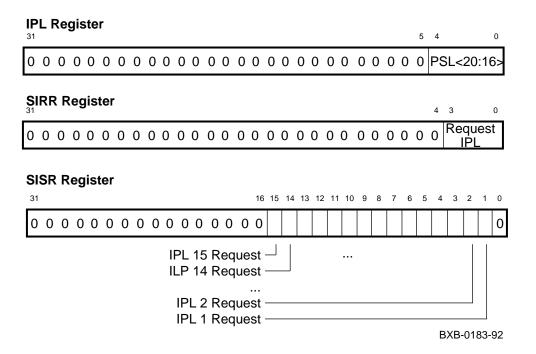

The interrupt system is controlled by three IPRs:

- Interrupt Priority Level Register (IPL), IPR18

- Software Interrupt Request Register (SIRR), IPR20

- Software Interrupt Summary Register (SISR), IPR21

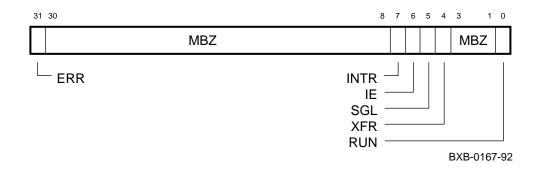

The IPL register is used for loading the interrupt priority level field (IPL<4:0>) into PSL<20:16>. The SIRR register is used for creating software interrupt requests. The SISR register records pending software interrupt requests at levels 1 through 15. Figure 2-15 shows the three interrupt control registers.

Figure 2-15 Interrupt Control Registers

### 2.6.2.1 External Interrupt Requests

NVAX+ inputs six external interrupt signals as IRQ\_H<3:0>, HALT\_H, and ERR\_H. These signals request general-purpose interrupts at the following IPLs:

- HALT\_H: The assertion of HALT\_H causes the CPU to enter the console at IPL 1F (hex) at the next macroinstruction boundary. The interrupt is not gated by the current IPL, and always results in console entry, even if the IPL is already 1F (hex). Note that unlike normal interrupts, which cause a PC/PSL pair to be pushed on the interrupt stack, HALT\_H interrupts store the current PC/PSL and halt code in the SAVPC and SAVPSL processor registers. Console halts are discussed at length in Chapter 9 (Error Handling).

- ERR\_H: The assertion of ERR\_H indicates that an error has been detected in the system environment. This results in the dispatch of the interrupt to the operating system at IPL 1D (hex) through SCB vector 60 (hex).

- IRQ<3:0>: Device interrupts resulting in dispatch of the interrupt to the operating system at IPL 14–17 (hex) through SCB vector D0, D4, D8, or DC (hex).

Table 2-5 shows the external interrupt request levels and the associated SCB vectors. Interrupt routines at the specified SCB acknowledge the interrupt.

Table 2-5 External Interrupt Requests

| Interrupt<br>Request | Req<br>(Hex) | uest IPL<br>(Decimal) | Interrupt Condition                                                                       | SCB Vector<br>(Hex) |

|----------------------|--------------|-----------------------|-------------------------------------------------------------------------------------------|---------------------|

| HALT_H               | 1F           | 31                    | Ctrl/P typed at the console,<br>LCNR <nhalt> set, node reset,<br/>or system reset</nhalt> | Console             |

| ERR_H                | 1D           | 29                    | Hardware error                                                                            | 60                  |

| IRQ<3>               | 17           | 23                    | Device interrupt                                                                          | DC                  |

| IRQ<2>               | 16           | 22                    | Device interrupt                                                                          | D8                  |

| IRQ<1>               | 15           | 21                    | Device interrupt                                                                          | D4                  |

| IRQ<0>               | 14           | 20                    | Device interrupt                                                                          | D0                  |

## 2.6.2.2 Internal Interrupt Requests

The Cbox, Ibox, and Mbox report error conditions by asserting internal interrupt request signals. Table 2-6 gives the interrupt requests caused by internal hard and soft errors.

Table 2-6 Internal Interrupt Requests

| Interrupt Request | Request IPL<br>(Hex) (Decimal) |    | SCB Vector<br>(Hex) |

|-------------------|--------------------------------|----|---------------------|

| H_ERR             | 1D                             | 29 | 60                  |

| S_ERR             | 1A                             | 26 | 54                  |

The performance monitoring facility requests an interrupt at IPL 1B (hex) when the performance counters become half full. This request is serviced entirely by microcode. It is cleared by writing to the appropriate interrupt service routine.

When the interval timer period expires (ICCS<6> is set), the interrupt is dispatched to the operating system at IPL 16 (hex) through SCB vector C0 (hex).

An architecturally defined software interrupt request causes an associated bit to be set in the SISR register. The request is dispatched to the operating system. The IPL of the SCB vector is implied by the interrupt request. Table 2-7 shows the association between an SISR register bit, request IPL, and SCB vector.

Table 2-7 Software Interrupt Requests

|              | Regi          | uest IPL  | SCB Vector |

|--------------|---------------|-----------|------------|

| SISR Bit Set | (Hex)         | (Decimal) | (Hex)      |

| <15>         | 0             | 15        | ВС         |

| <14>         | $0\mathrm{E}$ | 14        | B8         |

| <13>         | 0D            | 13        | <b>B4</b>  |

| <12>         | 0C            | 12        | B0         |

| <11>         | 0B            | 11        | AC         |

| <10>         | 0A            | 10        | A8         |

| <9>          | 09            | 09        | A4         |

| <8>          | 08            | 08        | A0         |

| <7>          | 07            | 07        | 9C         |

| <6>          | 06            | 06        | 98         |

| <5>          | 05            | 05        | 94         |

| <4>          | 04            | 04        | 90         |

| <3>          | 03            | 03        | 8C         |

| <2>          | 02            | 02        | 88         |

| <1>          | 01            | 01        | 84         |

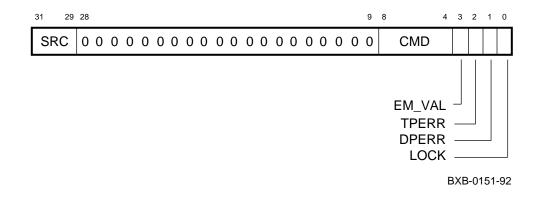

# 2.7 System Control Block

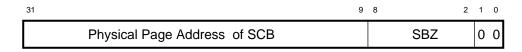

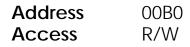

The system control block (SCB) is a page containing vectors for servicing interrupts and exceptions. The SCB is pointed to by the 32-bit System Block Base Register (SCBB). Since the SCBB contains a 32-bit physical address, the SCB can reside anywhere in memory space. For optimum performance, the SCBB should contain a page-aligned address. Microcode forces longword alignment by clearing bits <1:0> of the new value before loading it into the SCBB register. Figure 2-16 shows the format of the SCBB register.

Figure 2-16 System Control Block Base Register

BXB-0185-92

NOTE: When When the CPU is in 30-bit physical address mode, SCBB<31:30> are ignored.

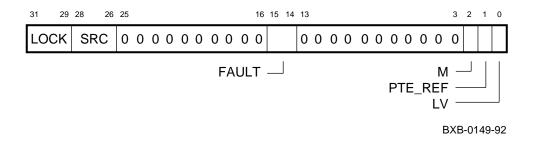

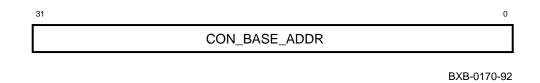

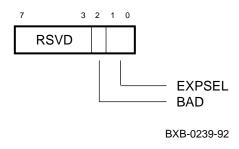

An SCB vector is an aligned longword in the SCB. The NVAX+ chip microcode dispatches interrupts and exceptions through the SCB vector, shown in Figure 2-17.

Figure 2-17 System Control Block Vector

BXB-0197-92

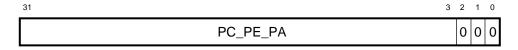

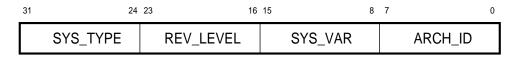

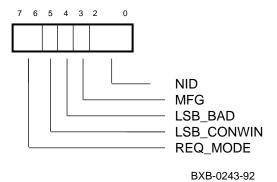

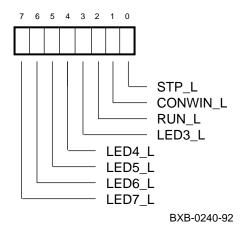

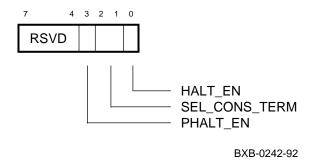

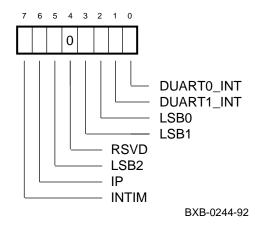

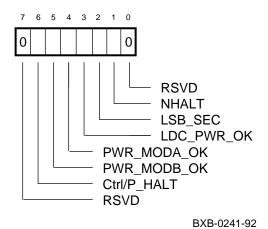

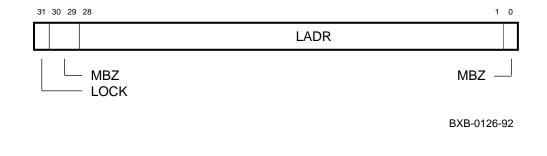

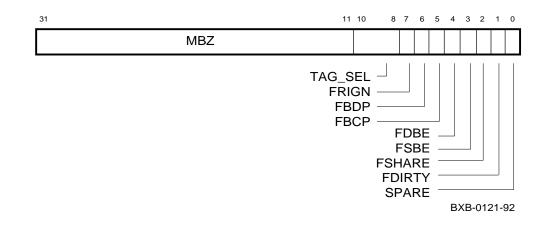

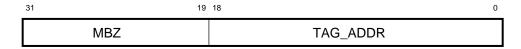

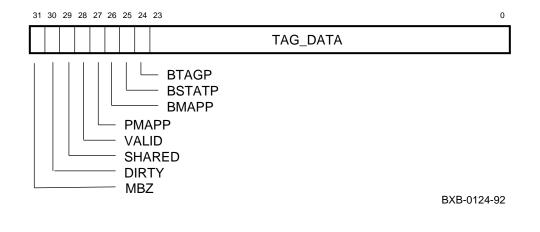

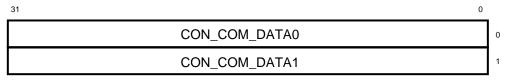

Table 2-8 describes the bit functions of the SCB vector.