# DZQ11 Asynchronous Multiplexer User's Guide

Copyright © 1984, 1987 by Digital Equipment Corporation

#### All Rights Reserved

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors herein.

#### Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation.

| d | ı | g | ij |  | а | ٠ | 774 |

|---|---|---|----|--|---|---|-----|

|---|---|---|----|--|---|---|-----|

DEC PDP RT

DECmate P/OS UNIBUS

DECUS Professional VAX

DECwriter Rainbow VMS

DIBOL RSTS VT

MASSBUS RSX Work Processor

### **CONTENTS**

|           |                                      | Page                              |

|-----------|--------------------------------------|-----------------------------------|

| CHAPTER 1 | GENERAL DESCRIPTION                  |                                   |

| 1.1       | INTRODUCTION                         | 1-1                               |

| 1.2       | PHYSICAL DESCRIPTION                 | 1-3                               |

| 1.2.1     | DZQ11 Configurations                 |                                   |

| 1.2.2     | Interface Cables                     | 1-6                               |

| 1.2.3     | Test Connectors                      | 1-6                               |

| 1.3       | SPECIFICATIONS                       | 1-8                               |

| 1.3.1     | Environmental                        | 1-8                               |

| 1.3.2     | Electrical                           | 1-8                               |

| 1.3.3     | Performance                          | 1-8                               |

| 1.3.3.1   | Interfaces                           | 1-8                               |

| 1.3.3.2   | Maximum Configurations               | 1-9                               |

| 1.3.3.3   | Throughput                           |                                   |

| 1.3.3.4   | Receivers                            |                                   |

| 1.3.3.5   | Transmitters                         | 1-9                               |

| 1.3.3.6   | Baud-Rate Generator                  | 1-9                               |

| 1.3.3.7   | Performance Summary                  | 1-10                              |

| 1.3.4     | Interrupts                           |                                   |

| 1.3.4.1   | Receiver-Done Interrupt              |                                   |

| 1.3.4.2   | Silo-Alarm Interrupt                 |                                   |

| 1.3.4.3   | Transmit Interrupt                   |                                   |

| CHAPTER 2 | INSTALLATION                         |                                   |

| 2.1       | SCOPE                                | 2-1                               |

| 2.2       | UNPACKING AND INSPECTION             |                                   |

| 2.3       | INSTALLATION PROCEDURE               |                                   |

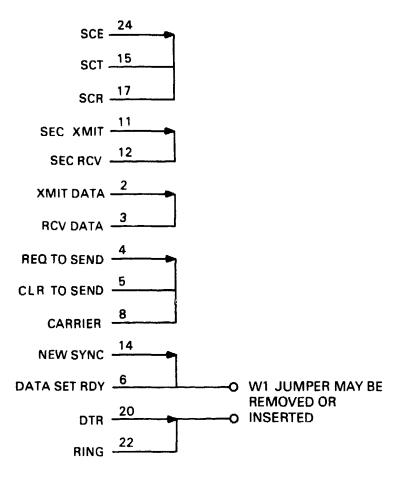

| 2.3.1     | Modem Control Jumpers                |                                   |

| 2.3.2     | Module Installation.                 |                                   |

| 2.3.3     | Testing DZQ11s in PDP-11 Systems     |                                   |

| 2.3.4     | Testing in MicroVAX Systems          |                                   |

| 2.4       | DEVICE ADDRESS ASSIGNMENTS           | 2-1 <i>5</i><br>2 <sub>-</sub> 15 |

| 2.5       | INTERRUPT VECTOR ADDRESS ASSIGNMENTS | 2-13                              |

| CHAPTER 3 | DEVICE REGISTERS                     |                                   |

| 3.1       | SCOPE                                | 3-1                               |

| 3.2       | DEVICE REGISTERS                     |                                   |

| 3.2.1     | Control and Status Register          |                                   |

| 3.2.2     | Receiver Buffer                      |                                   |

| 3.2.3     | Line Parameter Register              |                                   |

| 3.2.4     | Transmitter Control Register         |                                   |

| 3.2.5     | Modem Status Register                |                                   |

| 3.2.6     | Transmit Data Register               |                                   |

| CHAPTER 4  | PROGRAMMING                                                     |      |

|------------|-----------------------------------------------------------------|------|

| 4.1        | SCOPE                                                           |      |

| 4.2        | PROGRAMMING FEATURES                                            | 4-1  |

| 4.2.1      | Interrupts                                                      | 4-1  |

| 4.2.2      | Emptying the Silo                                               |      |

| 4.2.3      | Transmitting a Character                                        |      |

| 4.2.4      | Data Set Control                                                |      |

|            | FIGURES                                                         |      |

| Figure No. | Title                                                           | Page |

| 1-1        | M3106 Module                                                    | 1-2  |

| 1-2        | DZQ11 System Applications                                       | 1-3  |

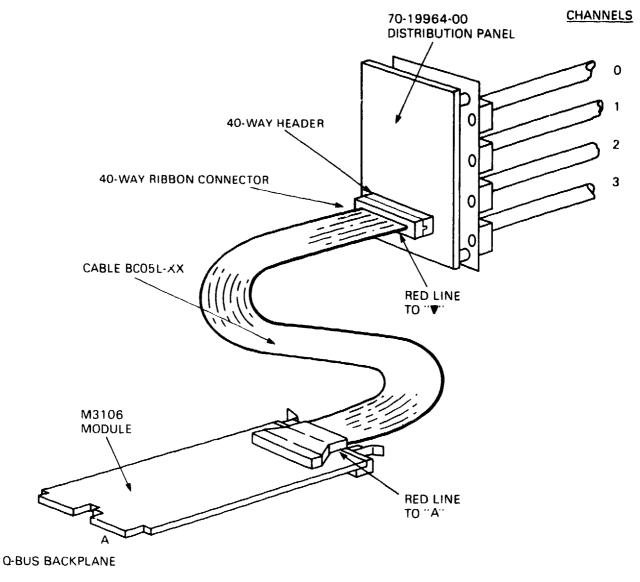

| 1-3        | Elements of the DZQ11 Option                                    |      |

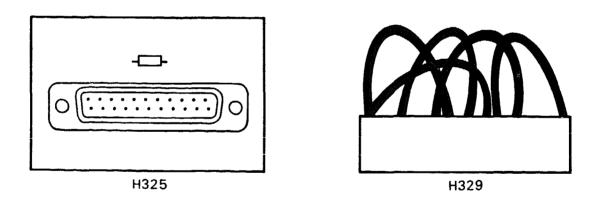

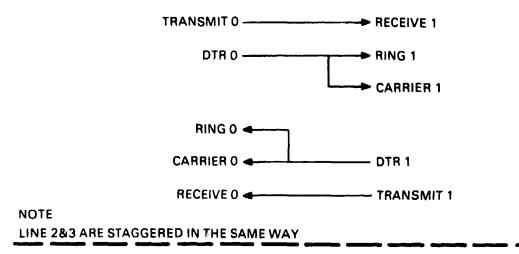

| 1-4        | Test Connectors H325 and H329                                   |      |

| 1-5        | Loopback Connection                                             |      |

| 2-1        | Jumper Locations (DC367B Socket Mount)                          |      |

| 2-2        | Jumper Locations (DC367B Surface Mount)                         | 2-7  |

| 2-3        | Jumper Locations (DC7085 Surface Mount)                         |      |

| 2-4        | DZQ11 Installation (BC11U-25)                                   |      |

| 2-5        | DZQ11 Installation (70-19964-00)                                | 2-13 |

| 3-1        | Register Bit Assignment                                         | 3-2  |

|            | TABLES                                                          |      |

| Table No.  | Title                                                           | Page |

| 2-1        | Items Supplied per Configuration                                | 2-4  |

| 2-2        | Jumper Configuration                                            | 2-9  |

| 2-3        | Break Character Response Options                                | 2-10 |

| 2-4        | Address Switch Selection: E28 on 50-16374-01 Etch Revisions and |      |

|            | E17 on 50-16374-02 Etch Revisions                               | 2-11 |

| 2-5        | Vector Switch Selection: E13 on 50-16374-01 Etch Revisions and  |      |

|            | E11 on 50-16374-02 Etch Revisions                               |      |

| 2-6        | Floating Address Assignments                                    | 2-16 |

| 2-7        | One DUV11 and One DZQ11                                         | 2-17 |

| 2-8        | Two DZQ11s                                                      | 2-18 |

| 2-9        | First Part of Q-bus Vector Address Assignments List             | 2-18 |

| 3-1        | DZQ11 Register Address Assignments                              |      |

| 3-2        | CSR Bit Assignments                                             | 3-3  |

| 3-3        | RBUF Bit Assignments                                            | 3-5  |

| 3-4        | LPR Bit Assignments                                             | 3-5  |

## CHAPTER 1 GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

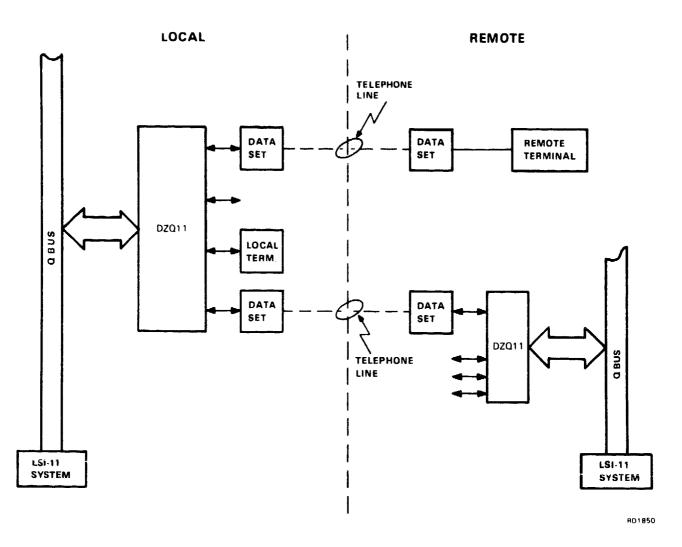

The DZQ11 is a Q-bus option. Its outline is shown in Figure 1-1. The DZQ11 is an asynchronous multiplexer that interfaces between a Q-bus processor and four asynchronous serial data communication lines. The DZQ11 communications interfaces are compatible with RS-232-C (V.28) and RS-423-A (V.10/X.26). There is enough modem control to permit dial-up (auto-answer) operation with full-duplex modems\*, such as the Bell models 103, 113, 212, or equivalent. The device, however is not intended for use on public communication services in countries where it may not meet the requirements for attachment approval. Remote full-duplex, working as a control (master) station over private lines, is also possible for point-to-point or multipoint operation. Figure 1-2 shows some possible applications for the DZQ11 in a Q-bus system.

All the DZQ11 parameters can be easily controlled by software. These parameters are:

- Baud rate

- Character length

- Number of stop bits for each line

- Enabling of parity checking for each line (odd or even)

- Enabling of transmitter and receiver interrupts.

#### Additional features include:

- Limited modem control

- Zero receiver baud rate

- Break generation and detection

- Silo buffering of received data

- Line turnaround.

The DZQ11 is program-compatible with the Q-bus DZV11.

#### NOTE

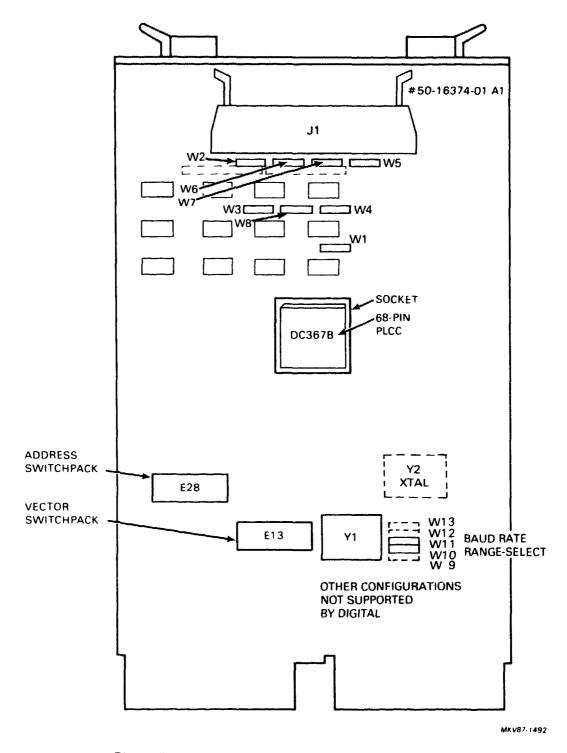

For details of the M3106 module variations, see Figures 2-1, 2-2, and 2-3.

Documents describing the DZO11 are:

- DZQ11 Asynchronous Multiplexer User's Guide EK-DZQ11-UG

- DZQ11 Asynchronous Multiplexer Technical Manual EK-DZQ11-TM

- Field Maintenance Printset MP-01795-01

- DZQ11 Maintenance Card EK-DZQ11-MC

<sup>\*</sup> The DZQ11 modern control does not support half-duplex operation or the secondary transmit-and-receive operation available on some moderns (such as the Bell 202)

NOTE: FOR DETAILS OF THE M3106 MODULE VARIATIONS,SEE FIG. 2-1, 2-2, AND 2-3.

MKV87-1490

Figure 1-1 M3106 Module

1-2

#### 1.2 PHYSICAL DESCRIPTION

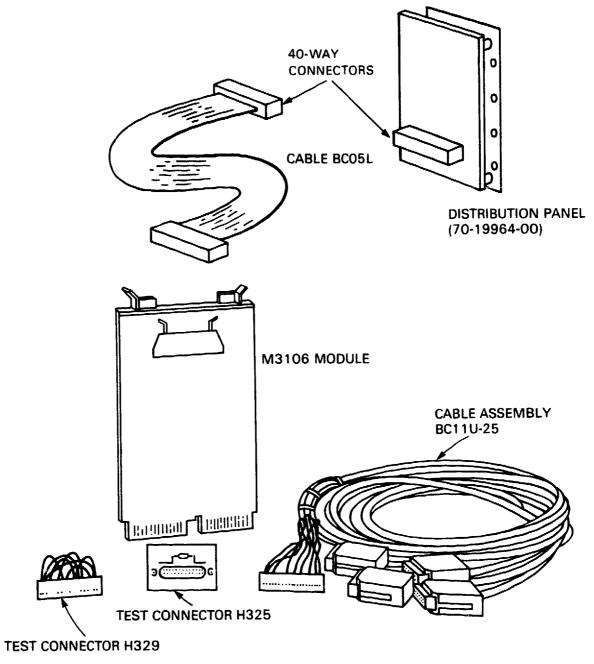

The DZQ11 is made up of two components connected by a ribbon cable. The components are:

- 1. A single dual-height module, 21.6×13.2 cm (8.51×5.19 inches), called the M3106 module. All input and output connections are available on a 40-way connector. This module includes all active circuitry, including the line drivers and receivers.

- 2. A distribution panel 6.7×8.5 cm (2.6×3.3 in) that contains four filtered D-type connectors, and a 40-way ribbon connector that connects to the M3106 module.

#### **NOTE**

### A G7272 Grant Continuity card may be needed. Refer to Section 2.3.2 for an explanation.

Figure 1-2 DZQ11 System Applications

#### 1.2.1 DZQ11 Configurations

The basic option supplied is the DZQ11-M and is made up of the following:

1. Logic Module M3106

User's Guide EK-DZQ11-UG

Maintenance Card EK-DZQ11-MC

4. Turnaround test connector H329

The basic option (DZQ11-M) can be supplied with one of five cabinet kits for installation into different systems. These are:

- 1. CK-DZQ11-DA (21-inch cable), example of use PDP-11/23S

- 2. CK-DZQ11-DB (12-inch cable), example of use Micro/PDP-11

- 3. CK-DZO11-DC (30-inch cable), example of use PDP-11/23+

- 4. CK-DZQ11-DF (36-inch cable), example of use PDP-11/83

- 5. CK-DZQ11-D3 unshielded option (BC11U-25 cable).

The first four cabinet kits are almost identical except for the length of the flat ribbon cables, and the addition of an adapter plate in the CK-DZQ11-DC. They are made up of the following:

- 1. BC05L-xx cable (see NOTE)

- 2. H325 line-loopback connector

- 3. The distribution panel 70-19964-00

- 4. Mounting bolts and washers for the distribution panel.

A system integrated DZQ11 option is a DZQ11-DP.

#### NOTE

The distribution panels provide noise filtering and static discharge protection on the communications lines. The -DC version has an adapter plate which allows the panel to be mounted in the PDP-11/23+.

BC05L-xx cables are supplied in different lengths for each kit as previously specified.

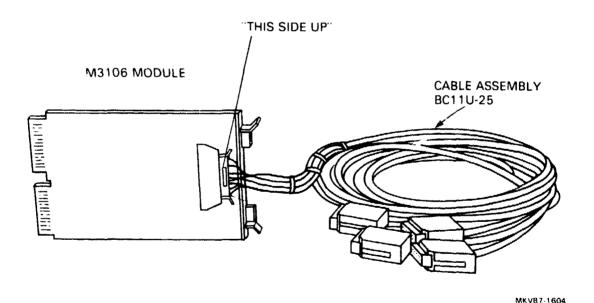

The CK-DZQ11-D3 cabinet kit is a cable assembly made up of four cables, with D-type connectors at one end, and the other end connected to a socket which fits in the module connector. This kit does not provide noise filtering or static discharge protection on the communications lines.

MKV87-1491

Figure 1-3 Elements of the DZQ11 Option

#### 1.2.2 Interface Cables

The connections from the DZQ11 use 25-pin male subminiature D-type connectors as specified for RS-232-C.

| Circuit AA (CCITT* 101)  | Pin 1  | Protective Ground   |

|--------------------------|--------|---------------------|

| Circuit AB (CCITT 102)   | Pin 7  | Signal Ground       |

| Circuit BA (CCITT 103)   | Pin 2  | Transmitted Data    |

| Circuit BB (CCITT 104)   | Pin 3  | Received Data       |

| Circuit CD (CCITT 108.2) | Pin 20 | Data Terminal Ready |

| Circuit CE (CCITT 125)   | Pin 22 | Ring Indicator      |

| Circuit CF (CCITT 109)   | Pin 8  | Carrier             |

#### NOTE

Signal ground and protective ground are connected together, through the chassis, by jumper W1 on the 70-19964-00 distribution panel.

#### 1.2.3 Test Connectors

Figure 1-4 shows the two accessory test connectors, H2. ) and H325.

The H329 plugs into the module I/O connector and connects line 0 to line 1, and line 2 to line 3.

The H325 plugs into an EIA connector on the distribution panel, or BC11U-25 cable assembly, to loopback data and modem signals over a single line. The loopback connections are shown in Figure 1-5.

Figure 1-4 Test Connectors H325 and H329

AD1851

<sup>\*</sup> CCITT - The International Consultative Committee for Telegraphy and Telephony is an advisory committee created under the United Nations to recommend worldwide standards.

#### H329 STAGGERED TURNAROUND

#### **H325 LOOPBACK CONNECTIONS**

Figure 1-5 Loopback Connection

RD1876

#### 1.3 SPECIFICATIONS

Environmental, electrical, and performance specifications for the DZQ11 are listed in the following paragraphs.

#### 1.3.1 Environmental

Storage temperature -40 degrees C to 66 degrees C

(-40 degrees F to 151 degrees F)

Operating temperature 5 degrees C to 50 degrees C

(41 degrees F to 122 degrees F)

Relative humidity Within the range of 10% to 95% non-condensing, at a maximum

wet-bulb temperature of 32 degrees C (90 degrees F) and a

minimum dew point of 2 degrees C (36 degrees F).

#### NOTE

Digital Equipment Corporation normally defines the operating temperature range for a system as 5 degrees C to 50 degrees C (41 degrees F to 122 degrees F). The 10 degrees C (50 degrees F) difference between the upper limits quoted allows for the temperature gradient within the system box.

The maximum operating temperatures must be derated by 1.8 degrees C/1000 m (1 degree F/1000 ft) for operation at high altitude sites.

#### 1.3.2 Electrical

Power consumption 1.100 A at + 5 V dc typical

0.236 A at + 12 V dc typical

Q-bus loading Q-bus ac loads - 1.5 ac loads

Q-bus dc loads - 1.0 dc loads

#### 1.3.3 Performance

The following paragraphs describe the DZQ11 performance capabilities and restrictions.

#### NOTE

All revisions to the M3106 module are of equal functionality and performance.

- 1.3.3.1 Interfaces The DZQ11 module interfaces directly to the Q-bus. This includes Q-bus variations with 22-, 18- and 16-bit addressing.

- 1. System Bus Interface

The DZQ11 module interfaces directly to a Q22 or other Q-bus via connectors A and B. The module meets the DIGITAL Q-bus specification.

#### 2. Serial Interfaces

The DZQ11 serial interfaces comply with a subset of EIA/CCITT standards RS-232-C/V.24. The electrical characteristics are compatible with EIA/CCITT standards RS-232-C/V.28 and RS-423/V.10 (unbalanced interface).

1.3.3.2 Maximum Configurations – The DZQ11 multiplexer is assigned a device address in the floating address space. The floating address space starts at 7600108 and extends to 7637768. Maximum configuration of DZQ11s is not limited by floating address space, but is limited by the rules controlling a system configuration of average size.

As the DZQ11 needs one backplane AB slot-pair, it is physically possible to mount:

- Two M3106 modules in a PDP-11/23-S

- Three M3106 modules in a Micro/PDP-11

- Four to five M3106 modules in a PDP-11/23+

These numbers are the absolute maximum, because of the limited number of 70-19964-00 distribution panels that can be installed in the rear panel of the mounting box. These numbers may also be limited by the available capacity of the power supply, if other options are installed in the mounting box.

1.3.3.3 Throughput - Each DZQ11 is capable of a throughput of 10 970 characters per second (chars/s). This rate is computed as follows.

(Bits/s × number of lines × directions) divided by bits/char

$(9.600 \times 4 \times 2)/7$  equals 10.970 chars/s, at 5 bits/char with one start and one stop bit and no parity.

The full device throughput can only be maintained when a character service routine takes 100 microseconds or less.

The DZQ11 has a maximum non-standard data rate of 19 800 baud. At this rate the throughput is 22 625 characters per second.

1.3.3.4 Receivers — The receivers perform serial-to-parallel conversion of 5-, 6-, 7-, or 8-level code with one start bit and at least one stop bit. The character length, number of stop bits, parity generation, and operating speed are programmable parameters for each line. Both the receiver and the transmitter of a corresponding line share the same operating speed, and the receiver line can be enabled or disabled.

Each receiver is double buffered and has an acceptable input distortion of 43.75% on any bit. The sum of the character distortion must also not exceed 43.75%. An exception to this is the stop bit. The stop bit can tolerate an error of 50%, that is, the receiver will accept a stop bit as short as one half of a bit period. Break detection is provided on each receiver via a register bit. In addition, the configuration of switchpack E13-9 and E13-10 can cause the processor to boot or halt when a break is detected on line 3.

- 1.3.3.5 Transmitters The transmitters provide parallel-to-serial conversion of 5-, 6-, 7- or 8-level code with or without parity. The parity sense, when selected, can be either odd or even. The stop code can be either 1 or 2 units except when 5-level code is selected. When 5-level code is selected, the stop code can be set to 1 or 1.5 units. The character length, number of stop units, parity generation and sense, and operating speed are programmable parameters for each line. The operating speed for the transmitter is common with the receiver. Breaks can be transmitted on any line. The maximum start-stop distortion for the output of a transmitter is less than 2.5% for an 8-bit character.

- 1.3.3.6 Baud-Rate Generator The baud-rate generators are completely programmable. Each line has an independent generator which can select 1 of 16 baud rates. Speed tolerance for all rates is better than 0.3%. The baud rates are shown in Section 1.3.3.7.

1.3.3.7 Performance Summary – The following list shows the programmable features offered for each line.

Character length 5-, 6-, 7-, or 8-level code

Number of stop bits 1 or 2 for 6-, 7-, or 8-level code.

1 or 1.5 for 5-level code

Parity Odd, even, or none

Baud rates 50, 75, 110, 134.5, 150, 300, 600, 1 200, 1 800, 2 000, 2 400, 3

600, 4 800, 7 200, and 9 600 (and non-standard 19 800)

Breaks Can be generated and detected on each line

Line 3 has a hardware response to detected breaks which, when enabled, may generate a HALT or BOOT. This facility can be

selected by switches.

#### 1.3.4 Interrupts

The following interrupts are available on the DZQ11.

- 1.3.4.1 Receiver-Done Interrupt The receiver-done interrupt occurs every time a character appears at the output of the receiver buffer register and the silo alarm is disabled. The receiver-done interrupt can be enabled or disabled from the bus.

- 1.3.4.2 Silo-Alarm Interrupt The silo-alarm interrupt occurs after 16 entries have been made into the receive buffer register by the scanner. This interrupt disables the receiver-done interrupt, and is armed again when the receive buffer register has been read.

- 1.3.4.3 Transmit Interrupt The transmit interrupt occurs every time the scanner finds a bufferempty condition, and the transmitter control register bit is set for that line. It can be enabled or disabled from the bus.

### CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter contains the procedures for the unpacking, installation, and initial checkout of the DZQ11 asynchronous multiplexer. It contains information on the following:

- Device and vector address selection

- Recommended cables

- Testing after installation

- Floating address and vector assignment.

#### 2.2 UNPACKING AND INSPECTION

The DZQ11 is packed following normal commercial packing practices. To unpack, first remove all packing material and check the equipment against the shipping list. (Table 2-1 contains a list of supplied items per configuration.) Report any damage or shortages to the shipper immediately and inform the local DIGITAL office. Examine all parts and carefully examine the module for damage, loose components, and breaks in the etched paths.

#### **CAUTION**

The M3106 is supplied in a protective sleeve. Do not remove the sleeve until you are about to install the module. Protect the module from static during installation.

#### **WARNING**

The procedures described in this chapter involve the removal of the system covers, and should be performed only by trained personnel.

#### **ATTENTION**

Les procédures décrites dans ce chapitre nécessitent l'enlévement des capots du système. Elles ne pourront être effectuées que par du personnel qualifié.

#### **VORSICHT!**

Bei der Ausfuhrung der in diesem Kapitel beschriebenen Anweisungen mussen die Systemabdeckungen entfernt werden. Dies sollte nur von geschultem Personal ausgefuhrt werden.

#### : ATENCION!

Los procedimientos descritos en este capitulo incluyen el desmontaje de las cubiertas del sistema y debe ser realizado solamente por personal entrenado.

#### ADVARSEL!

Ifølge de procedurer, som er beskrevet i dette kapitel, skal systemets beskyttelsesplader fjernes; dette bør kun udføres af personer der ved hvordan dette skal gøres.

#### WAARSCHUWING

Bij de procedures die in dit hoofdstuk worden beschreven dienen bepaalde delen van de systeemomhulling te worden verwijderd; dit mag uitsluitend worden gedaan door opgeleid personeel.

#### **VAROITUS!**

Tässä luvussa kuvatut toimenpiteet liittyvät järjestelmän suojakansien irrottamiseen. Ainoastaan koulutettu henkilökunta saa suorittaa nämä toimenpiteet.

注 意

な章では、本体カバーの取り外し等について述べてあります。作業は、必す専門の担当者によっておこなって下さい。

#### אזהרה

הפעולות המתוארות בפרק זה, כרוכות בהסדת המכסים של המערכת ויבוצעו אך ורק על ידי אדם מוסמך.

#### **ATTENZIONE**

La procedura descritta in questo capitolo comporta la rimozione delle coperture e deve essere eseguita solo da personale specializzato.

#### **ADVARSEL**

I dette kapitlet beskrives bl. a. hvordan man fjerner dekslene rundt systemet. Dette arbeidet må bare utføres av fagfolk.

#### **AVISO**

Os procedimentos descritos neste capítulo respeitam à forma como se retiram as protecções do sistema. Dada a sua especificidade, recomendamos que seja executado por pessoal especializado.

#### **VARNING**

I detta kapitel beskrivs hur systemkaapan tas bort. Detta faar endast utfoeras av utbildad personal.

Table 2-1 Items Supplied per Configuration

| DZQ11-M Base Option                                               |     |             |      |    |     |

|-------------------------------------------------------------------|-----|-------------|------|----|-----|

| Description                                                       | Qua | ntity       |      |    |     |

| M3106 module H329 test connector DZQ11 User's Guide (EK-DZQ11-UG) |     | 1<br>1<br>1 |      |    | No. |

| CK-DZQ11-DA/DB/DC/D3/DF Cabinet kits                              | Qua | intity      | ,    |    |     |

| Description                                                       | DA  | DB          | DC   | D3 | DI  |

| 70-19964-00 distribution panel                                    | 1   | 1           | 1    | -  | 1   |

| 74-28684-01 adapter plate                                         | _   | •••         | 1    |    |     |

| BC05L-1K 21-inch cable                                            | 1   |             |      | -  |     |

| BC05L-01 12-inch cable                                            | -   | 1           | **** |    |     |

| BC05L-2F 30-inch cable                                            | -   |             | 1    | _  |     |

| BC11U-25 cable assembly                                           | -   | •••         | -    | 1  | -   |

| BC05L-03 36-inch cable                                            | -   | -           | ~_   | _  | 1   |

| H325 test connector                                               | 1   | 1           | 1    | 1  | 1   |

| 90-06633-00 screws                                                | 4   | 4           | 8    | -  | 4   |

| 90-06021-01 washers                                               | 4   | 4           | 8    |    | 4   |

#### 2.3 INSTALLATION PROCEDURE

The following paragraphs describe the installation of the DZQ11 option in a Q-bus system.

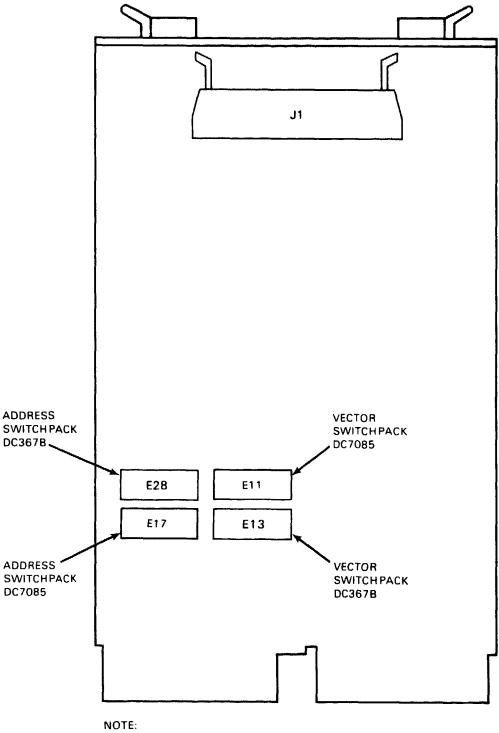

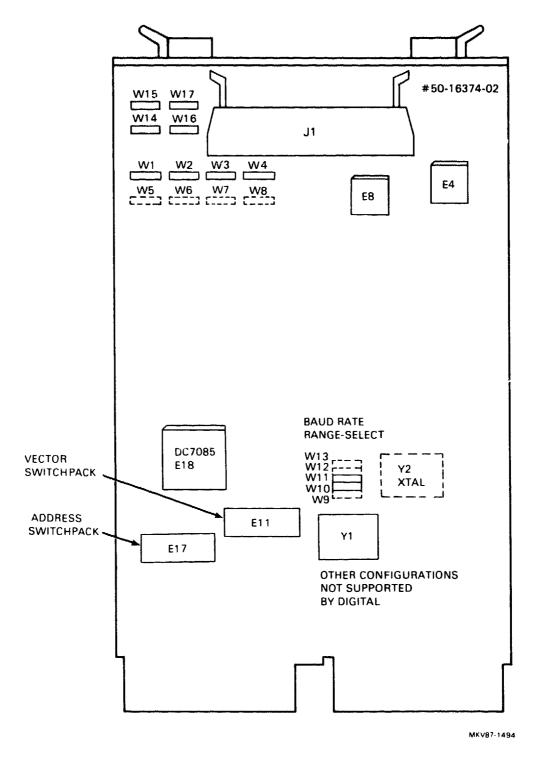

All variations have the same functionality. For the DC367B versions, the address and vector switchpacks are E28 and E13 respectively, while those for the DC7085 version are E17 and E11.

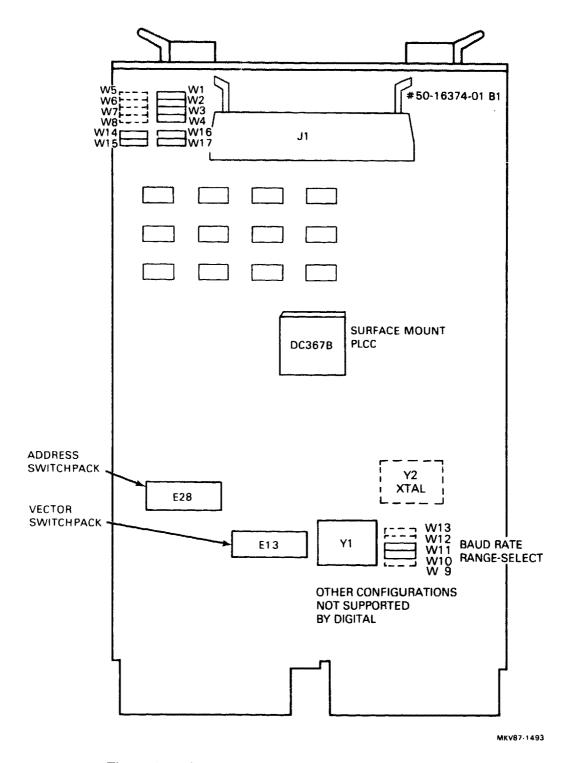

Figures 2-1 and 2-2 refer to the module variations that use the DC367B gate array. Figure 2-1 refers to the version that uses the socket-mounted DC367B, while Figure 2-2 refers to the version that uses the surface-mounted DC367B. Figure 2-3 refers to the M3106 variation that uses the DC7085 gate array.

All other components discussed in this manual have the same component numbers for all three variations, with the exception of jumpers W14-W17. These four jumpers are not available on the socket-mounted DC367B variation (Figure 2-1), and must be installed on the other two versions.

#### 2.3.1 Modem Control Jumpers

There are eight jumpers on both module versions which are used for modem control. The jumpers labelled W1 to W4 link the Data Terminal Ready (DTR) circuit to the Request To Send (RTS) circuit. This allows the DZQ11 to assert both DTR and RTS when using modems that need control of RTS. These jumpers must be installed for running the cable and external diagnostic programs. The four jumpers W5 to W8 link the Forced Busy (FB) circuits to the RTS circuits. When these jumpers are installed, asserting an RTS circuit also places an ON or BUSY level on the corresponding FB circuit. Jumpers W5 to W8 are not installed in the factory; therefore, they need to be added if this signal is required by the particular modem used. Table 2-2 shows the jumper line assignments.

Figure 2-1 Jumper Locations (DC367B Socket Mount)

Figure 2-2 Jumper Locations (DC367B Surface Mount)

Figure 2-3 Jumper Locations (DC7085 Surface Mount)

Table 2-2 Jumper Configuration

| Jumper     | Connection | Line |  |  |

|------------|------------|------|--|--|

| WI         | DTR to RTS | 3    |  |  |

| W2         | DTR to RTS | 2    |  |  |

| W3         | DTR to RTS | 1    |  |  |

| W4         | DTR to RTS | 0    |  |  |

| <b>W</b> 5 | RTS to FB  | 3    |  |  |

| W6         | RTS to FB  | 2    |  |  |

| W7         | RTS to FB  | 1    |  |  |

| <b>W</b> 8 | RTS to FB  | 0    |  |  |

#### 2.3.2 Module Installation

To install the M3106 module, perform the following.

#### NOTE

This checkout procedure should be performed by trained maintenance personnel only.

#### **CAUTION**

Switch off power before inserting or removing modules.

The M3106 is a fine-line-etch PCB. Handle it carefully to avoid damaging the etch.

Take anti-static measures to protect the module.

- 1. The Q-bus Interrupt Acknowledge and the DMA Grant signals are daisy-chained through the AB slots of the Q-bus backplane. If a DZQ11 is followed by a quad-size option in an AB/AB (Q/Q) backplane, it may cause an AB slot-pair to be left vacant. In order to maintain the continuity of the daisy-chained signals, a G7272 Grant Continuity card should be installed in the vacant A slot.

- 2. Refer to Section 2.4 for descriptions of the address assignments. Set the address switches so that the module responds to its assigned address. When a switch is closed (ON), a binary 1 is encoded. When a switch is open (OFF), a binary 0 is encoded. The switch numbered 1 is connected to address bit 12, 2 is connected to address bit 11, and so on (Table 2-4).

- 3. The other 10-position switchpack performs the vector selection. Switch position 7 is not used. Switch position 6 is connected to vector bit 3, 5 is connected to vector bit 4, and so on. When a switch is closed (ON), binary 1 is encoded. When a switch is open (OFF), a binary 0 is encoded (Table 2-5).

- 4. Position 8 of the vector selection switch is a test switch which can disconnect the DZQ11 oscillator from all circuitry. Make sure that this switch is in the ON position before installation.

- 5. Positions 9 and 10 of the vector selection switchpack controls the DZQ11 response to a Break character received on Line 3. There are three valid options: HALT, BOOT, and no response. Table 2-3 lists the switch selections.

Table 2-3 Break Character Response Options

| Switch |     | Effect of Break Character on Line 3 |                        |  |  |  |  |  |

|--------|-----|-------------------------------------|------------------------|--|--|--|--|--|

| 9      | 10  |                                     |                        |  |  |  |  |  |

| OFF    | OFF | No effect                           | (normal operation)     |  |  |  |  |  |

| ON     | OFF | Causes Processor to halt            | (specific application) |  |  |  |  |  |

| OFF    | ON  | Causes Processor to boot            | (specific application) |  |  |  |  |  |

| ON     | ON  | Illegal Condition                   |                        |  |  |  |  |  |

- 6. Make sure that +5 volts is present between AA2 and ground and that +12 volts is present between AD2 and ground. Measure at the nearest accessible point, if the backplane cannot be accessed.

- 7. Remove power and insert the module in an AB slot of the backplane.

- 8. Apply power and make sure that the +5 volts and +12 volts is present with the module installed.

#### **CAUTION**

Insert and remove modules slowly and carefully to prevent damage to the module components on the card guides, and to avoid changing switch selections in error.

Figure 2-4 DZQ11 Installation (BC11U-25)

Table 2-4 Address Switch Selection: E28 on 50-16374-01 Etch Revisions and E17 on 50-16374-02 Etch Revisions

| 4 |    | MSB     |       |    |         |    |    |    |       |     |    |          |    |     | , ···································· |               | LSB |

|---|----|---------|-------|----|---------|----|----|----|-------|-----|----|----------|----|-----|----------------------------------------|---------------|-----|

|   | 16 | 15      | 14    | 13 | 12      | 11 | 10 | 9  | 8     | 7   | 6  | 5        | 4  | 3   | 2                                      | 1             | 0   |

|   | 1  | 1       | 1     | 1  | •       |    |    | sv | VITCH | ES- |    |          | -  | 0   | 0                                      | 0             | 0   |

| _ |    | <b></b> |       |    |         |    |    |    |       | l   |    |          |    |     |                                        |               |     |

|   |    |         |       |    | )  <br> |    |    |    |       |     |    |          |    |     |                                        |               |     |

|   |    |         | VITCH |    | 1       | 2  | 3  | 4  | 5     | 6   | 7  | 8        | 9  | 10  |                                        | EVICE<br>DDRE |     |

|   |    |         |       |    |         |    |    |    |       |     |    |          |    |     | 17                                     | 7600          | 00  |

|   |    |         |       |    |         |    |    |    |       |     |    |          |    | ON  |                                        | 7600          | 1   |

|   |    |         |       |    |         |    |    |    |       |     |    |          | ON |     |                                        | 7600          |     |

|   |    |         |       |    |         |    |    |    |       |     |    |          | ON | ON  | Ì                                      | 7600          |     |

|   |    |         |       |    |         |    |    |    |       |     |    | ON<br>ON |    | ON  |                                        | 7600<br>7600  |     |

|   |    |         |       |    |         | ļ  |    |    |       |     |    | ON       | ON | UN  |                                        | 7600<br>7600  | ı   |

|   |    | }       |       |    |         |    |    |    |       |     |    | ON       | ON | ON  | l .                                    | 7600<br>7600  |     |

|   |    |         |       |    |         | }  |    |    |       |     | ON | U.T      | 0  | 0,, |                                        | 7601          |     |

|   |    |         |       |    |         |    |    |    |       | ON  |    |          |    |     | 17                                     | 7602          | 00  |

|   |    |         |       |    |         |    |    |    |       | ON  | ON |          |    |     | 17                                     | 7603          | 00  |

|   |    |         |       |    |         |    |    |    | ON    |     |    |          |    |     | 17                                     | 7604          | 00  |

|   |    |         |       |    |         |    |    |    | ON    |     | ON |          |    |     | 17                                     | 7605          | 00  |

|   |    |         |       |    |         |    |    |    | ON    | ON  |    |          |    |     | 17                                     | 7606          | 00  |

|   |    |         |       |    |         |    |    |    | ON    | ON  | ON |          |    |     | ł                                      | 7607          |     |

|   |    |         |       |    | ŀ       |    | ON | ON | ON    | ON  | ON | ON       | ON |     | 17                                     | 7637          | 60  |

|   |    |         |       |    |         |    | ON | ON | ON    | ON  | ON | ON       | ON | ON  | 17                                     | 7637          | 70  |

ON = SWITCH CLOSED TO RESPOND TO A LOGICAL 1 ON THE BUS

MKV87-1602

Table 2-5 Vector Switch Selection: E13 on 50-16374-01 Etch Revisions and E11 on 50-16374-02 Etch Revisions

| MSB      |                              |       |    |    |               |   |             |                                     |                                         |       |          |          |     |                                                                           | LSB |

|----------|------------------------------|-------|----|----|---------------|---|-------------|-------------------------------------|-----------------------------------------|-------|----------|----------|-----|---------------------------------------------------------------------------|-----|

| 15       | 14                           | 13    | 12 | 11 | 10            | 9 | 8           | 7                                   | 6                                       | 5     | 4        | 3        | 2   | 1                                                                         | 0   |

| 0        | 0                            | 0     | 0  | 0  | 0             | 0 | •           |                                     | SWIT                                    | CHES  |          | -        | 1/0 | 0                                                                         | 0   |

|          |                              |       |    |    | WITCI<br>UMBI |   | 1           | 2                                   | 3                                       | 4     | 5        | 6        |     | CTOF                                                                      |     |

| SE<br>FO | FER 1<br>CTIO<br>R SE<br>E13 | N 2.3 | 3  |    |               |   | ON ON ON ON | 2222222<br>2000202222<br>2000222222 | 222222222222222222222222222222222222222 | 20000 | 22 22 22 | ON ON ON |     | 300<br>310<br>320<br>330<br>340<br>350<br>360<br>370<br>400<br>500<br>700 |     |

ON = SWITCH CLOSED TO PRODUCE A LOGICAL 1 ON THE BUS

MKV87-1603

MKV87-1495

Figure 2-5 DZQ11 Installation (70-19964-00)

#### 2.3.3 Testing DZQ11s in PDP-11 Systems

The following diagnostics are available to test DZQ11s installed in PDP-11 systems. DZITA and DVDZD are only used when a link between two processors is to be tested.

| CVDZA<br>CVDZB<br>CVDZC<br>CXDZB | DZV11/DZQ11 Logic Test - Part 1 DZV11/DZQ11 Logic Test - Part 2 DZV11/DZQ11 Cable/Echo Test DECX/11 Module |

|----------------------------------|------------------------------------------------------------------------------------------------------------|

| DZITA<br>DVDZD                   | Interprocessor Test Program (ITEP) Overlay for ITEP                                                        |

Test the option as follows.

- 1. Run diagnostics CVDZA and CVDZB in internal mode, to verify operation. Refer to the listing for more help. Run at least three passes without error.

- 2. Insert the H329 test connector in J1 with the letter side facing up. J1 is the cable connector at the top of the M3106 module.

- Run CVDZA and CVDZB in the staggered mode, to verify module operation. Refer to the diagnostic listing for the correct procedure. Run at least three passes without error.

- 3. If the unshielded cab-kit (D3) version is used, replace the H329 test connector with the 40-way connector end of the BC11U cable assembly. Follow the "This side up" instruction on the assembly. Refer to Figure 2-4 for assembly and interconnection instructions.

- 4. If the cab-kit versions CK-DZQ11-DA, -DB or -DF are used, feed the cable through the rear of the cabinet and connect it to the distribution panel. Mount the distribution panel in the opening at the rear of the cabinet.

- The -DC version is provided with an adapter plate to fit the large opening in a PDP-11/23+. Mount the adapter plate on the distribution panel, with four of the eight screws provided. Mount the distribution panel as described above.

- 5. Connect the H325 test connector on the first line and run diagnostic CVDZC. Select the cable-test part of the diagnostic. Three passes are needed without error. Repeat this step for each line.

- 6. Run the DECX/11 system exerciser to verify the absence of Q-bus interference with other system devices.

- 7. The DZQ11 is now ready for connection to external equipment. If the connection is to a local terminal through either of the two options (BC11U-25 or 70-19964-00), a null modem cable assembly must be used. Use the BC22A, BC22D, or BC03P null modem cables for connection between the option and the terminal. The H312-A null modem unit may also be used in place of the null modem cables.

Connections between the option and a modern should be made using a BC22E or BC05D cable.

All of the cables referred to, with the exception of the BC11U-25, must be ordered separately as they are not components of a DZQ11 option.

If a terminal is available, run the diagnostic CVDZC in echo-test mode to verify the cable connections and the terminal equipment.

#### 2.3.4 Testing in MicroVAX Systems

The following diagnostic tests are available for testing DZQ11s in MicroVAX systems.

EHXDZ DZV11/DZQ11 Test

EHKMV Macroverify - MicroVAX System Test

Macroverify is a standalone diagnostic which contains a DZV11/DZQ11 test module.

Refer to the appropriate diagnostic listing, or to Chapters 11 and 14 of the MicroVAX Owner's Guide, for details of how to run EHXDZ and EHKMV.

MicroVAX diagnostic testing is described in your MicroVAX Diagnostic Maintenance (MDM) package.

#### 2.4 DEVICE ADDRESS ASSIGNMENTS

On UNIBUS and Q-bus systems, a range of addresses ( $xxx60010_8$  to  $xxx63776_8$ ) in the top 4K words is assigned as floating address space (xxx means all top address bits = 1).

The first part of the list of options (sufficient to include the DZQ11) which can be assigned floating device addresses is given in Table 2-6. 'Rank' gives the sequence of address assignment for both Q-bus and UNIBUS options.

If addresses are assigned according to defined rules, configuration programs can check which options are installed in a system. Having a combined list allows us to use one set of configuration rules and one configuration program for both O-bus and UNIBUS systems.

Table 2-6 Floating Address Assignments

| Rank | Device                                | Size<br>(decimal) | Modulus<br>(octal) |

|------|---------------------------------------|-------------------|--------------------|

| 1    | DJII                                  | 4 words           | 10                 |

| 2    | DHII                                  | 8 words           | 20                 |

| 3    | DQ11                                  | 4 words           | 10                 |

| 4    | DU11, DUV11*                          | 4 words           | 10                 |

| 5    | DUPII                                 | 4 words           | 10                 |

| 6    | LK11A                                 | 4 words           | 10                 |

| 7    | DMC11/DMR11                           | 4 words           | 10                 |

| 8    | DZ11, DZS11,<br>DZQ11*/DZV11*<br>DZ32 | 4 words           | 10                 |

<sup>\*</sup> Q-bus device

For example, the address assignment sequences could be:

| UNIBUS | Q-bus                        |

|--------|------------------------------|

| DJH    | No Q-bus equivalent of DJ11  |

| DHI1   | No Q-bus equivalent of DH11  |

| DQ11   | No Q-bus equivalent of DQ11  |

| DÙH    | DUV11                        |

| DUP11  | No Q-bus equivalent of DUP11 |

| LKIIA  | No Q-bus equivalent of LK11A |

| DMC11  | No Q-bus equivalent of DMC11 |

| DZ11   | DZQ11 and so on.             |

| · · ·  |                              |

Devices of the same type are given sequential addresses, therefore all DUV11s in a system will have lower addresses than DZQ11s or DZV11s.

For the purpose of address assignment, DZQ11s and DZV11s are considered as devices of the same type.

The column Size(decimal) in Table 2-6, shows how many words of address space are needed for each device. The column Modulus(octal) is the modulus used for starting addresses. For example, devices with an octal modulus of 10 must start at an address which is a multiple of 10<sub>8</sub>. The same rule is used to select a gap address (see assignment rules) after an option, or for a nonexistent device.

The assignment rules are as follows.

- 1. Addresses, starting at xxx60010, are assigned according to the sequence of Table 2-6

- 2. Option and gap addresses are assigned according to the octal modulus as follows.

- a. Devices with an octal modulus of 10 are assigned an address on a  $10_8$  boundary (the three lowest-order address bits = 0)

- b. Devices with an octal modulus of 20 are assigned an address on a 20g boundary (the four lowest-order address bits = 0)

- 3. Address space equal to the device's modulus must be allowed for each device which is connected to the bus

- 4. A one-word gap, assigned according to rule 2, must be allowed after the last device of each type. This gap could be bigger when rule 2 is applied to the following rank

- 5. A one-word gap, assigned according to rule 2, must be allowed for each unused rank on the list if a device with a higher address is used. This gap could be bigger when rule 2 is applied to the following rank

Two examples of address assignment follow. Table 2-7 shows addresses for a system with one DUV11 and one DZQ11. Table 2-8 shows addresses for a system with no DUV11 and two DZQ11s. Note that where there is no Q-bus device at a specific rank, the UNIBUS device parameters must be used to assign the gap. Vector assignments (see Section 2.5) are also shown in these tables.

Table 2-7 is supported by a description of how to apply the assignment rules.

Rank **Address** Designation Vector 1 xxx60010 DJ11 gap 2 xxx60020 DH11 gap 3 xxx60030 DOII gap 4 xxx60040 **DUV11** 300 DUV11 gap xxx60050 5 xxx60060 DUP11 gap 6 xxx60070 LK11A gap 7 xxx60100 DMC11 gap 8 xxx60110 DZQ11 310 xxx60120 DZO11 gap

Table 2-7 One DUV11 and One DZQ11

The first floating address is 760010. As a DJ11 has a modulus of 10<sub>8</sub>, its gap can be assigned to 760010. The next available location becomes 760012.

As a DH11 has a modulus of 20g, it cannot be assigned to 760012. The next modulo 20 boundary is 760020, so the DH11 gap is assigned to this address. The next available location is therefore 760022.

A DQ11 has a modulus of 10<sub>8</sub>. It cannot be assigned to 760022. Its gap is therefore assigned to 760030. The next available location is 760032.

The DUV11 has a modulus of 10<sub>8</sub>. It cannot be assigned to 760032. It is therefore assigned to 760040. As the size of DUV11 is four words, the next available address is 760050.

There is no second DUV11, so a gap must be left to indicate that there are no more DUV11s. As 760050 is on a 10g boundary. The DUV11 gap can be assigned to this. The next available address is 760052.

And so on.

Table 2-8 Two DZQ11s

| Rank | Address  | Designation | Vector |  |

|------|----------|-------------|--------|--|

| 1    | xxx60010 | DJ11 gap    |        |  |

| 2    | xxx60020 | DH11 gap    |        |  |

| 3    | xxx60030 | DQ11 gap    |        |  |

| 4    | xxx60040 | DÙVI I gap  |        |  |

| 5    | xxx60050 | DUP11 gap   |        |  |

| 6    | xxx60060 | LK11A gap   |        |  |

| 7    | xxx60070 | DMC11 gap   |        |  |

| 8    | xxx60100 | 1st DZQ11   | 300    |  |

| 8    | xxx60110 | 2nd DZQ11   | 310    |  |

|      | xxx60120 | DZQ11 gap   |        |  |

#### 2.5 INTERRUPT VECTOR ADDRESS ASSIGNMENTS

Addresses between 300<sub>8</sub> and 774<sub>8</sub> are designated as the floating vector space. These addresses are assigned in sequence as in Table 2-9.

Each device needs two 16-bit locations for each vector. For example, a device with one receive and one transmit vector needs four words of vector space.

The vector assignment rules are as follows.

- 1. Each device occupies vector address space equal to 'Size' words. For example, the DLV11-J occupies 16 words of vector space. If its vector was 300<sub>8</sub> the next available vector would be 340<sub>8</sub>.

- 2. There are no gaps, except those needed to align an octal modulus.

The vector addresses shown in Tables 2-7 and 2-8 are assigned according to these rules.

Table 2-9 First Part of Q-bus Vector Address Assignments List

| Device        | Size<br>(decimal) | Modulus<br>(octal) |  |

|---------------|-------------------|--------------------|--|

| DLV11-J       | 16                | 10                 |  |

| DLV11,DLV11-F | 4                 | 10                 |  |

| DRV11-B       | 4                 | 10                 |  |

| DRV11         | 4                 | 10                 |  |

| DLV11-E       | 4                 | 10                 |  |

| VSV11         | 8                 | 10                 |  |

| KWV11         | 4                 | 10                 |  |

| DUV11         | 4                 | 10                 |  |

| DZV11/DZQ11   | 4                 | 10                 |  |

# CHAPTER 3 DEVICE REGISTERS

### 3.1 SCOPE

This chapter describes the format and bit function of each register in the DZQ11.

### 3.2 DEVICE REGISTERS

The DZQ11 contains six addressable registers. Figure 3-1 shows the bit assignments of these registers and Table 3-1 lists the registers and related DZQ11 addresses.

Table 3-1 DZQ11 Register Address Assignments

| Register Name            | Mnemonic Address |        | Program<br>Capability |  |

|--------------------------|------------------|--------|-----------------------|--|

| Control and Status Reg.  | CSR              | 76XXX0 | Read/Write            |  |

| Receiver Buffer          | RBUF             | 76XXX2 | Read Only             |  |

| Line Parameter Register  | LPR              | 76XXX2 | Write Only            |  |

| Transmitter Control Reg. | TCR              | 76XXX4 | Read/Write            |  |

| Modem Status Register    | MSR              | 76XXX6 | Read Only             |  |

| Transmit Data Register   | TDR              | 76XXX6 | Write Only            |  |

XXX = Selected in agreement with the floating device address system.

## 3.2.1 Control and Status Register

The control and status register (CSR) can be addressed with a byte or word address. All bits in the CSR are cleared by an occurrence of BINIT, or by setting device Master Clear (CSR<04>). The format is shown in Figure 3-1 and the bit assignments are listed in Table 3-2.

|                 |      |                                         |     |                              | ALL REGISTER | BITS ARE<br>CLEARED BY<br>MASTER CLEAR<br>EXCEPT FOR |           | RBUF<14 00><br>TCR<15 08><br>MSR<15 00> |         |                          |             |                           |         |

|-----------------|------|-----------------------------------------|-----|------------------------------|--------------|------------------------------------------------------|-----------|-----------------------------------------|---------|--------------------------|-------------|---------------------------|---------|

| 1.SB<br>00      | 7-   | CASS                                    | 0.1 | RBUF<br>D0                   | WO           | LINE                                                 | RW -      |                                         | RO<br>I | R. 0                     | NO<br>NO    | TBUF<br>0                 | WA 0552 |

| 5               |      | 10N 10N                                 | 021 | RBUF<br>01                   | WO           | LINE                                                 | ₹<br>     | LINE<br>ENAB                            | ЯO      | R: 1                     | N<br>O<br>N | TBUF                      |         |

| 05              | 7    | 10N 10N                                 | 9   | RBUF<br>D2                   |              | ONSO                                                 | ₹         |                                         | ЯО      | RI 2                     | ا<br>ا ه    | TBUF<br>2                 |         |

| 03              | WH   | MAINT                                   | RO  |                              | wo           | CHAR<br>LGTH<br>A                                    | R. I      | LINE<br>ENAB                            | RO      | RI 3                     | WO.         | TBUF<br>3                 |         |

| 04              | RW   | CLR                                     | RO  | <u>u</u>                     |              | CHAR<br>LGTH<br>B                                    | 71        | \$\$\$\$\$\$                            |         | 0355                     | WO          | TBUF<br>4                 |         |

| 92              | Α    | MSE                                     | RO  | RBUF<br>DS                   | wo           | STOP<br>CODE                                         |           | 25/5°                                   |         | ON                       | wo          | TBUF                      |         |

| 90              | яw   |                                         | ВО  | RBUF<br>D6                   | wo           | PAR<br>ENAB                                          |           | 035n                                    |         | 035N<br>0N               | OW          | TBUF<br>6                 |         |

| ES<br>LOW<br>07 | во   | RDONE                                   | RO  | RBUF<br>D7                   | OM           | ODD<br>PAR                                           | 7         | NOT                                     |         | ONSON                    | OM          | TBUF<br>7                 |         |

| BYTES<br>HIGH L | во   | TLINE                                   | ВО  | RX<br>LINE<br>A              | WO           | SPEED<br>CODE<br>A                                   | WR        | DTR<br>0                                | ЯО      | CO<br>0                  | WO          | BRK<br>0                  |         |

| 60              | ВО   | 1                                       | ВО  | RX<br>LINE<br>B              | wo           | SPEED<br>CODE<br>B                                   | RW        | DTR                                     | မှ      | co<br>1                  | wo          | BRK                       |         |

| 10              |      | 35°C                                    |     | 035N                         | wo           | SPEED<br>CODE<br>C                                   | RW        | DTR<br>2                                | õ       | CO<br>2                  | wo          | BRK<br>2                  |         |

| 11              |      | 3550                                    |     | 035R                         | OM           | SPEED<br>CODE<br>D                                   | RW        | DTR<br>3                                | RO      |                          | OM.         |                           |         |

| 12              | ₽.   | SAE                                     | RO  | PAR                          | wc           | RX<br>ENAB                                           |           | 035A                                    |         | 235.7<br>N               |             | 0350                      |         |

| 13              | ВО   | S A S                                   |     | EBB B                        |              | 10N                                                  |           | 104                                     |         | 2357<br>N                | l           | 0357                      |         |

| 4               | A.W. | ======================================= | 8   | OVAN                         |              | 1000                                                 |           | TON                                     | l .     | 0357                     | i           | OJSN                      |         |

| MSB<br>15       | ê    | TRDY                                    | 8   | DATA OVR                     |              | JON                                                  |           | 035n                                    |         | 0357<br>0N               |             | 035N                      |         |

|                 |      | CONTROL<br>& STATUS<br>(CSR)            |     | RECEIVER<br>BUFFER<br>(RBUF) |              | LINE<br>PARAMETER<br>(LPR)                           |           | TRANSMIT<br>CONTROL<br>(TCR)            |         | MODEM<br>STATUS<br>(MSR) |             | TRANSMIT<br>DATA<br>(TDR) |         |

|                 |      | DR0                                     |     | !                            | O#2          |                                                      | <b>\_</b> | DR4                                     | ·       |                          | <b>6</b>    |                           | J       |

Figure 3-1 Register Bit Assignment

Table 3-2 CSR Bit Assignments

| Bit     | Title                                         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <02:00> | Not used                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <03>    | Maintenance<br>(MAINT)                        | This is a READ/WRITE bit. When set it loops the serial output connections of the transmitter to the corresponding serial input connections of the receiver at the UART. (Used for loopback test only.)                                                                                                                                                                                                                                                                                                                                                                                              |

| <04>    | Master Clear<br>(CLR)                         | When written to a 1, this bit generates 'initialize' within the DZQ11. A read-back of the CSR with this bit set indicates initialize in progress within the device. This bit is self-clearing. All registers, silos, and UARTs are cleared with the following exceptions:                                                                                                                                                                                                                                                                                                                           |

|         |                                               | 1. Only bit 15 of the receiver buffer register (Data Valid) is cleared; the other bits (<14:00>) are not.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         |                                               | 2. The high byte of the transmitter control register is not cleared by Master Clear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |                                               | 3. The modem status register is not cleared by Master Clear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <05>    | Master Scan<br>Enable<br>(MSE)                | This read/write bit must be set to permit the receiver and transmitter control sections to start scanning. When cleared, Transmitter Ready (CSR<15>) is inhibited from setting, and the received character buffers (silos) are cleared.                                                                                                                                                                                                                                                                                                                                                             |

| <06>    | Receiver<br>Interrupt<br>Enable<br>(RIE)      | This bit permits the generation of an interrupt, when CSR<07> or CSR<13> is set. This bit is read/write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <07>    | Receiver Done (RDONE)                         | This is a read-only bit that is set when a character appears at the output of the first-in/first-out (FIFO) buffer. For the DZQ11 to run in the interrupt-per-character mode, CSR<06> must be set and CSR<12> must be cleared. With CSR<06> and CSR<12> cleared, character-flag mode is indicated. Receiver Done clears when the receiver buffer register (RBUF) is read or when Master Scan Enable (CSR<05>) is cleared. If the FIFO buffer contains an additional character, the Receiver Done flag may stay clear for up to 1 microsecond, while that character moves to the bottom of the FIFO. |

| <09:08> | Transmitter Line Number (TLINE B and TLINE A) | These read-only bits indicate the line number whose transmit buffer needs servicing. These bits are valid only when Transmitter Ready (CSR<15>) is set, and are cleared when Master Scan Enable is cleared. Bit <08> is the least-significant bit.                                                                                                                                                                                                                                                                                                                                                  |

| <11:10> | Not used                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 3-2 CSR Bit Assignments (Cont)

| Bit  | Title                                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <12> | Silo Alarm<br>Enable<br>(SAE)               | This is a read/write bit. When set, it enables the silo-alarm and prevents RDONE (bit <07>) from causing interrupts. If the receiver interrupt enable bit (bit <06>) is set, SAE enables the silo-alarm (bit <13>) to generate an interrupt after 16 silo entries.                                                                                                                                                                                                                                                        |  |

| <13> | Silo Alarm<br>(SA)                          | This is a read-only bit set by the hardware after 16 characters have been entered into the FIFO buffer. Silo Alarm is held cleared when Silo Alarm Enable (CSR<12>) is cleared. This bit is cleared by a read to the receiver buffer register and does not set until 16 additional characters are entered into the buffer. If Receiver Interrupt Enable (CSR<06>) is set, the occurrence of Silo Alarm generates receiver interrupt request. Flag mode operation of the Silo Alarm bit is permitted with CSR<06> cleared. |  |

| <14> | Transmitter<br>Interrupt<br>Enable<br>(TIE) | This is a read/write bit which must be set for Transmitter Ready to generate an interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| <15> | Transmitter<br>Ready<br>(TRDY)              | This read-only bit is set by the hardware when the transmitter scanner stops on a line whose transmit buffer may be loaded with another character and whose related TCR bit is set. The transmitter line number, specified in CSR<09:08>, is only valid when Transmitter Ready is set. Transmitter Ready is cleared by any of the following conditions:                                                                                                                                                                   |  |

|      |                                             | 1. When Master Scan Enable is cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|      |                                             | 2. When the related TCR bit is cleared for the line number pointed to in CSR<09:08>                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|      |                                             | If additional transmit lines need service, Transmitter Ready appears again within 1.4 microseconds of the completion of the 'transmit data register load' instruction. When Transmitter Ready occurs with Transmitter Interrupt Enable set, a transmitter interrupt request is generated.                                                                                                                                                                                                                                 |  |

### 3.2.2 Receiver Buffer

The receiver buffer (RBUF) is a 16-bit read-only register that contains the received character at the output of the FIFO buffer. A read of the register causes the character entry to be removed from the buffer, and all other entries to shift down to the lowest location that is not occupied. Only the Data Valid bit (RBUF<15>) is cleared by BINIT or by setting device Master Clear (CSR<04>). Bits <14:00> are not affected. The bit assignments for the RBUF register are listed in Table 3-3.

Table 3-3 RBUF Bit Assignments

| Bit     | Title                                          | Function                                                                                                                                                                                                                                                                                                                                            |

|---------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <07:00> | Received<br>Character<br>(RBUF D<7:0>)         | These bits contain the received character, right justified. the least-significant bit is bit <00>. For short characters, bits that are not used are logic low. The parity bit is not shown.                                                                                                                                                         |

| <09:08> | Received Line Number (RX LINE B and RX LINE A) | These bits contain the line number on which the Received Character was received. Bit <08> is the least significant.                                                                                                                                                                                                                                 |

| <11:10> | Not used                                       |                                                                                                                                                                                                                                                                                                                                                     |

| <12>    | Parity Error (PAR ERR)                         | This bit is set if the sense of the parity of the received character does not agree with the parity defined for that line.                                                                                                                                                                                                                          |

| <13>    | Framing Error<br>(FRAM ERR)                    | This bit is set if the received character did not have a stop bit present at the correct time. This bit is usually interpreted as indicating that a break has been received.                                                                                                                                                                        |

| <14>    | Overrun Error<br>(OVRN ERR)                    | This bit becomes set when a received character is overwritten in the UART buffer (by a following character), before it has been transferred by the scanner to the FIFO.                                                                                                                                                                             |

| <15>    | Data Valid<br>(DATA VALID)                     | This bit, when set, indicates that the data in bits <14:00> is valid. This bit permits the use of a character-handling program which again and again takes characters from the FIFO buffer until there are no more available. This is done by reading this register and checking bit <15> until the program gets a word for which bit <15> is zero. |

# 3.2.3 Line Parameter Register

The line parameter register (LPR) controls the operating parameters related to each line in the DZQ11. The LPR must be addressed with a word address and is a write-only register. The line parameters for all lines must be loaded again following an occurrence of either BINIT or device Master Clear. Table 3-4 lists bit assignments.

Table 3-4 LPR Bit Assignments

| Bit     | Title                                              | Function                                                                                                                                                                                                              |

|---------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <01:00> | Parameter Line<br>Number<br>(LINE B and<br>LINE A) | These bits specify the line number for which the parameter information (bits <12:3>) is to apply. Bit <00> is the least-significant bit.                                                                              |

| <02>    | Not used                                           | Must always be written as a zero when specifying the parameter line number. Writing this bit as a one extends the parameter line number field into nonexistent lines. Parameters for lines 00 to 03 are not affected. |

Table 3-4 LPR Bit Assignments (Cont)

| Bit     | Title                                              | Function                                                                                                                                                                                                                                                                                                                                                                       |        |             |     |                                                    |            |

|---------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|-----|----------------------------------------------------|------------|

| <04:03> | Character<br>Length                                | These bits are set to receive and transmit characters of the length (except parity) shown below.                                                                                                                                                                                                                                                                               |        |             |     |                                                    |            |

|         | (CHAR LGTH<br>B and CHAR<br>LGTH A)                | Bit 04                                                                                                                                                                                                                                                                                                                                                                         |        | Bit 03      |     |                                                    |            |