## **DRB32 Hardware Installation Guide**

Order Number: EK-DRB32-IN-002

This book describes the installation of the DRB32 adapter. It also provides information on running the DRB32 diagnostics, troubleshooting, and installing option modules.

digital equipment corporation maynard, massachusetts

The DRB32 is a high-speed parallel port sold by Digital Equipment Corporation for use in qualified applications. Contact your Digital sales representative for more information.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

Copyright © 1987, 1990 by Digital Equipment Corporation. All Rights Reserved.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEC PDP

DECnet ULTRIX

DECUS UNIBUS

DRB32 VAX

DR11-W VAXBI

VAXcluster VMS

## **Contents**

## Preface

| Chapter 1 | Introduction                                 |      |

|-----------|----------------------------------------------|------|

| 1.1       | Functional Description of the DRB32 Module 1 | -1   |

| 1.2       | DRB32 Configurations 1                       | -4   |

|           | 1.2.1 DRB32-M Option                         | -4   |

|           | 1.2.2 DRB32-E Option                         | -4   |

|           | 1.2.3 DRB32-W Option 1                       |      |

| 1.3       | DRB32 Software                               |      |

| Chapter 2 | DRB32 Hardware Installation Procedures       |      |

| 2.1       | Summary of Installation Tasks 2              | 2-1  |

|           | 2.1.1 Site Preparation                       |      |

|           | 2.1.2 DRB32 Option Components                |      |

|           | 2.1.3 Configuration Rules                    |      |

| 2.2       | Option Installation 2                        |      |

|           | 2.2.1 DRB32-M Installation 2                 |      |

|           | 2.2.2 DRB32-E Installation                   |      |

|           | 2.2.3 DRB32-W Installation                   |      |

| Chapter 3 | Test and Verification                        |      |

| 3.1       | Test and Verification3                       | 3-1  |

| 3.2       | Self-Test3                                   | 3-2  |

|           | 3.2.1 Normal Self-Test                       | 3-2  |

|           | 3.2.2 Fast Self-Test                         | 3-5  |

| 3.3       | EVDRH (VAX Level 3)                          | 3-5  |

|           | 3.3.1 Running EVDRH                          | 3-8  |

|           | 3.3.2 DRB32 Output Tester                    | 3-11 |

|           |                                              |      |

## Contents

| 3.4        | EVDRI (VAX Level 3)                                  |      |

|------------|------------------------------------------------------|------|

|            | 3.4.1 Running EVDRI                                  | 3-17 |

|            | 3.4.2 DRB32-W Loopback Cable                         | 3-19 |

| 3.5        | Troubleshooting                                      | 3-21 |

|            | 3.5.1 Diagnosing the DRB32-M                         | 3-21 |

|            | 3.5.2 Diagnosing the DRB32-E                         | 3-22 |

|            | 3.5.3 Diagnosing the DRB32-W                         | 3-22 |

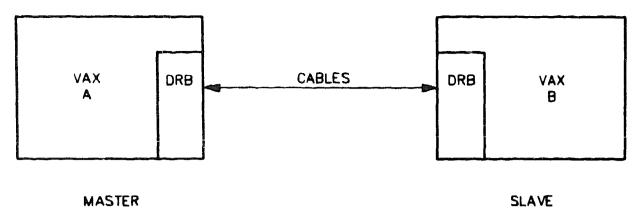

| 3.6        | Message Passing Between DRB32s (LINK Tests)          | 3-23 |

|            | 3.6.1 Running the EVDRH Single-System LINK Test      | 3-23 |

|            | 3.6.2 Running the Dual-System LINK Test              | 3-29 |

|            | 3.6.3 Interpreting the Dual-System LINK Test Results | 3-31 |

|            | 3.6.4 The DRB32-W Single-System LINK Test            | 3-34 |

| Appendix A | DRB32 Output Tester Patterns                         |      |

| Appendix B | Error Log Format                                     |      |

| Assessin C | DDB22 France Codes                                   |      |

| Appendix C | DRB32 Error Codes                                    |      |

| Appendix D | DRB32 Self-Test Error Codes                          |      |

| Appendix E | DRB32 Registers                                      |      |

| E.1        | BIIC Registers                                       | E-1  |

| E.2        | DRB32 Module Registers                               |      |

| E.3        | Parallel Port Registers                              |      |

| Appendix F | Glossary                                             |      |

| Figures    |                                                      |      |

| 1-1        | DRB32 Simplified Block Diagram                       | 1-3  |

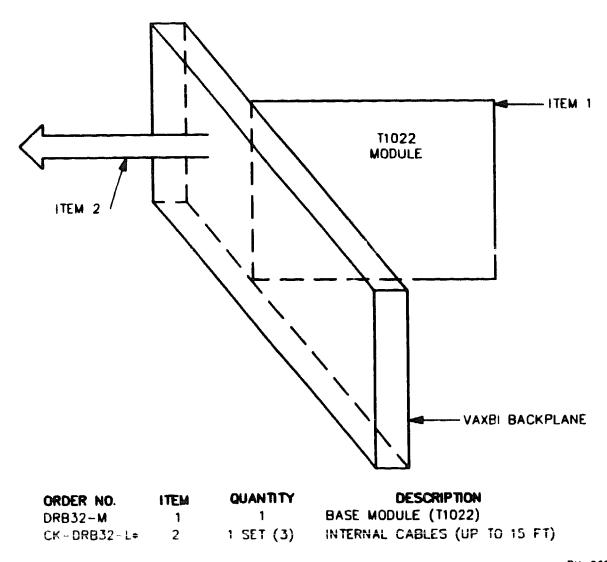

| 2-1        | DRB32-M Module                                       |      |

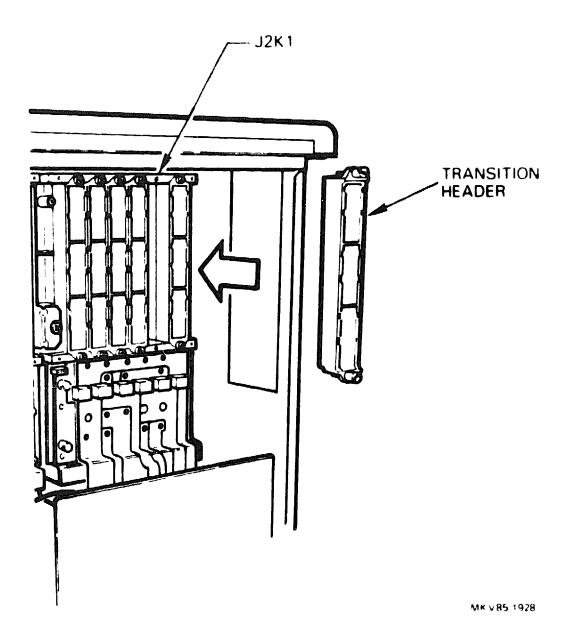

| 2-2        | Transition Header Installation                       | 2-7  |

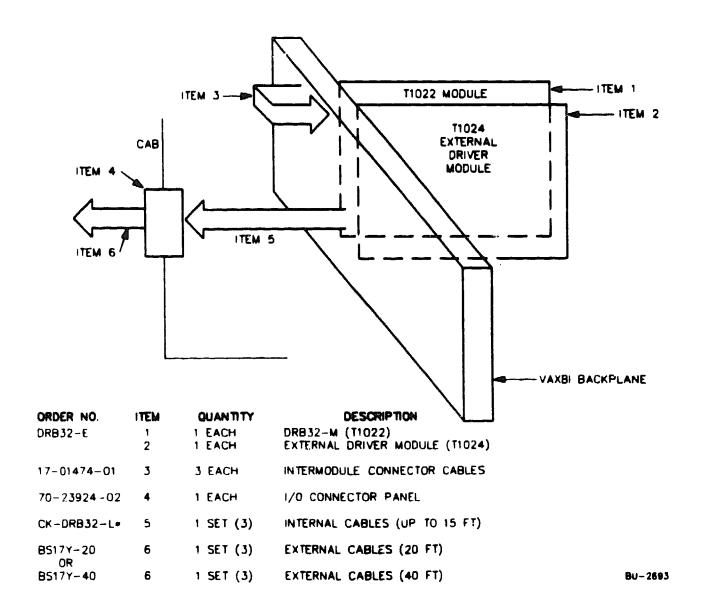

| 2-3        | DRB32-E Option                                       | 2-8  |

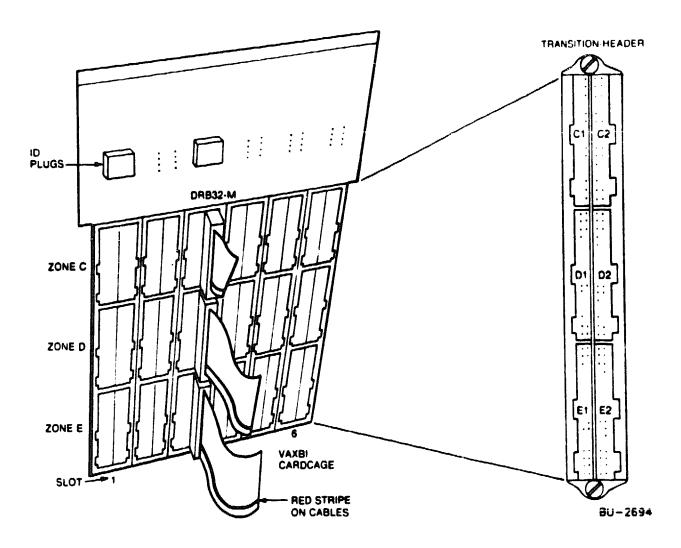

| 2-4        | Backplane and Transition Headers                     | 2-10 |

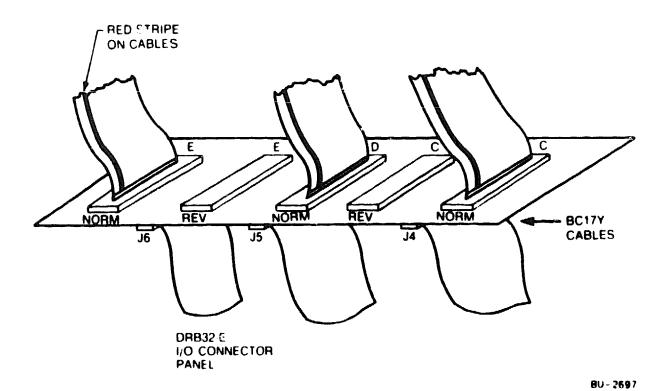

| 2-5        | DRB32-E I/O Connector Panel                          |      |

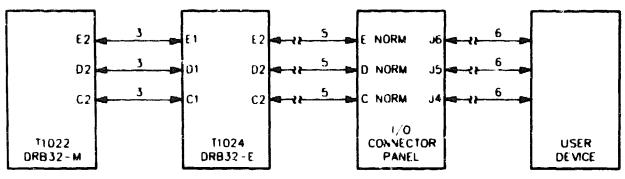

| 2-6        | Typical Configuration for the DRB32-E Option         |      |

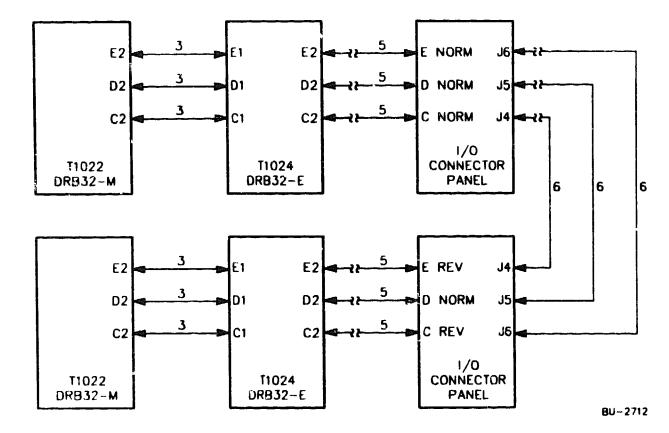

| 2-7        | Configuration for Back-To-Back DRB32-E Options       |      |

| 2-8        | DRB32-W Option                                       |      |

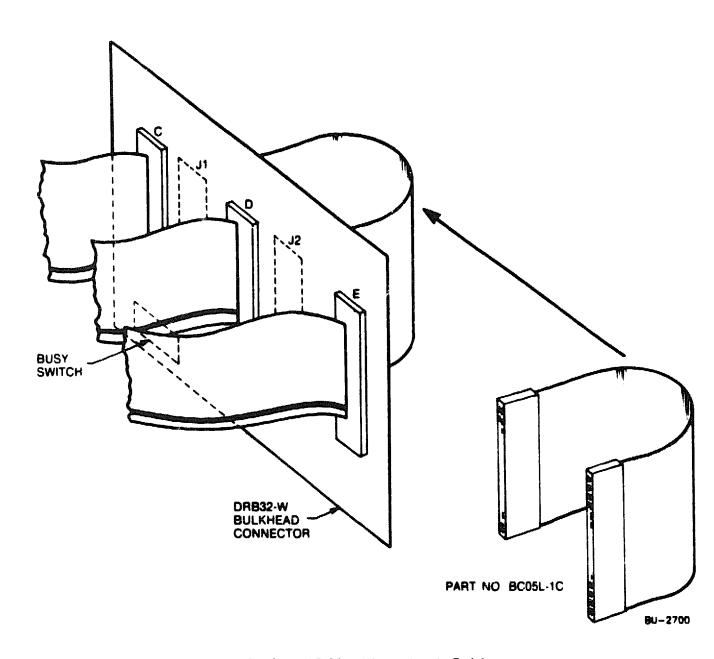

| 2-9        | DRB32-W Bulkhead Connector                           | 2-16 |

| 2-10  | Typical Configuration for the DRB32-W Option        |             |

|-------|-----------------------------------------------------|-------------|

| 3-1   | GPO Register                                        |             |

| 3-2   | Attaching A DRB32 For Internal Loopback Testing     |             |

| 3-3   | Selecting Default Tests                             |             |

| 3-4   | Test Failure Example                                |             |

| 3-5   | DRB32 Output Tester                                 |             |

| 3-6   | Data Lines Test                                     |             |

| 3-7   | Parity Lines Test                                   |             |

| 3-8   | Error on Testing                                    | 3-15        |

| 3-9   | DRB32-W Internal Loopback Test Example              |             |

| 3-10  | DEB32-W Test Error                                  |             |

| 3-11  | Improperly Set Switch Message                       |             |

| 3-12  | DRB32-W Loopback Cable                              | 3-20        |

| 3-13  | External Loopback Test Example                      | 3-21        |

| 3-14  | Running EVDRH Single-System LINK Test               | 3-25        |

| 3-15  | Running Single-System LINK Test: Test 1             | 3-25        |

| 3-16  | Single-System LINK Test: Test 1 Error Example       |             |

| 3-17  | Single-System LINK Test: Test 2 Example             | 3-28        |

| 3-18  | Single-System LINK Test: Test 2 Error Example       | 3-29        |

| 3-19  | Dual-System LINK Test Configuration                 |             |

| 3-20  | Sample of a Successful Test from the Master Console | 3-31        |

| 3-21  | Sample of a Successful Test from the Slave Console  |             |

| 3-22  | Master Console Error Message                        |             |

| 3-23  | Slave Console Error Message                         | 3-33        |

| 3-24  | Running EVDRI Single-System LINK Test               |             |

| A-1   | Pattern 1                                           |             |

| A-2   | Pattern 2                                           |             |

| A-3   | Pattern 3                                           |             |

| A-4   | Pattern 4                                           |             |

| A-5   | Pattern 5                                           |             |

| A-6   | Pattern 6                                           |             |

| A-7   | Parity Test 1                                       |             |

| A-8   | Parity Test 2                                       | A-5         |

| ables |                                                     | <del></del> |

| 2-1   | Contents of DRB32 Options                           | 2-2         |

| 2-2   | Cable Ordering Numbers                              |             |

| 3-1   | DRB32 Self-Test Tests                               |             |

| 3-2   | DRB32 Level 3 Tests                                 |             |

| 3-3   | EVDRH Section Names                                 |             |

| 3-4   | EVDRI Tests                                         |             |

| 3-5   | EVDRI Sections                                      |             |

|       |                                                     |             |

## Contents

| C-1 | ERRREG Error Codes                | C-1 |

|-----|-----------------------------------|-----|

| -   | Self-Test Error Codes             |     |

|     | BIIC Registers                    |     |

|     | DRR32 Parallel I/O Port Registers |     |

## **Preface**

## Purpose of this Manual

The DRB32 Hardware Installation Guide (EK-DRB32-IN) supplies installation information for the DRB32 adapter. It covers the hardware installation, information on how to run the diagnostics, and troubleshooting the DRB32 and option modules.

Information on installing the DRB32 software is in the DRB32 Programmer's Manual (AA-HZ25C-TE).

#### Intended Audience

This manual is for:

- Digital or customer personnel who install and repair this equipment in the field.

- Customer engineers and programmers who incorporate this equipment into their own product or system.

## Structure of this Manual

Chapter 1 describes the DRB32 adapter.

Chapter 2 describes installation of the DRB32 hardware.

Chapter 3 describes testing and verification of the DRB32 hardware.

Appendix A contains DRB32 Output Tester patterns.

Appendix B contains the error log format.

Appendix C lists the event rodes that can appear in the DRB32 ERREG Register.

Appendix D lists the self-test error codes.

Appendix E lists the DRB32 registers.

Appendix F is a glossary that describes the DRB32 hardware and software.

#### Related Manuals

The DRB32 adapter is one of a family of processors, memories, and adapters that uses the 32-bit VAXBI bus. For a technical summary of all VAXBI modules, system components, and integrated circuits, see the VAXBI Options Handbook (Order No. EB-27271-46).

Other related technical manuals are:

DRB32 Introduction

Order No. EK-DRB32-OV

An overview of the hardware, software, and use of the DRB32 adapter.

DRB32 Technical Manual Order No. EK-DRB32-TM

Description of the DRB32 hardware and functional operation for the hardware designer, including register descriptions, data path descriptions, pinouts, and VAXBI transactions.

DRB32 Programmer's Manual Order No. AA-HZ25C-TE

Description of the DRB32 software for the software programmer and designer, including device drivers, tools, example programs and test code. Also describes software installation procedures.

## System Installation Guide

Description of the cable management practices, how to access the VAXBI card cage, and other host-specific requirements.

## Conventions Used

- The DRB32 adapter is referred to as the DRB32. "DRB32" refers to the DRB32-M option, if no option is specified.

- The VAXBI bus is referred to as the VAXBI.

# 1 Introduction

The DRB32 Hardware Installation Guide describes the installation of the DRB32 hardware. This manual also includes information on DRB32 diagnostics, troubleshooting, and installing option modules. See the DRB32 Programmer's Guide for information on installing the DRB32 software.

## 1.1 Functional Description of the DRB32 Module

The DRB32 is an adapter that provides fast data transfers between Digital's VAXBI systems and user devices such as array processors, A/D converters, and high-speed instrumentation. The DRB32 meets the requirements of a VAXBI node, and therefore provides a simple connection for your devices to VAXBI systems. Large, fast data transfers are the major advantages of the DRB32. The DRB32 is optimized for large DMA transfers in **Block mode**.

Block mode allows for transfers up to 982,528 bytes without processor intervention. The DRB32 hardware has a double buffering capability that enables it to set up DMA transfers that are larger than this 982,528-byte limit. Data transfers can also be made in Data mode, in which a host processor on the VAXBI directly reads or writes the DRB32 register that sends and receives data from the user device.

The DRB32 uses map registers to translate virtual addresses to VAXBI physical addresses. The DRB32 map register area is 1919 longwords. Mapped adapters require a process running in a VAX computer to load map registers into the adapter for virtual-to-physical address conversion. Transfer widths are selected by the user—the DRB32 can handle longword (32-bit), word (16-bit), or byte (8-bit) transfers. However, the selection of 16- or 8-bit widths results in lower performance. The DRB32 uses odd parity.

#### Introduction

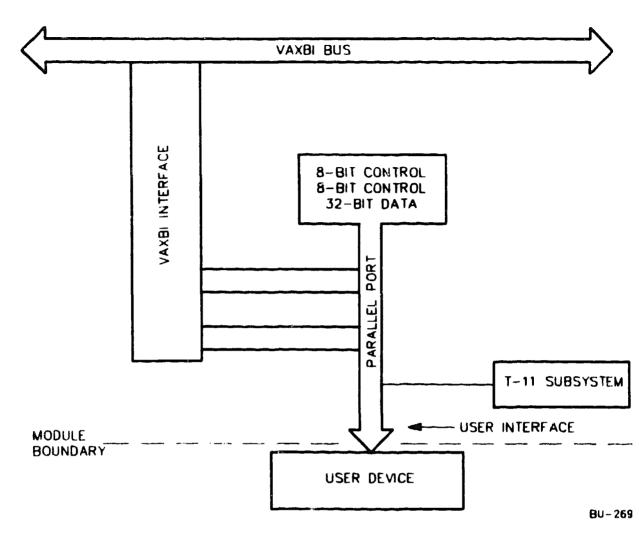

The major functional components of the DRB32 are the following:

- Parallel I/O port

- VAXBI interface

- T-11 subsystem

The DRB32 is a parallel I/O port (with a 32-bit half-duplex data path and dual 8-bit duplex control paths) that connects the VAXBI bus and a user device. At the VAXBI end, the DRB32 has a VAXBI interface corner. At the user device end, the DRB32 parallel port has a user interface with signals for data, control, and device status. Attached to the parallel I/O port is a T-11 subsystem that performs module self-test. A simplified block diagram of these three DRB32 functional components is shown in Figure 1-1 below.

Figure 1-1 DRB32 Simplified Block Diagram

## 1.2 DRB32 Configurations

The DRB32 is available in three configurations:

- DRB32-M

- DRB32-E

- DRB32-W

#### 1.2.1 DRB32-M Option

The DRB32-M is the basic intracabinet DRB32 option, designed for an application where all cabling is kept within a single cabinet. This option consists of the primary DRB32 module (T1022) and a set of cables. The DRB32-M is compliant with FCC Class A regulations when fully contained within an FCC-compliant cabinet. For a more detailed description of this option, see Section 2.2.1.

## 1.2.2 DRB32-E Option

The DRB32-E external cable-driving option can drive an intercabinet cable that is up to 40 feet long. The DRB32-E is for applications in which user equipment must be separate from the cabinet containing the DRB32. Therefore, a cable must connect the two cabinets. This option consists of the primary DRB32 module (T1022), the external driver module (T1024), an I/O connector panel, and cables. For a more detailed description of this option, see Section 2.2.2.

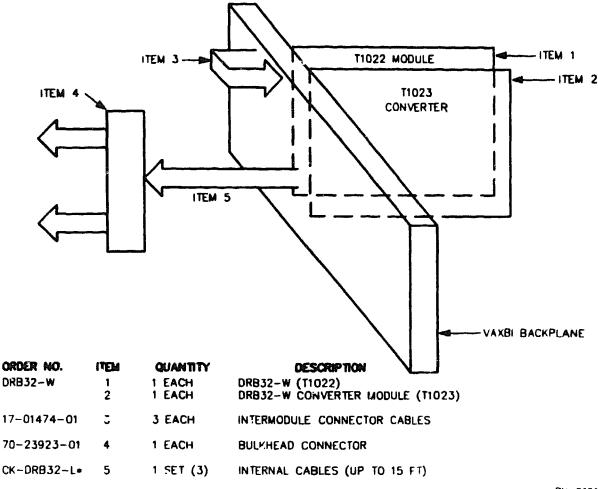

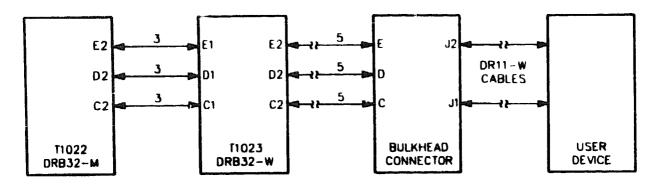

## 1.2.3 DRB32-W Option

The DRB32-W option provides a means of connecting DR11-W equipment to VAXBI systems. The DRB32-W is for intracabinet use. It consists of the primary DRB32 module (T1022), a DR11-W converter module (T1023), a bulkhead connector, and cables. For a more detailed description of options, see Section 2.2. For a more detailed description of this option, see Section 2.2.3.

## 1.3 DRB32 Software

The DRB32 software is included in a VMS layered product called DRB32VMSDRIVERS and must be ordered separately.

The following software is available for the DRB32-M and DRB32-E:

- VMS device driver (UQDRIVER) for the DRB32-M/-E

- Test code for drivers (DRB32\$QIO)

- Subroutine package for communications between two VAXBI systems through a back-to-back DRB32 link (DRB32\$MESSAGE)

- MACRO and object libraries

- Command procedures to load and build the driver and test programs

The following software is available for the DRB32-W:

- VMS device driver (UQWDRIVER) for the DRB32-W

- Test code for drivers (DRB32\$WQIO)

- MACRO and object libraries

- Command procedures to load and build the driver and test programs

The software listed above is described in the *DRB32 Programmer's Manual*, as are the instructions for software installation and verification.

Hardware diagnostics are available and are described in Chapter 3 of this manual.

## 2

## **DRB32 Hardware Installation Procedures**

This chapter describes the hardware installation of the DRB32-M, the DRB32-E, and the DRB32-W.

#### CAUTION

You must wear an antistatic wrist ground strap while working on a VAXBI system with its covers removed or when handling any VAXBI module. Do not remove any module from its antistatic packaging until you are ready to `nstall it.

## 2.1 Summary of Installation Tasks

The following steps are necessary for successful installation of the DRB32 options.

- 1. Unpack and inspect the Installation Kit.

- 2. Check VAXBI configuration.

- 3. Install the DRB32 module(s).

- 4. Install internal cables.

- 5. Install, if necessary, transition header(s), I/O connector panel, and/or bulkhead connector.

- 6. Install, if necessary, any external cables.

- 7. Test and verify the installation.

#### 2.1.1 Site Preparation

There is no special site preparation necessary for the installation of any of the DRB32 options. To install the DRB32, there must be space in the VAXBI card cage. If you are installing a DRB32-E or DRB32-W, two contiguous VAXBI slots in the same cage are needed.

#### WARNING

It is essential that all devices be connected to the same line-power bus to ensure that all devices have the same chassis ground. A danger to personnel and a fire hazard exist when various devices have different chassis ground potentials.

#### 2.1.2 DRB32 Option Components

The DRB32 and any associated option modules, I/O connector panels, and bulkhead connectors are supplied in the installation kits. Use Table 2-1 to check the contents of the installation kit. Examine each part for damage and make sure all parts are present. Report any damage to the shipper and to the local Digital office. Requisition any missing parts.

Three installation kits are available for the three DRB32 options. The contents of these three kits are described in Table 2-1.

Table 2-1 Contents of DRB32 Options

| Part Number | Description                          | DRB32-M<br>Option | DRB32-E<br>Option | DRB32-W<br>Option |

|-------------|--------------------------------------|-------------------|-------------------|-------------------|

| T1022-AA    | DRB32-M Module                       | 1                 | 1                 | 1                 |

| T1024-AA    | DRB32-E External Driver Module       | 0                 | 1                 | 0                 |

| T1023-YA    | DRB32-W Converter Module             | 0                 | 0                 | 1                 |

| 17-01474-01 | Intermodule Cable                    | 0                 | 3                 | 3                 |

| 70-23924-01 | I/O Connector Panel                  | 0                 | 1                 | 0                 |

| 70-23923-01 | <b>Bulkhead Connector</b>            | 0                 | 0                 | 1                 |

| EK-DRB32-IN | DRB32 Hardware<br>Installation Guide | 1                 | 1                 | 1                 |

Cabinet kits, internal cables, and external cables are not part of the installation kit and are ordered separately. The customer orders any of the following cables for installation of their equipment. Each part number represents a set of three cables. For the DRB32-M and for the DRB32-W, there must be one set of internal cables. For the DRB32-E, there must be a set of internal cables and a set of external cables. See Table 2-2.

Table 2-2 Cable Ordering Numbers

| Option Number | Description                                    | DEC Part Number |  |

|---------------|------------------------------------------------|-----------------|--|

| CK-DRB32-LJ   | Set of Three Internal Cables<br>5-foot Length  | 17-01375-02     |  |

| CK-DRB32-LM   | Set of Three Internal Cables<br>10-foot Length | 17-01375-03     |  |

| CK-DRB32-LN   | Set of Three Internal Cables<br>15-foot Length | 17-01375-04     |  |

| BS17Y-20      | Set of Three BC17Y-20 External Cables, 20 feet | 17-00445-06     |  |

| BS17Y-40      | Set of Three BC17Y-40 External Cables, 40 feet | 17-00445-09     |  |

## 2.1.3 Configuration Rules

The DRB32 address space is determined by the NODE plug associated with the slot where the module is located. You do not have to set any jumpers or special addresses to install the hardware. There are, however, some VAXBI rules that must be followed. These rules apply in all VAXBI systems.

- 1. No DRB32 module can be placed in slot J1K1 (the rightmost slot).

- 2. The DRB32-E or DRB32-W requires two adjacent VAXBI slots in the same cage. The DRB32-M module (T1022) goes in the rightmost of the two slots.

- 3. The VAXBI node ID for the DRB32 must be unique. The node ID is found on a plug on the backplane, opposite to the slot containing the DRB32-M module. VAXBI systems are shipped with node plugs already installed.

There may be other system-dependent configuration restrictions, such as those imposed by backplane capacity, or physical mounting limitations in the cabinet. Such restrictions are described in the host system documentation.

## 2.2 Option Installation

#### WARNING

Remove all power to the system before performing the module installation.

## CAUTION

You must wear an antistatic wrist ground strap while working on a VAXBI system with its covers removed or when handling any VAXBI module. Do not remove any module from its antistatic packaging until you are ready to install it.

#### 2.2.1 DRB32-M Installation

Figure 2-1 shows how the DRB32-M fits together mechanically. Use the figure and the following instructions to install the option.

Figure 2-1 DRB32-M Module

BU-2691

Follow the steps below for installing the DRB32-M.

1. Expose the back of the VAXBI card cage.

#### DRB32 Hardware Installation Procedures

- 2. Insert the DRB32 (T1022) module into an empty VAXBI slot, following the configuration rules in section 2.1.3. All VAXBI modules are keyed to prevent incorrect installation.

- 3. Ensure that a unique node ID plug is present on the VAXBI backplane in the slot where the T1022 module has been placed.

- 4. If necessary, install the transition header (PN 12-22246-01) for the slot in question using the torque screwdriver (PN 29-17381-00). Set the value on the screwdriver to 6 inch pounds. Note that the accuracy of the torque is valid only when the screw is in motion. See Figure 2-2.

Figure 2-2 Transition Header Installation

- 5. Attach the three cables (CK-DRB32-L\*) to section C2, D2 and E2 of the transition header. See Figure 2-4.

- 6. Run the cables inside the cabinet to whatever location the customer designates. Use common cable management practices as described in the System Installation Guide when performing this operation.

- 7. Continue the installation by following the steps in the test and verification section of this manual.

#### 2.2.2 DRB32-E Installation

Figure 2-3 shows how the DRB32-E fits together mechanically. Use the figure and the following instructions to install the option.

Figure 2-3 DRB32-E Option

Follow the steps below for installing the DRB32-E.

1. Expose the back of the VAXBI card cage.

- 2. Insert the DRB32 (T1022) module into an empty VAXBI slot, following the configuration rules in section 2.1.3. All VAXBI modules are keyed to prevent incorrect installation.

- 3. Insert the external driver module (T1024) into the slot to the left of the T1022 module.

- 4. Ensure that a unique node ID plug is present on the VAXBI backplane in the slot where the T1022 module has been placed.

- 5. If necessary, install two transition headers (PN 12-22246-01) for the slots in question using the torque screwdriver (PN 29-17381-00). Set the value on the screwdriver to 6 inch pounds. Note that the accuracy of the torque is valid only when the screw is in motion. See Figure 2-2: Transition Header Installation.

- 6. Place the three intermodule cables (part number 17-01474-01) on sections C, D and E of the transition header connecting the two modules. The transition headers are split vertically and the cables are plugged into adjacent sections of both slots. Refer to Figure 2-4: Backplane and Transition Headers. Cables go from C2 of the T1022 slot to C1 of the T1024 slot, from D2 of the T1022 slot to D1 of the T1024 slot, and from E2 of the T1022 slot to E1 of the T1024 slot.

- 7. Install the I/O connector panel to the I/O section of the system.

#### WARNING

It is essential that all devices be connected to the same line-power bus to ensure that all devices have the same chassis ground. A danger to personnel and a fire hazard exists when various devices have different chassis ground potentials.

Figure 2-4 Backplane and Transition Headers

8. If only one DRB32-E is being installed in the system, follow the instructions in (a) below. If two DRB32-Es are being installed, follow the instructions in (b). Refer to Figure 2-5: DRB32-E I/O Connector Panel.

### CAUTION

Cables CK-DRB32-L have a ground bus bar. Incorrect installation causes the DRB32 bus to malfunction. Ensure that the red stripes on the cables are installed on pin 30, as shown in Figure 2-4.

Figure 2-5 DRB32-E I/O Connector Panel

a. Install the three cables (part number CK-DRB32-L\*), from the transition header of the external driver module to the I/O connector panel. Cables go from C2 of the T1024 slot to C NORM on the I/O connector panel, from D2 of the T1024 slot to D NORM on the I/O connector panel, and from E2 σ<sup>c</sup> the T1024 slot to E NORM on the I/O Panel. See Figure 2-4 and Figure 2-6: Typical Configuration for the DRB32-E Option.

BU-2711

Figure 2-6 Typical Configuration for the DRB32-E Option

b. Install the three cables for one DRB32-E as in (a) above. Install the three cables for the second DRB32-E from the transition header of the second external driver module to the second I/O connector panel. Cables go from C2 of the second T1024 slot to C REV on the I/O connector panel, from D2 of the second T1024 slot to D NORM on the I/O connector panel, and from E2 of the second T1024 slot to E REV on the I/O connector panel. See Figure 2-4: Backplane and Transition Headers and Figure 2-7: Configuration for Back-To-Back DRB32-E Options.

Figure 2-7 Configuration for Back-To-Back DRB32-E Options

- 9. Run the cables inside the cabinet between the transition header and the I/O connector panel. Use common cable management practices as described in the System Installation Guide when performing this operation.

- 10. Install the BS17Y-20 or -40 cables from the outside of the I/O connector panel to whatever location the customer designates using common cable management.

- 11. Continue the installation by following the steps in the test and verification section of this manual.

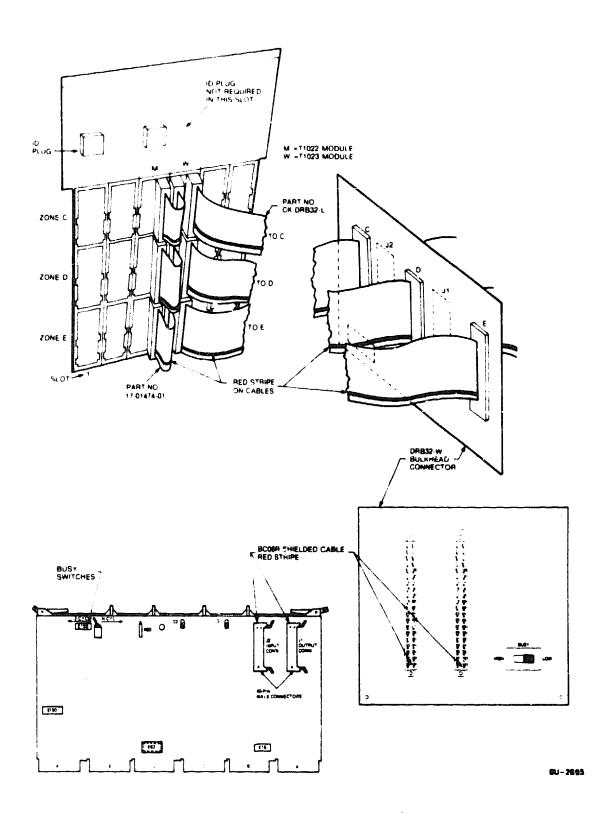

#### 2.2.3 DRB32-W Installation

Figure 2-8 shows how the DRB32-W fits together mechanically. Use the figure and the following instructions to install the option.

#### NOTE

The DRB32-W went through a redesign. For an explanation of the two DRB32-W versions, please refer to the *DRB32 Technical Manual* (EK-DRB32-TM-003), Appendix C. Both the DRB32-W versions are installed, tested, and verified the same way. If you follow the steps listed in sections 2.2.3 and 3.4, you will have completed the DRB32-W option installation.

BU - 2696

Figure 2-8 DRB32-W Option

Use the following steps to install the DRB32-W option.

- 1. Expose the back of the VAXBI card cage.

- 2. Insert the DRB32 (T1022) module into an empty VAXBI slot, following the configuration rules in section 2.1.3. All VAXBI modules are keyed to prevent incorrect installation.

- 3. Insert the converter module (T1023) into the slot to the left of the T1022 module.

- 4. Ensure that a unique node ID plug is present on the VAXBI backplane in the slot where the T1022 module has been placed.

- 5. If necessary, install two transition headers (PN 12-22246-01) for the slots in question using the torque screwdriver (PN 29-17381-00). Set the value on the screwdriver to 6 inch pounds. Note that the accuracy of the torque is valid only when the screw is in motion. See Figure 2-2: Transition Header Installation.

- 6. Place the three intermodule cables (part number 17-01474-01) on sections C, D and E of the transition header connecting the two modules. The transition headers are split vertically and the cables are plugged into adjacent sections of both slots. Refer to Figure 2-4: Backplane and Transition Headers. Cables go from C2 of the T1022 slot to C1 of the T1023 slot, from D2 of the T1022 slot to D1 of the T1023 slot, and from E2 of the T1022 slot to E1 of the T1023 slot.

- 7. Install the bulkhead connector to a convenient location on the cabinet frame.

- 8. Install the three cables (part number CK-DRB32-L\*) from the transition header of the T1023 to the bulkhead connector. Cables go from C2 of the T1023 slot to C on the bulkhead connector, from D2 of the T1023 slot to D on the bulkhead connector, and from E2 of the T1023 slot to E on the bulkhead connector. See Figure 2-9: DRB32-W Bulkhead Connector.

Figure 2-9 DRB32-W Bulkhead Connector

9. If the DR11-W cables are being removed from an existing DR11-W, refer to Figure 2-9 and disconnect the DR11-W cable from DMA module J1 and connect it to the bulkhead connector J1 so that what was DMA module J1-pin A goes to bulkhead connector J1-pin 1 (which forces what was DMA module J1-pin VV to go to J1-pin 40). Then, disconnect the DR11-W cable from DMA module J2 and connect it to the bulkhead connector J2 so that what was DMA module J2-pin A goes to bulkhead connector J2-pin 1 (which forces what was DMA module J2-pin VV to go to bulkhead connector J2-pin 40).

#### CAUTION

When using BC06R-XX shielded cables, ensure that the red stripe is connected from DR11-W pin VV to bulkhead connector pin 40 (down) so that the shield is connected to ground. See Figure 2-9. If the cables were connected "red stripe up," at the bulkhead connector, then the shield would be connected to data bit 15 (D<15>H) and signal integrity for bit 15 would be lost.

10. If the DR11-W cables are being removed from an existing DR11-W, note the position of the DR11-W switches 1 and 2. Set the BUSY switch on the bulk-head connector as follows:

| Bulkhead<br>Connector<br>Switch |     | DR11-W<br>Switches |  |  |

|---------------------------------|-----|--------------------|--|--|

| BUSY                            | 1   | 2                  |  |  |

| HIGH                            | ON  | OFF                |  |  |

| LOW                             | OFF | ON                 |  |  |

11. Continue the installation by following the steps in the test and verification section of this manual.

Figure 2-10 Typical Configuration for the DRB32-W Option

BU - 2692

## 3

## **Test and Verification**

This chapter includes information on:

- Testing and verification of the DRB32 hardware

- The DRB32 diagnostic tools

- Troubleshooting

If the customer has ordered the DRB32 software, a VMS layered product called DRB32VMSDRIVERS, the included *DRB32 Programmer's Manual* describes the software Installation Verification Procedure (IVP) in Chapter 2.

## 3.1 Test and Verification

To test and verify the installation of the DRB32-M, the DRB32-E, and the DRB32-W, run the following tests.

- 1. Self-Test (runs on power-up)

- 2. EVDRH (default for the -M module)

- 3. EVDRH (DRB32\_EXTERNAL)—External Loopback mode. Use the DRB32 output tester for the DRB32-M and DRB32-E.

- 4. EVDRI (default for the DRB32-W module)

- 5. EVDRI (DRBW\_EXTERNAL)—External Loopback mode. Use the DRB32-W external loopback cable for the DRB32-W.

Self-test only exercises the DRB32-M module (the basic DRB32 board). Although the yellow LEDs light on both the DRB32-E external driver module and the DRB32-W converter module, no self-test is actually performed. On these two modules, the LED is tied to +5 volts (so that a quick inspection of the LEDs does not result in your swapping

out a good module). The LEDs on these two modules light even if the DRB32-M has not passed its internal self-test. Use EVDRH to test the DRB32-M, DRB32-E, and cables. EVDRI tests the DRB32-W.

By default, the EVDRH puts the DRB32 into Internal Loopback mode. When this occurs, the DRB32 bus drivers are disabled and will NOT put signals out onto the DRB32 bus. However, the rest of the DRB32 logic (excluding the bus drivers) is tested. EVDRH can also be run in an External Loopback mode that, with the use of the DRB32 output tester, tests the bus drivers and the cables. See the section on troubleshooting for details. Installation verification includes both default and external loopback tests. These diagnostic tests are described in the following sections.

### 3.2 Self-Test

Self-test for the DRB32-M (T1022) is located in ROM from address 160000 octal to 171776 octal and is executed by the T-11 processor on the DRB32. Successful completion of the DRB32-M self-test lights the yellow LED on the DRB32-M. For the VAX 8200, the console indicates which VAXBI nodes have passed self-test, by printing their node numbers. Nodes that have failed self-test are indicated by printing their node number preceded by a minus sign.

Neither the DRB32-E external driver module nor the DRB32-W converted module have self-tests on board; their LEDs are lit by tying them to +5 volts. The LEDs on the DRB32-E and DRB32-W light whether or not the DRB32-M has passed its internal self-test. (The purpose of these LEDs is to prevent mistakes in swapping out a DRB32-E or DRB32-W module that works.)

### 3.2.1 Normal Self-Test

Self-test uses the tests shown in Table 3-1 to exercise the logic on the DRB32-M. Note that tests 9 and A test two functions.

| Table 3 | 2_1   | DPR32  | Self-Test | Tosts |

|---------|-------|--------|-----------|-------|

| ININE . | 1 - I | 118933 |           |       |

| Test<br>Number | Name           | Function                                                                                                                    |

|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1              | T-11 Processor | Tests function of T-11 chip by exercising instruction set, address modes, data paths, stack, registers, and other functions |

| 2              | ROM Checksum   | Tests for "stuck at" faults in data and address paths of T-11 subsystem to ROM (where self-test resides)                    |

| Table 3-1      | DRB32 Self-Test Tes                        | sts (Continued)                                                                                                                                                                                                                                                                                                                                |

|----------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test<br>Number | Name                                       | Function                                                                                                                                                                                                                                                                                                                                       |

| 3              | T-11 RAM                                   | Tests T-11 RAM subsystem by alternately writing and reading As and 5s through ascending and descending addresses                                                                                                                                                                                                                               |

| 4              | CB RAM                                     | Tests DRB32 Central Bus RAM by alternately writing and reading As and 5s through ascending and descending addresses                                                                                                                                                                                                                            |

| 5              | Map Registers                              | Tests DRB32 map registers by alternately writing and reading As and 5s through ascending and descending addresses                                                                                                                                                                                                                              |

| 6              | BCAI Register                              | Tests BCAI chip registers by alternately writing and reading As and 5s through ascending and descending register addresses                                                                                                                                                                                                                     |

| 7              | Map Port BIIC<br>Response                  | Tests DRB32 map port by writing and reading data through port to CB RAM using VAXBI loopback transactions                                                                                                                                                                                                                                      |

| 8              | Map Port VAXBI<br>Response                 | Tests DRB32 map port by writing and reading data through port to CB RAM using VAXBI transaction                                                                                                                                                                                                                                                |

| 9              | DMA Port / CSC<br>Interrupt                | Tests two functions: 1) Tests DMA port by doing DMA data transfer from CB RAM to IODAT register (using CURRENT map registers) and DMA data transfer from IODAT register to CB RAM (using the NEXT map registers)  2) Tests that T-11 can be interrupted (when interrupts are enabled) when a current segment transfer on DMA port is completed |

| Α              | Physical Address<br>Parity/Error Interrupt | Tests two functions: 1) Tests that a (generated) parity error is detected during DMA transfer on address portion of a transfer 2) Tests that T-11 can be interrupted (when interrupts are enabled) when an error is detected on the DRB32                                                                                                      |

| В              | Data Parity Error                          | Tests that a (generated) data parity error is detected on data during loopback transactions                                                                                                                                                                                                                                                    |

| C              | VAXBI Interrupt                            | Tests VAXBI interrupts                                                                                                                                                                                                                                                                                                                         |

| Table 3-1 | DRR32 | Self-Test Tests | (Continued) |

|-----------|-------|-----------------|-------------|

| 141HC 3-1 | URDJZ | Jeniest rests   | (COMMINGE)  |

| Test<br>Number | Name                  | Function                                                                                                                               |

|----------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| D              | Control Bus Interrupt | Tests that an interrupt is generated (when interrupts are enabled) when a change of state on the 8-bit input control lines is detected |

| E              | Register Test         | Tests DRB32 registers not used in any test above                                                                                       |

If self-test fails, General Purpose Register 0 (at address bb+F0) contains the test number in the high order word and the error number in the low order word. For example, refer to Figure 3-1 and let us assume that a DRB32 residing at node 6 (base address 6000C000) has failed self-test on power up. By examining GPR0, we can see that test 7 has failed and with an error number of 2. The direct cause of the error can quickly be traced through the self-test listing (if self-test passes, GPR0 returns a 0).

Figure 3-1 GP0 Register

Refer to Appendix D for the Self-Test Error Code List. Self-test does VAXBI loopback transactions and reads and writes the module's own node space, but does not do the entire range of VAXBI transactions possible to the DRB32. Therefore, self-test does not test the interaction of the DRB32 with any other device on the VAXBI.

### NOTE

No self-test is performed on either the DRB32-E external driver module or the DRB32-W converter module, even though an LED is lit on these boards.

### 3.2.2 Fast Self-Test

Fast self-test is executed when the Fast Self-Test bit in the T-11 CB RAM location register is cleared. Fast self-test only executes Test 7 and Test 9. (See Table 3-1 above.)

## 3.3 EVDRH (VAX Level 3 Functional Diagnostic)

EVDRH is a VAX level 3 diagnostic that runs under the control of the VAX Diagnostic Supervisor (VDS). Since EVDRH runs in the system CPU on the VAXBI, VAXBI transactions are possible, enabling further testing of the DRB32 microcode and hardware. (There is no plan for a DRB32 VAX level 2 diagnostic, since the DRB32 device driver is likely to be developed/modified by the customer.)

Since the DRB32 is used as an interface to user devices, it is not advisable for a diagnostic to put data onto the DRB32's output bus, because such data might damage the user device. Therefore, EVDRH (and also self-test) tri-states the DRB32's drivers, preventing signals from being transmitted onto the output bus. However, you can test the output buses and the DRB32 drivers with the use of the DRB32 output tester, which is described in the next two sections.

EVDRH includes the tests shown in Table 3-2.

| Table 3-2      | DRB32 Level 3 Test                         | S                                                                                                                               |

|----------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Test<br>Number | Name                                       | Function                                                                                                                        |

| 1              | DRB32 Control and<br>Device Type Registers | Tests that device type corresponds to the DRB32                                                                                 |

| 2              | BHC and DRB32 Self-<br>Test Check          | Tests that BHC and DRB32 both passed self-<br>test                                                                              |

| 3              | BIIC and DRB32<br>Required Registers       | Tests required registers on DRB32 are accessible, fields that can be written are writable, fields that can be read are readable |

| 4              | DRB32 CB RAM<br>March                      | Tests DRB32 Central Bus RAM by alternately writing and reading As and 5s through ascending and descending addresses             |

| 7              | 32-Bit VAXBI-to-Port<br>Octaword Transfer  | Tests if DRB32 can read data from VAXBI memory using octaword transfers on VAXBI                                                |

| 6              | 32-Bit Port-to-VAXBI<br>Octaword Transfer  | Tests if DRB32 can write data to VAXBI memory using octaword transfers on VAXBI                                                 |

|  | Table 3-2 | DRB32 | Level 3 | Tests | (Continued) |

|--|-----------|-------|---------|-------|-------------|

|--|-----------|-------|---------|-------|-------------|

| Test   |                                        |                                                                                                                                      |

|--------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Number | Name                                   | Function                                                                                                                             |

| 7      | Page Overflow                          | Tests if data can be transferred to and from DRB32 across page boundaries in VAXBI memory                                            |

| 8      | Byte Offset                            | Tests if data byte can be transferred to and from DRB32, regardless of its location in the two DRB32 octaword buffers                |

| 9      | 32-Bit VAXBI-to-Port<br>Block Transfer | Tests that data blocks can be transferred to and from DRB32 to VAXBI memory, looping back data on DRB32                              |

| 10     | Parity Error                           | Tests if parity errors are detected on both address and data                                                                         |

| 11     | Dual Transfer                          | Tests continuous transfer feature by using both CURRENT and NEXT registers to transfer data to and from DRB32                        |

| 12     | Control Bus Interrupt                  | Tests if VAXBI interrupt can be generated by DRB32's CTRL IN lines                                                                   |

| 13     | Error Interrupt                        | Tests if VAXBI interrupt request is generated by DMA transfer error                                                                  |

| 14     | Single-System LINK Cable Test          | Tests ability of two DRB32s in same system to communicate via their cable link                                                       |

| 15     | Single-System LINK<br>Data Test        | Tests ability of two DRB32s in same system to transfer data to each other                                                            |

| 16     | DRB32 External<br>Loopback Test        | Tests integrity of the DRB32 data path (drivers, receivers, cables); test requires use of DRB32 Output Tester and its loopback cable |

| 17     | Dual-System (cab) Link                 | Tests ability of two DRB32-Es in different systems to communicate; can be used to verify that DRB32s work together                   |

The EVDRH diagnostic has several sections and section names. These section names (and the tests that each section performs) are shown in Table 3-3.

Table 3-3 EVDRH Section Names

| Section Names            | Tests Performed                                                                                      |  |

|--------------------------|------------------------------------------------------------------------------------------------------|--|

| 1) DEFAULT               | (All DRB32 internal loopback tests) Tests 1 - 13                                                     |  |

| 2) SELFTEST_CONTROL      | Allows control of self-test: can cause self-test to loop on error, loop on test, halt on error, etc. |  |

| 3) DRB32_EXTERNAL        | Runs DRB32 external loopback test                                                                    |  |

| 4) SINGLE_CAB_LINK       | Runs LINK test with two DRB32s in a single-system                                                    |  |

| 5) MASTER_DUAL_CAP _LINK | Runs LINK test with two DRB32s in different systems                                                  |  |

| 6) SLAVE_DUAL_CAB_LINK   | Runs LINK test with two DRB32s in different systems                                                  |  |

### 3.3.1 Running EVDRH

To run EVDRH, first boot the VAX Diagnostic Supervisor (VDS), (for specific VDS boot procedures, refer to the appropriate processor technical manual), load the diagnostic, attach the device(s) under test, and start the appropriate section.

Figures 3-2 through 3-4 are examples of the terminal output produced when you attach a DRB32 for the internal loopback test section of EVDRH, run the test, and have an error.

Copyright Digital Equipment Corporation 1986, 1987, 1988, 1989, 1990 All Rights Reserved.

DIAGNOSTIC SUPERVISOR, ZZ-EBSAA-X12.6-1996 8-MAR-1990 03:43:20 DS> load evdrh

Copyright Digital Equipment Corporation 1986, 1987, 1988, 1989, 1990 All Rights Reserved.

CONFIDENTIAL DIAGNOSTIC SOFTWARE PROPERTY OF DIGITAL EQUIPMENT CORPORATION

Use authorized only pursuant to a valid Right-to Use License.

DS> att

Device type? drb32

Device Link? hub

Device Name? uq1

Node? 6

BR? 4

DS> set tra,h

DS> sel all

DS>

Figure 3-2 Attaching a DRB32 for Internal Loopback Testing

Once the DRB32 has been attached and selected, the internal loopback (default) tests can be run as shown in Figure 3-3.

```

DS> st

.. Program: EVDRH - DRB32-M, -E Functional Diagnostic, revision 1.1,

16 tests, at 00:00:57.09.

Testing: _UU1

Test 1: DRB32 Control And Device Type Registers Test

Test 2: BIIC and DRB32 Self Test Check Test

Test 3: BI/DRB32 Required Registers Test

Test 4: DRB32 CB RAM March Test

Test 5: 32 Bit BI to Port Octaword Transfer Test

Test 6: 32 Bit Port to BI Octaword Transfer Test

Test 7: Page Overflow Test

Test 8: Byte Offset Test

Test 9: 32 Bit BI to Port Block Transfer Test

Test 10: Parity Error Test

Test 11: Dual Transfer Test

Test 12: Control Bus Interrupt Test

.. End of run, 0 errors detected, pass count is 1,

time is 8-MAR-1990 03:48:48.88

DS>

```

Figure 3-3 Selecting Default Tests

If the DRB32 is malfunctioning, an error is output to the user during the failing test. This is illustrated in Figure 3-4.

Figure 3-4 Test Failure Example

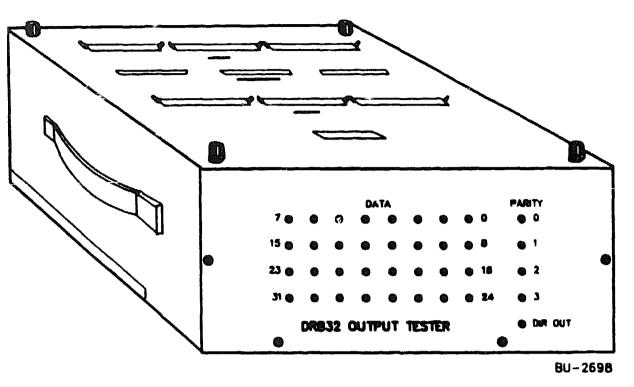

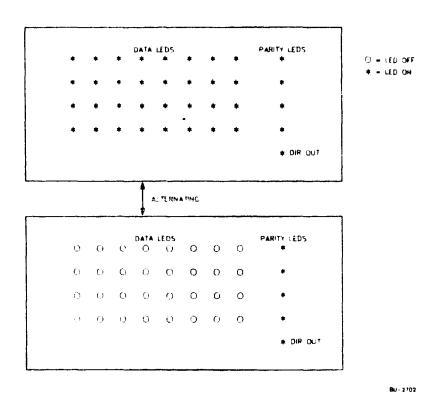

### 3.3.2 DRB32 Output Tester

#### NOTE

The DRB32 Output Tester can only be run by a qualified Digital representative.

The DRB32 output tester is a receiving device to test the DRB32's output drivers and cables without damaging user devices or causing unpredictable events. Since the DRB32 is a half-duplex device, the DRB32 output tester provides a means of testing hardware without sending data out to user devices. The DRB32 output tester is used with EVDRH. To test the DRB32's output bus, you must disconnect the user device. The DRB32 output tester can be attached to either an I/O connector panel, the VAXBI backplane, or to cables running from the backplane to the I/O connector panel, thus providing a way to isolate malfunctioning cables or drivers.

The DRB32 output tester consists of 37 LEDs mounted on a PC card in a box, with connector plugs on the top. Provided cables are plugged into these connectors and allow testing of the:

- 1. Output drivers on the DRB32-M

- 2. Cable between the DRB32-M and the DRB32-E or a user device

- 3. Output drivers on the DRB32-E

- 4. Cable between the DRB32-E and the I/O connector panel

- 5. Signals coming from the DRB32-E's I/O connector panel

- 6. Output of the FCC compliant cables that run from the I/O connector panel to the user device.

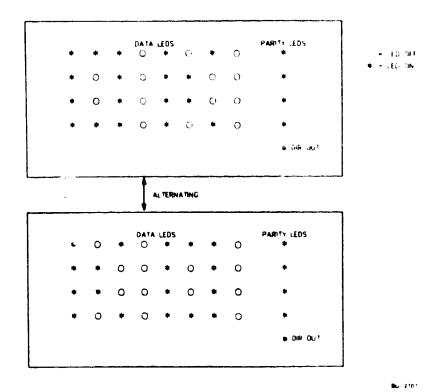

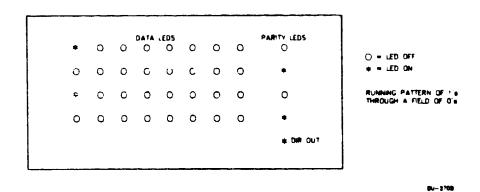

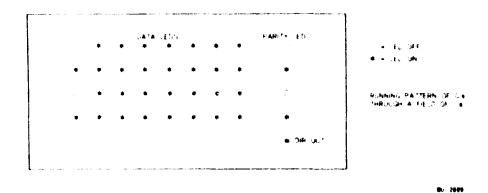

A drawing of the DRB32 output tester LED placement is shown in Figure 3-5.

Figure 3-5 DRB32 Output Tester

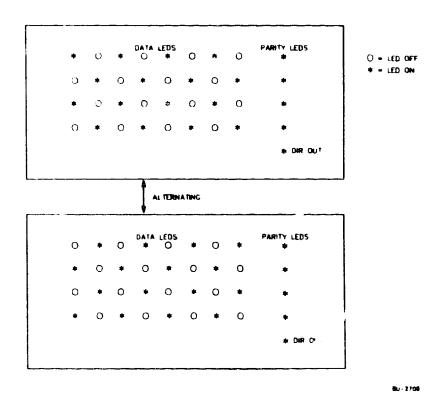

Thirty-two LEDs are tied to bits 0-31 on the output bus. Four LEDs are tied to the parity bits associated with each byte of data, and one LED is tied to the signal DIR OUT. Each LED is labeled on the Tester. The Control signals on the control bus are looped back (CTRL OUT L <0-7> to CTRL IN L <0-7>). CTRL OUT <7> is also tied to DIR IN so that direction on the bus may be established.

The external loopback test diagnoses, first, the data path to the DRB32 transceivers and then the data path from the transceivers to the outside world. The DRB32 output tester is used only when the data path to the transceivers is known to be good. If it is not, an error message is reported and the DRB32 output tester portion of the test does not run. To run the external loopback test, simply attach the DRB32 (if you have not already done so previously) and type:

#### DS> STA/SEC=DRB32\_EXTERNAL

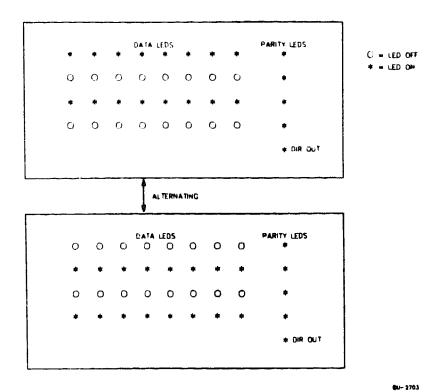

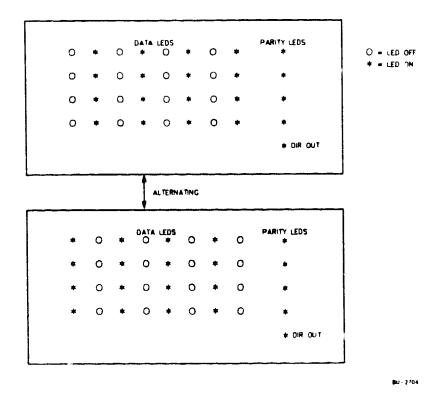

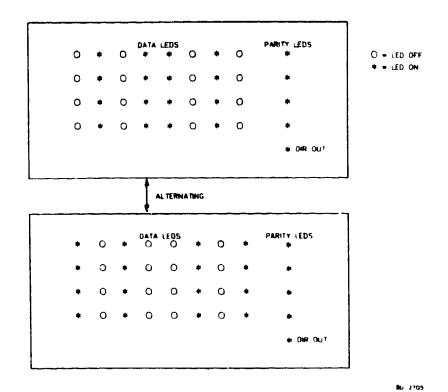

Figure 3-6 shows the instructions that appear on your terminal for the data line test if the data path to the transceivers is good. After you type "GO" to proceed with the test and before you press RETURN to display the first pattern, ensure that the tester is displaying "OK", as shown in the top of Figure A-6.

```

DS> sta

.. Program: EVDRH - DRB32-M, -E Functional Diagnostic, revision 1.1,

16 tests, at 00:32:34:02.

Testing: _UQ1

Test 16: DRB32 External Loopback Test Routine

WARNING: Make sure the loopback connector, cables, etc. are connected

properly. Failure to do so could result in damage to the user

equipment.

Type "'GO'' when you are ready to proceed with the test [GO] go

PART I: Data Lines Test

This test attempts to verify the integrity of the 32

data lines which interface the DRB32 directly to the

outside world. Pay close attention to only those LEDs

which comprise the data field; the parity LEDs (right-

most) can be ignored for now. The object of the test

is to ensure that each adjacent LED (e.g., data lines)

will respond completely independent of any other LED.

If not, then a short or open exists at the data line in

question.

MOTE: The patterns will be output to the loopback connector

in 6 sets of 2 patterns each. This is to facilitate easy

viewing and quick verification of the integrity of the data

lines.

Press RETURN when ready to proceed with the test (<CR>):

enattern set number 1 is now being displayed)

Press RETURN when ready to proceed with the test (<CR>):

(Pattern set number 2 is now being displayed)

Press RETURN when ready to proceed with the test (<CR>):

<Pattern set number 3 is now being displayed>

Press RETURN when ready to proceed with the test (<CR>):

«Pattern set number 4 is now being displayed»

Press RETURN when ready to proceed with the test (<CR>):

(Pattern set number 5 is now being displayed)

Press RETURN when ready to proceed with the test [ < CR> ]:

(Pattern set number 6 is now being displayed)

Press RETURN when ready to proceed with the test fcCR>1:

```

Figure 3-6 Data Lines Test

The instructions in Figure 3-7 appear on your terminal for the parity lines test.

PART II: Parity Lines Test

This test attempts to verify the integrity of the 4 parity lines (rightmost) associated with the 32 data lines. As in the previous test, the object is to ensure that each parity line will respond independent of any other parity line. This is accomplished by running two is through a field of 0s. The important thing is to verify that the parity lines respond by reading, alternately, 1010 and 0101

Press RETURN when ready to proceed with the test [<CR>]:

<The parity lines test patern is now being output to the loopback connector>

Press RETURN to advance to the next pattern or to exit the test:

<The parity lines test pattern is not being

output to the loopback connector>

Press RETURN to advance to the next pattern or to exit the test:

Figure 3-7 Parity Lines Test

Appendix A shows the LED data patterns. Patterns alternate, so that you can tell if a signal is bad by looking at the patterns. If an error occurs prior to the LED panel test, a message similar to the one in Figure 3-8 is output to the user and the test ends.

```

DS> sta

.. Program: EVDR# - DRB32-M, -E Functional Diagnostic, revision 1.1,

16 fests, at 00:30:33.28.

Test 16: DRB32 External Loopback Test Routine

WARNING:

Make sure the loopback connector, cables, etc. are connected

properly, failure to do so could result in damage to user

equipment.

Type ''GO'' when you are ready to proceed with the test [GD] go

****** EVDRH - DRB32-M, -E Functional Diagnostic - 1.1 *******

Pass 1, test 1, subtest 0, error 3, 8-MAR-1990 03:48:48:81

Hard error while testing UQ1: DRB32 ERROR

B! TO IDDAT REGISTER TRANSFER ERROR.

EXPECTED VALUE OF IDDAT: FFFFFFFF(X)

RECEIVED VALUE OF IDDAT: GOEFEFGF(X)

******* End of Hard error number 3 ******

```

Figure 3-8 Error on Testing

# 3.4 EVDRI (VAX Level 3)

EVDRI is also a VAX level 3 diagnostic that runs under the control of the V/X Diagnostic Supervisor (VDS). This diagnostic tests the functionality and data path of the DRB32-W converter module. The DRB32-W is a device that interfaces the DRB32 (a VAXBI device) to the DR11-W (a UNIBUS device).

Like EVDRH, EVDRI comprises two distinct program sections: an internal loopback section and an external loopback section. The external loopback test requires the use of an external loopback cable (part no. 70-23923), but unlike the connector for EVDRH there are no LEDs associated with it. The two program sections contain identical tests, but the external loopback test provides maximum hardware coverage. EVDRI includes the following tests.

| Test<br>Number | Name                                                           | Function                                                                                                     |

|----------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 1              | DRB32-W Internal<br>Loopback Longword<br>DMA Test              | Tests the ability of the DRB32-W to transfer longwords via DMA transactions                                  |

| 2              | DRB32-W Internal<br>Loopback Byte DMA<br>Test                  | Tests the ability of the DRB32-W to transfer bytes via DMA transactions                                      |

| 3              | DRB32-W Internal<br>Loopback ATTN H<br>Interrupt Test          | Tests the ability of the DRB32-W to respond to and clear an ATTN H interrupt                                 |

| 4              | DRB32-W Internal<br>Loopback Direction<br>Error Interrupt Test | Tests the ability of the DRB32-W to respond to a direction error interrupt and clear the error condition     |

| 5              | DRB32-W Internal<br>Loopback DATAIP<br>Error Interrupt Test    | Tests the ability of the DRB32-W to respond to a Data In Pause error interrupt and clear the error condition |

| 6              | DRB32-W External<br>Loopback Longword<br>DMA Test              | Tests the ability of the DRB32-W to transfer longwords via DMA transactions                                  |

| 7              | DRB32-W External<br>Loopback Byte DMA<br>Test                  | Tests the ability of the DRB32-W to transfer bytes via DMA transactions                                      |

| 8              | DRB32-W External<br>Loopback EVEN Word<br>Transfer Test        | Tests the reliability of the DRB32-W word counter functionality during EVEN word transfers                   |

| 9              | DRB32-W External<br>Loopback ODD Word<br>Transfer Test         | Tests reliability of the DRB32-W word counter functionality during ODD word transfers                        |

| 10             | DRB32-W External<br>Loopback ATTN H<br>Interrupt Test          | Tests the ability of the DRB32-W to respond to and clear ATTN H interrupt                                    |

| 11             | PRB32-W External Loopback Direction Error Interrupt Test       | Tests the ability of the DRB32-W to respond to a direction error interrupt and clear the error condition     |

| 12             | DRB32-W External<br>Loopback DATAIP<br>Error Interrupt Test    | Tests the ability of the DRB32-W to respond to a Data In Pause error interrupt and clear the error condition |

| Table 3-4 | EVDRI Tests | (Continued) |

|-----------|-------------|-------------|

|-----------|-------------|-------------|

| Test<br>Number | Name                                            | Function                                                                     |

|----------------|-------------------------------------------------|------------------------------------------------------------------------------|

| 13             | DRB32-W Single-<br>System LINK Test<br>T1023-YA | Tests the ability of two DRB32-Ws (T1023-YA) to pass messages in PIO and DMA |

| 14             | DRB32-W Single-<br>System LINK Test<br>T1023-00 | Tests the ability of two DRB32-Ws (T1023-00) to pass messages in PIO and DMA |

EVDRI has two sections and section names. These section names (and the tests that each section performs) are shown in Table 3-5.

**Table 3-5 EVDRI Sections**

| Section Names              | Tests Performed                                         |

|----------------------------|---------------------------------------------------------|

| 1) DEFAULT                 | (All DRB32-W internal loopback tests) Tests 1-5         |

| 2) DRBW_EXTERNAL           | Runs DRB32-W external loopback tests<br>Tests 6-12      |

| 3) DRBW_SINGLE_SYSTEM_LINK | Runs DRB32-W single-system LINK test<br>Tests 13 and 14 |

#### NOTE

T1023-YA is a new version of the DRB32-W. The T1023-00 is the old (T1023-AA) version. Only the new version is shipped, but these diagnostics will test any old version (T1023-00) module previously installed in the system.

## 3.4.1 Running EVDRI

Before diagnosing the DRB32-W using EVDRI, be sure the DRB32-M module is fully functional. Only after the DRB32-M is known to be good should diagnosing of the DRB32-W take place. This will help prevent erroneous testing results. To run the default section (internal loopback tests) of EVDRI, first make sure the DRB32-W and the DRB32-M are attached by the appropriate cables. Boot the VAX Diagnostic Supervisor, load EVDRI, and follow the attach sequence (section 3.3.1) for the DRB32-M module. The DRB32-W does not contain a VAXBI corner and, therefore, does not need to be attached to the supervisor process. Type STA and the DRB32-W internal loopback tests are then run and appear as shown in Figure 3-9.

Copyright Digital Equipment Corporation 1986, 1987, 1988, 1989, 1990. All Rights Reserved.

DIAGNOSTIC SUPERVISOR, ZZ-EBSAA-X12.6-1996 8-MAR-1990 03:43:20

DS> load evdri

Copyright Digital Equipment Corporation 1986, 1987, 1988, 1989, 1990.

All Rights Reserved.

CONFIDENTIAL DIAGNOSTIC SOFTWARE PROPERTY OF DIGITAL EQUIPMENT CORPORATION

Use authorized only pursuant to a valid Right-to-Use License.

••••••••••••••

```

DS> att

Device type? drb32

Device Link? hub

Device Name? ug1

Node? 6

BR? 4

DS> set tra,h

DS> sel all

DS> sta

.. Program: EVDRI - DRB32-W Functional Diagnostic, revision 3.0, 14

tests, at 03:44:13.99.

Testing: UG1

Test 1: DRB-W Internal Loopback Longword DMA Test

Test 2: DRB-W Internal Loopback Byte DMA Test

Test 3: DRB-W Internal Loopback ATTNH Interrupt Test

Test 4: DRB-W Internal Loopback Direction Error Interrupt Test

Test 5: DRB-W DATAIP Error Test

.. End of run, 0 errors detected, pass count is 1,

time is 8-MAR-1990 03:48:48.40

```

Figure 3-9 DRB32-W Internal Loopback Test Example

If an error occurs during testing, an error message (similar to the one in Figure 3-10) is output to the user.

```

Pass 1, test 1, subtest 0, error 10, 8-MAR-1990 03:48:48.40

Hard error while testing UQ1: DRB32 ERROR

A DMA READ DOES NOT MATCH THE DATA WRITTEN TO THE DRB-W

EXPECTED: 00000000

RECEIVED: 00400040

******* End of Hard error number 10 *******

```

Figure 3-10 DRB32-W Test Error

### 3.4.2 DRB32-W Loopback Cable

For complete coverage of the DRB32-W, it is necessary to disconnect the DRB32-W from the user equipment and connect it to a loopback cable (part no. BC051-1C). To use the DRB32-W loopback cable, you must set a switch on the bulkhead connector to the low position to change the polarity of the BUSY H signal.

### NOTE

If the switch is not set properly, the diagnostic reminds the user; see Figure 3-11.

The BUSY bit on the DRBW connector is not set. Please set the switch on the external loopback connector before continuing.

Figure 3-11 Improperty Set Switch Message

An illustration of the DRB32-W loopback cable is shown in Figure 3-12.

Figure 3-12 DRB32-W Loopback Cable

The external loopback test is run by calling out the specific section in the diagnostic. This is illustrated in Figure 3-13.

```

DS> sta/sec=drbw_external

.. Program: EVDRI- DRB32-W Functional Diagnostic, revision 3.0, 14 tests, at 03:44:13.99.

Testing: _UQ1

Test 6: DRB-W External Loopback Longword DMA Test

Test 7: DRB-W External Loopback Byte DMA Test

Test 8: DRB32-W External Loopback EVEN Word Transfer Test

Test 9: DRB32-W External Loopback DDD Word Transfer Test

Test 10: DRB32-W External Loopback ATTN H Interrupt Test

Test 11: DRB32-W External Loopback Direction Error Interrupt Test

Test 12: DRB32-W External Loopback DATAIP Error Interrupt Test

.. End of run, 0 errors detected, pass count is 1,

time is 8-MAR-1990 03:48:51.40

```

Figure 3-13 External Loopback Test Example

If an error occurs, a message to that effect is output to the user. For an example of a sample error message you might expect to see, refer to the error message example under running the DRB32-W internal loopback tests, Figure 3-10.

## 3.5 Troubleshooting

Follow general systemwide techniques for troubleshooting with this option. Some suggestions are:

- Self-test and module swap works in most cases

- Seating in the VAXBI backplane is important

- Torque settings on transition headers are critical; use 6 inch pounds—greater torque causes damage to the transition header and backplane

- Always use a grounded wrist strap to prevent static damage to the modules

## 3.5.1 Diagnosing the DRB32-M

The DRB32 has two Field Replaceable Units:

- 1. The T1022 module

- 2. The cables between the VAXBI backplane and the user device.

Self-test and EVDRH default sections test the DRB32-M module logic up to the bus drivers. If both these test pass, but the customer is not able to use the option, either the drivers or the cable is faulty. Use the DRB32 output tester to isolate the failure to either the cables or the DRB32 drivers.

If customer failures persist, and efforts to correct hardware problems do not work, there may be a problem with customer-produced hardware or software.

### 3.5.2 Diagnosing the DRB32-E

The DRB32-E consists of:

- 1 The DRB32-M (T1022) m saule

- 2. The DRB32-E (T1024) module

- Sets of cables.

Between the two modules on the VAXBI backpiane

From the VAXBI backplane to the I/O connector panel

From the I/O connector panel to the user device

4. The I/O connector panel

There is no self-test on the T1024 module. Its LED is tied to +5 volts so that when this LED is lit, it does not indicate that self-test passed. The module is designed to compensate for differential grounds between systems/devices not in the same electrical environment as the DRB32. It is primarily made up of ECL logic and has a very high MTBF. To troubleshoot this option, you must use EVDRH with the DRB32 output tester to isolate the failing part.

## 3.5.3 Diagnosing the DRB32-W

The DRB32-W consists of:

- 1. The DRB32-M (T1022) module

- 2. The DRB32-W (T1023) module

- 3. Sets of cables

Between the two modules on the VAXBI backplane

From the VAXBI backplane to the bulkhead connector

From the bulkhead connector to the user device

4. The bulkhead connector

There is no self-test on the T1023 module. Its LED is tied to +5 volts so that when this LED is lit, it does not indicate that it passed self-test. This module is designed to provide interface capabilities from the DRB32 to a DR11-W device.

To troubleshoot this option, you must use EVDRI in Internal Loopback mode and External Loopback mode with the loopback cable. Ensure that the DRB32-M module has been thoroughly verified to be working so as to eliminate this from the diagnostic path. The quickes method of diagnosing the DRB32-W converter module is to run the Internal Loopback mode tests. If any of these tests fails, the module or the cables connecting the DRB32-M to the DRB32-W converter module are faulty. Replace the cables and run the tests again. If the tests fail this time, the DRB32-W converter module is at fault.

If these tests pass, you should run the external loopback tests. If any one of these tests fails, the DRB32-W module or the cables to the bulkhead connector are bad. To isolate the problem, use known good cables from the DRB32-W converter module to the bulkhead connector. If the tests now fail, the DRB32-W is faulty. Conversely, if the tests pass, replace the cables.

## 3.6 Message Passing Between DRB32s (LINK Tests)

The purpose of the DRB32 link tests is to test the cable interconnect between two VAXBI systems containing DRB32 hardware. The diagnostic coverage is minimal, though the link test does exploit a great deal of the transfer capabilities of the DRB32. For this reason, the LINK test should not be run if the DRB32 internal/external tests have not previously run successfully. Only after the other tests have verified the functionality of the connected DRB32s are the results of the LINK test meaningful.

There are two versions of the LINK test:

- Single-system LINK test

- Dual-system LINK test

The single-system LINK test is used to test two DRB32s that are in the same system. This test is especially useful for manufacturing testing. The dual-system LINK test is used to test two DRB32s devices in different systems.

## 3.6.1 Running the EVDRH Single-System LINK Test

Use the EVDRH single-system LINK test (or intrasystem LINK test) to functionally test two DRB32s in the same VAXBI system. The LINK test is only meaningful after self-test and all level 3 internal/external loopback tests have been run successfully.

The EVDRH single-system LINK test actually consists of two subtests:

- The first test verifies that the cables are connected properly by writing and reading the DRB32's IOCTL and IODAT registers.

- The second test exchanges protocol and data between the two DRB32s in a manner similar to an actual application. The total data transfer is variable, up to approximately 1MB of data.

To run the EVDRH single-system LINK test, follow these instructions:

- Place two DRB32s as close to each other as possible in the same VAXBI backplane (be careful to note at which nodes they reside). Using any available internal cables (see Table 2-2: Cable Ordering Numbers) or the intermodule cable (17-01474-01) from the output tester, connect the DRB32s together as explained in section 2.2.2 for the T1022 and T1024 modules.

- Boot the supervisor and ATTACH the DRB32s.

- Set trace and select the units to test.

- Set event flag 1 to attach two UUTs for simultaneous testing.

- Run the first test.

See Figure 3-14 for an example of running the single-system LINK test (first test).

Copyright Digital Equipment Corporation 1986, 1987, 1988, 1989, 1990. All Rights Reserved.

DIAGNOSTIC SUPERVISOR, ZZ-EBSAA-X12.6-1996 8-MAR-1990 03:43:20 DS> 1 evdrh

Copyright Digital Equipment Corporation 1986, 1987, 1988, 1989, 1990. All Rights Reserved.

CONFIDENTIAL DIAGNOSTIC SOFTWARE PROPERTY OF DIGITAL EQUIPMENT CORPORATION

Use authorized only pursuant to a valid Right-to Use License.

DS> att

Device type? drb32

Device Link? hub

Device Name? uq1

Node? 6

BR? 4

DS> att

Device type? drb32

Device Link? hub

Device Name? uq2

Node? 7

BR? 4

DS> set tra

DS> set ev fl1

## Figure 3-14 Running EVDRH Single-System LINK Test

If the cables are connected properly and the DRB32 drivers are fully functional, the output appears as in Figure 3-15.

Test 1: Link Modules IOCTL/IODAT Test

... End of run, 0 errors detected, pass count is 1.

Figure 3-15 Running Single-System LINK Test: Test 1

If an error occurs, a typical run might look like the one shown in Figure 3-16.

```

DS>

```

```

.. Program: EVDRH - DRB32-M, -E Functional Diagnostic, revision 1.1, 16 tests, at 03:48:50.40.

Testing: _UQ1 _UQ2

```

```

Test 14: Link Modules IOCTL/IODAT Test

****** EVDRH - DRB32-M, -E functional Diagnostic - 1.1 *******

Pass 1, test 14, subtest 0, error 1, 0-MAR-1990 03:48:48.40

Hard error while testing UQ1: DRB32 ERROR

```

ERROR TRANSFERRING DATA FROM ''ORIGINAL MASTER'' IOCTL TO ''ORIGINAL SLAVE'' IOCTL.

```

EXPECTED:

00, 01, 02, 03, 04, 05, 06, 07, 08, 09, 0A, 0B, 0C, 0D, 0E, 0F

10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 1A, 1B, 1C, 1D, 1E, 1F

20. 21. 22. 23. 24. 25. 26. 27. 28. 29. 2A. 2B. 2C. 2D. 2E. 2F

30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 3A, 3B, 3C, 3D, 3E, 3F

40. 41. 42. 43. 44. 45. 46. 47. 48. 49. 4A. 4B. 4C. 4D. 4E. 4F

50, 51, 52, 53, 54, 55, 56, 57, 58, 59, 5A, 5B, 5C, 5D, 5E, 5F

60, 61, 62, 63, 64, 65, 66, 67, 68, 69, 6A, 6B, 6C, 6D, 6E, 6F

70, 71, 72, 73, 74, 75, 76, 77, 78, 79, 7A, 7B, 7C, 7D, 7E, 7F

80, 81, 82, 83, 84, 85, 86, 87, 88, 89, 8A, 8B, 8C, 8D, 8E, 8F

90, 91, 92, 93, 94, 95, 96, 97, 98, 99, 9A, 9B, 9C, 9D, 9E, 9F

AO. A1. A2. A3. A4. A5. A6. A7. 48. A9. AA. AB. AC. AD. AE. AF

BO. B1. B2. B3. B4. B5. B6. B7. B8. B9. BA. BB. BC. BD. BE. BF

CO. C1. C2. C3. C4. C5. C6. C7. C8. C9. CA. CB. CC. CD. CE. CF.

DO, D1, D2, D3, D4, D5, D6, D7, D8, D9, DA, DB, DC, DD, DE, DF

EO. E1. E2. E3. E4. E5. E6. E7. E8. E9. EA. EB. EC. ED. EE. EF

FO, F1, F2, F3, F4, F5, F6, F7, D8, D9, FA, FB, FC, FD, FE, FF

```

Figure 3-16 Single-System LINK Test: Test 1 Error Example (Part 1 of 2)

```

RECEIVED:

End of Hard error number 1 *******

```

Figure 3-16 Single-System LINK Test: Test 1 Error Example (Part 2 of 2)

If an error occurs, check to make sure the cables are connected properly. If the connection is good, the cables may be faulty. After Test 1 successfully runs to completion, run Test 2. (See Figure 3-17.)

```

DS> ste/sec=single_cab_link

.. Program: EVDRH - DRB32-M, -E Functional Diagnostic, revision 1.1,

16 tests, at 05:48:48.50

Testing: _UG1 _UG2

Test 14: Link Modules IOCTL/IODAT Test

Test 15: DRB32 single-system Link Test

BEGINNING INITIAL DATA TRANSFER (1000 PAGES), [ORIGINAL MASTER (UQ10)

-> ORIGINAL SLAVE (UQ2)].

THE LINK HAS BEEN TURNED AROUND. WE WILL BEGIN TRANSFERRING DATA IN

THE OPPOSITE DIRECTION.

[ORIGINAL SLAVE (UQ2) -> ORIGINAL MASTER (UQ1)]

PROGRESS_FLAG = 000A

.. End of run, 0 errors detected, pass count is 1,

time is 8-MAR-1990 05:48:48.40

DS>

```

Figure 3-17 Single-System LINK Test: Test 2 Example

Note that the link is established and executed in two different directions. If an error occurs, the run may look like the one shown in Figure 3-18.

```

******* EVDRH - DRB32-M, -E Functional Diagnostic - 1.1 *******