**DRB32 Technical Manual**

digital equipment corporation @ maynard, massachusetts

The DRB32 is a high-speed parallel port sold by Digital Equipment Corporation for use in qualified applications. A brief special agreement is required for purchase of the product. Contact your Digital sales representative for more information.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

Book production by Educational Services Media Communications Group.

Copyright © 1989, 1990 by Digital Equipment Corporation. All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEC PDP VA X cluster

DECnet ULTRIX VMS

DECUS UNIBUS

DRB32 VAX

DR11-W VAXBI

# **CONTENTS**

# **PREFACE**

| CHAPTER 1 | INTRODUCTION                                       |      |

|-----------|----------------------------------------------------|------|

| 1.1       | PRODUCT DESCRIPTION                                | 1-1  |

| 1.2       | DRB32 HARDWARE COMPONENTS.                         | 1-2  |

| 1.3       | DRB32 OPTIONS                                      | 1-3  |

| 1.3.1     | DRB32 Main Option (DRB32-M)                        | 1-3  |

| 1.3.2     | DRB32 External Option (DRB32-E)                    | 1-5  |

| 1.3.3     | DRB32/DR11W Option (DRB32-W)                       | 1-6  |

| 1.4       | SOFTWARE                                           | 1-7  |

| 1.5       | DRB32 CONFIGURATIONS                               | 1-8  |

| 1.6       | STRATEGIES FOR CONNECTING TO THE VAXBI             | 1-8  |

| 1.7       | TYPICAL VAXBI/DRB32 SYSTEM CONFIGURATION           | 1-9  |

| CHAPTER 2 | FUNCTIONAL DESCRIPTION                             |      |

| 2.1       | BLOCK-DIAGRAM DESCRIPTION OF THE DRB32 MODULE      | 2-1  |

| 2.1.1     | Parallel I/O Port                                  | 2-3  |

| 2.1.1.1   | Features of the 32-Bit Parallel I/O Port Data Path | 2-3  |

| 2.1.1.2   | Features of the Two 8-Bit Control Paths            | 2-4  |

| 2.1.1.3   | Parity                                             | 2.4  |

| 2.1.1.4   | Central Bus RAM                                    | 2-4  |

| 2.1.2     | T-11 Microprocessor Subsystem                      | 2-4  |

| 2.1.3     | VAXBI Interface                                    | 2-5  |

| 2.2       | VAXBI TRANSACTIONS                                 | 2-6  |

| 2,2.1     | DRB32 Master VAXBI Transactions                    | 2-6  |

| 2.2.1.1   | READ                                               | 2-6  |

| 2.2.1.2   | WRITE                                              | 2-6  |

| 2.2.1.3   | Masked Octaword Write (WMCI)                       | 2-6  |

| 2.2.1.4   | Interrupt (INTR)                                   | 2-6  |

| 2.2.2     | DRB32 Slave Response to VAXBI Commands             |      |

| 2.2.2.1   | READ-Type Transactions                             |      |

| 2.2.2.2   | WRITE-Type Transactions                            | 2-8  |

| 2.2.2.3   | IDENT (Identify)                                   | 2-8  |

| 2.2.2.4   | STOP                                               |      |

| 2.3       | DRB32 ADDRESS SPACE                                |      |

| 2.3.1     | VAXBI Address Space Description                    | 2-9  |

| 2.3.2     | DRB32 Address Space Description                    | _    |

| 2.3.3     | DRB32 Address Space as Seen by the VAXBI           | 2-11 |

| 2.4       | DRB32 POWER-UP SEQUENCE                            | 2-12 |

| CHAPTER 3 | DRB32 REGISTER DESCRIPTIONS                        |      |

| 3.1       | BIIC REGISTERS                                     | 3-1  |

| 3.1.1     | DTYPEDevice Register                               | 3-2  |

| 3.1.2     | BICSR—VAXBI Control and Status Register            | 3-2  |

| 3.1.3     | BER—Bus Error Register                             | 3-4  |

| 3.1.4     | EINTRCSR—Error Interrupt Control Register                        |      |

|-----------|------------------------------------------------------------------|------|

| 3.1.5     | INTRDES—Interrupt Destination Register                           | 3-7  |

| 3.1.6     | IPINTRMSK Interprocessor Interrupt Mask Register                 | 3-7  |

| 3.1.7     | FIPSDES—Force Interproce sor Interrupt/Stop Destination Register | 3-7  |

| 3.1.8     | IPINTRSRCInterprocessor Source Register                          | 3-8  |

| 3 1.9     | SADR—Starting Address Register                                   | 3-8  |

| 3.1.10    | EADR—Ending Address Register                                     | 3-8  |

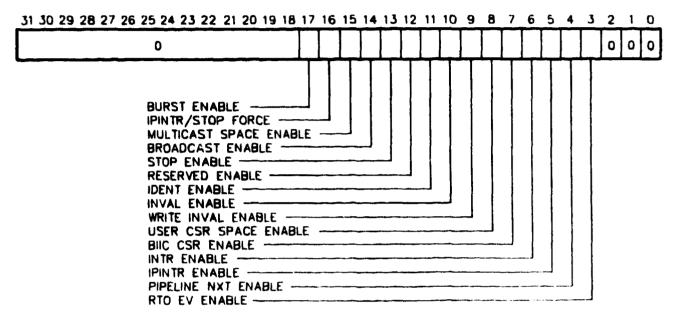

| 3.1.11    | BCICSR—BCI Control Register                                      | 3-9  |

| 3.1.12    | WSTAT—Write Status Register                                      |      |

| 3.1.13    | FIPSFR—Force Interprocessor Interrupt/Stop Register              | 3-11 |

| 3.1.14    | UINTRCSR—User Interface Interrupt Control Register               | 3-11 |

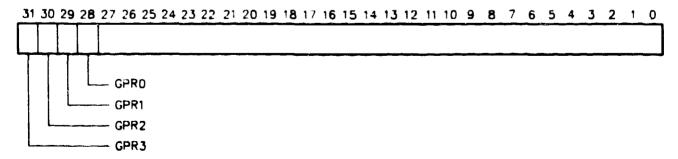

| 3.1.15    | BIIC General Purpose Registers                                   |      |

| 3.2       | DRB32 MODULE REGISTERS                                           |      |

| 3.2.1     | Parallel I/O Port Registers                                      |      |

| 3.2.2     | BAR—BCAI Access Register                                         | 3-14 |

| 3.2.3     | PARCSR—Parallel Port Control and Status Register                 | 3-15 |

| 3.2.4     | PARSTR—Parallel Port Setup and Test Register                     |      |

| 3.2.5     | ERRREG—Error Register                                            | 3-18 |

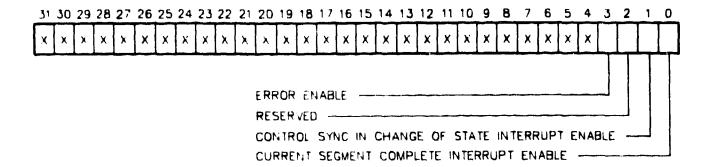

|           | DRBIEDRB32 Interrupt Enable Register                             | 3-20 |

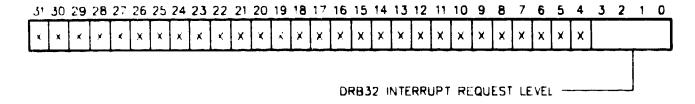

| 3.2.6     | DRBIRL—DRB32 Interrupt Request Level Register                    | 3-21 |

| 3.2.7     | DRDIED DRD32 Interrupt Clas Desister                             | 3.21 |

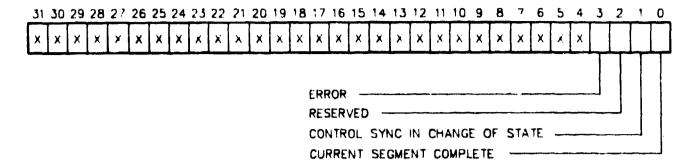

| 3.2.8     | DRBIFR—DRB32 Interrupt Flag Register                             | 3 22 |

| 3.2.9     | CURMR—Current Map Pointer Register                               | 3-22 |

| 3.2.10    | CURTOMR—Current Top of Map Register Area Pointer                 | 2.22 |

| 3.2.11    | CURBOFF—Current Address Byte Offset Register                     | 2.24 |

| 3.2.12    | CURBLET—Current Number of Bytes Left in Segment                  | 3-24 |

| 3.2.13    | PHYSADDR—Physical Address Register                               | 3-24 |

| 3.2.14    | IODAT—I/O Data Register                                          | 3-73 |

| 3.2.15    | IOCTL—I/O Control Register                                       | 3-20 |

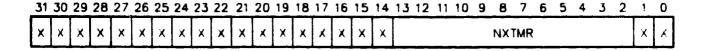

| 3.2.16    | NXTMR—Next Map Register Pointer                                  | 3-26 |

| 3.2.17    | NXTTOMR—Next Top of Map Register Area Pointer                    | 3-20 |

| 3.2.18    | NXTBOFF—Next Address Byte Offset                                 | 3-27 |

| 3.2.19    | NXTBLFT—Next Number of Bytes Left in Segment                     | 3-27 |

| 3.2.20    | TIIICR                                                           | 3-28 |

| 3.2.21    | T11MDTR                                                          | 3-28 |

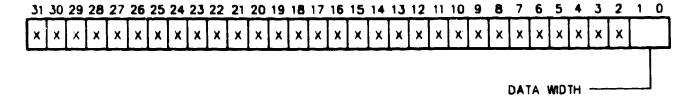

| 3.2.22    | DPWR—Data Port Width Register                                    | 3-28 |

| 3.2.23    | BOBP                                                             | 3-29 |

| 3.3       | VAX CONSOLE REGISTER (RXCD)                                      | 3-29 |

| 3.4       | USER-DEFINABLE REGISTERS (CB RAM)                                | 3-30 |

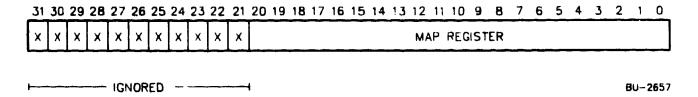

| 3.4.1     | Map Register                                                     | 3-30 |

| CHAPTER 4 | USER INTERFACE SIGNALS AND PROTOCOL                              |      |

| CHAILL 4  |                                                                  |      |

| 4.1       | USER INTERFACE DESCRIPTION                                       | 4-1  |

| 4.2       | USER INTERFACE DATA PATH DESCRIPTION                             | 4-3  |

| 4.2.1     | User Interface Data Path Data Signals                            | 4-3  |

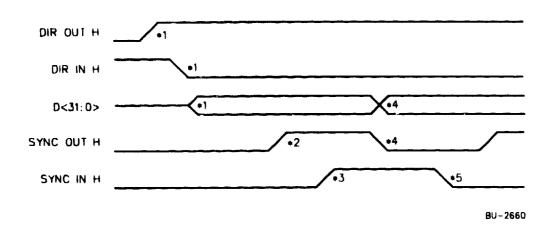

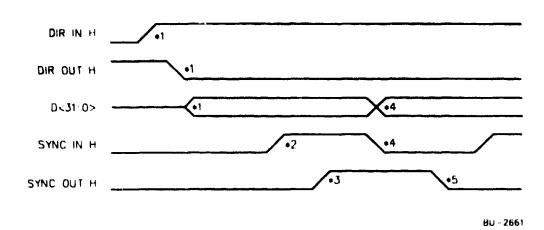

| 4.2.2     | Data Path Control Signals                                        | 4-4  |

| 4.2.2.1   | DIR IN/OUT                                                       | 4-4  |

| 4.2.2.2   | SYNC IN/OUT When Transmitting Data                               | 4-5  |

| 4.2.2.3   | SYNC IN/OUT When Receiving Data                                  | 4-5  |

| 4.2.3     | Data Transfer Protocol and Timing                                | 4-6  |

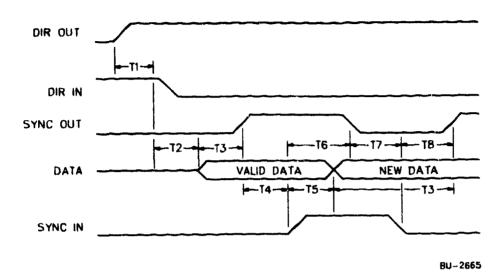

| 4.2.3.1   | Data Transfer from DRB32 to User Device                          | 4-7  |

| 4.2.3.2   | Send Data Timing                                                 |      |

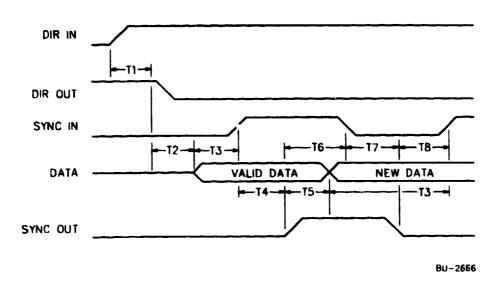

| 4.2.3.3   | Receive Data Timing                                              |      |

| 4.3       | USER INTERFACE CONTROL PATH DESCRIPTION                          |      |

| 4.3.1     | User Interface Control Path Data Signals                         | 4-10 |

| T.J.I     | OSCI INCLIACE CONTROL FAIR DATA DISHAM                           |      |

| 4.3.2          | User Interface Control Path Control Signals  |             |

|----------------|----------------------------------------------|-------------|

| 4.3.3          | Control Path Timing and Protocol             | 4-11        |

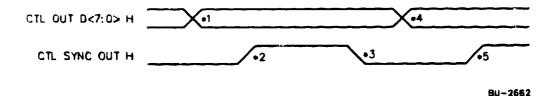

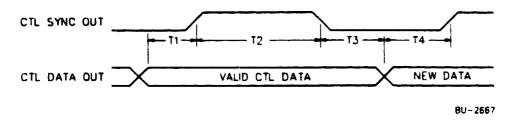

| 4.3.3.1        | CTL SYNC OUT H Timing                        | 4-11        |

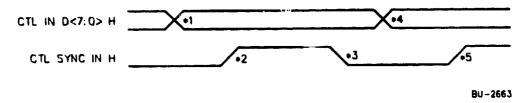

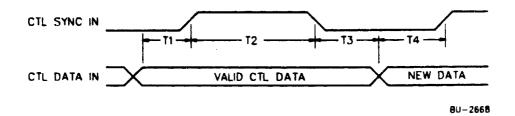

| 4.3.3.2        | CTL SYNC IN H Timing                         |             |

| 4.4            | DRB32 DEVICE STATUS LINES DESCRIPTION        | 4-12        |

| 4.4.1          | Device Status Signal Descriptions            |             |

| 4.5            | OPTIMIZING DATA TRANSFER SPEED               |             |

|                |                                              |             |

| 4.5.1          | DRB32 Data Transfer Speeds                   |             |

| 4.5.2          | How the DRB32 Works                          |             |

| 4.5.3          | The Synchronization Problem                  |             |

| 4.5.4          | DRB32 Data Transfer Speed with the VAX 8800  |             |

| 4.5.5          | DRB32 Speed Matrix                           | 4-19        |

| 4.5.6          | Rules to Optimize Data Transfer Speed        | 4-19        |

| APPENDIX A     | DRB32 SPECIFICATIONS                         |             |

| A.1            | TIMING SPECIFICATIONS                        | <b>A-1</b>  |

| A.1.1          | Send Data Timing                             | A-2         |

| A.1.2          | Receive Data Timing                          |             |

| A.1.3          | Control Data OUT Timing                      |             |

| A.1.3<br>A.1.4 | Control Data IN Timing.                      |             |

|                |                                              |             |

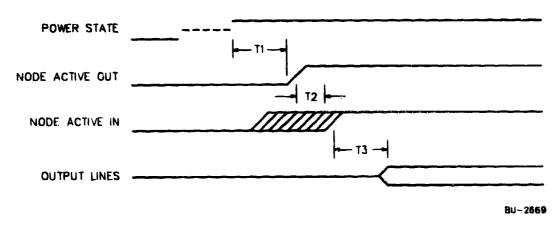

| A.1.5          | Power-Up Timing                              |             |

| Λ.2            | DRB32 ELECTRICAL SPECIFICATIONS              |             |

| A.2.1          | Intraenclosure DRB32-M Configuration         |             |

| A.2.1.1        |                                              |             |

| A.2.1.2        | Cables                                       | A-7         |

| A.2.1.3        | Terminators                                  | A-7         |

| A.2.2          | Interenclosure DRB32-E                       | A-7         |

| A.2.3          | Interenclosure DRB32-W                       |             |

| A.3            | ENVIRONMENTAL SPECIFICATIONS                 |             |

| A.4            | DRB32 PARALLEL I/O PORT PIN ASSIGNMENTS      |             |

| APPENDIX B     | DRB32-E OPTION                               |             |

|                |                                              |             |

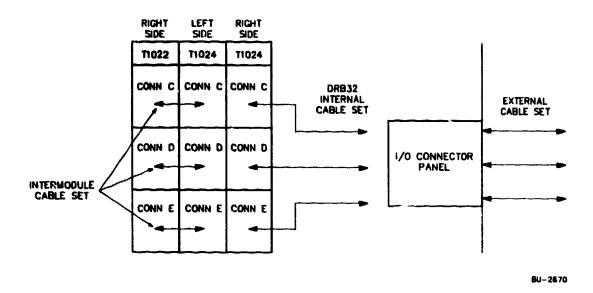

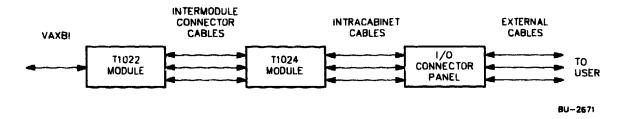

| B.1            | OVERVIEW                                     | B-1         |

| B.2            | I/O INTERCONNECTIONS BETWEEN CABINETS        | <b>B</b> -3 |

| B.2.1          | Differential Drivers (75110A)                |             |

| B.2.2          | Differential Receivers (75107)               | B-4         |

| B.2.3          | Single-Ended Bus Transceivers (26S10)        | B-4         |

| B.2.4          | Termination                                  | B-5         |

| B.3            | CABLE ASSEMBLIES                             | B-6         |

|                | LO INTERFACING DULES FOR THE DRIVE CORTION   |             |

| B.4            | I/O INTERFACING RULES FOR THE DRB32-E OPTION | D-0         |

| B.5            | PROPAGATION DELAY THROUGH THE T1024 MODULE   | B-6         |

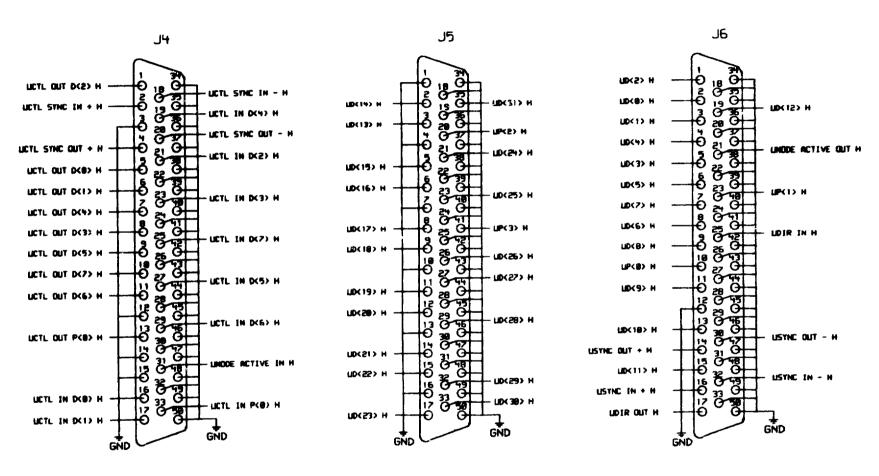

| <b>B</b> .6    | I/O SIGNAL-NAME INTERPRETATION               | B-8         |

| B.7            | POWER REQUIREMENTS                           | <b>B</b> -9 |

| APPENDIX C     | DRB32-W OPTION DESCRIPTION AND SPECIFICATION |             |

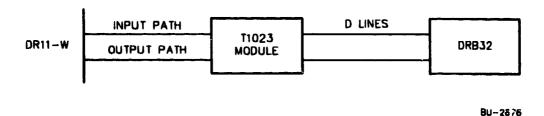

| C.1            | T1023 DESCRIPTION                            | C-1         |

| C.1.1          | DR11-W and DRB32-W Differences               |             |

| C.1.1<br>C.2   | BASIC FUNCTIONS OF THE T1023                 |             |

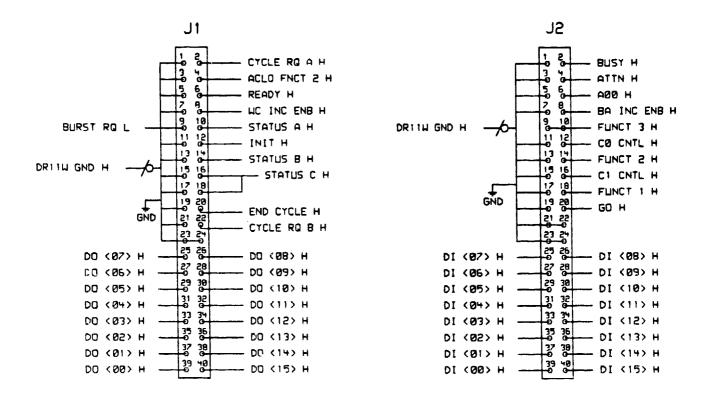

|                | DR11-W INTERFACE SIGNALS                     |             |

| C.3            |                                              |             |

| C.3.1          | Input Signals                                | C-4         |

| C.3.1.1        | Data Inputs                                  |             |

| C.3.1.2        | Status Inputs                                | C-4         |

| 2.3.1.3    | Bus Control                                                         |                |

|------------|---------------------------------------------------------------------|----------------|

| C.3.1.4    | Interrupt                                                           |                |

| C.3.2      | Output Signals                                                      |                |

| C.3.2.1    | Data Outputs                                                        |                |

| C.3.2.2    | Function Outputs                                                    |                |

| C.3.2.3    | Bus Control Outputs                                                 |                |

| C.3.2.4    | Miscellaneous Outputs                                               |                |

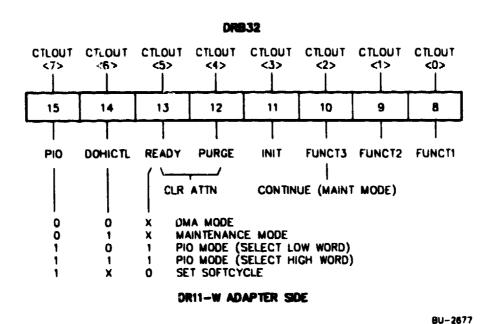

| C.4        | T1023 REGISTER SET                                                  | C-0            |

| C.4.1      | IOCTL - I/O Control Register                                        | C-0            |

| C.4.2      | IODAT - I/O Data Register                                           | C-9            |

| C.5        | DMA TRANSACTIONS AND TIMING DIAGRAMS                                | C 10           |

| C.5.1      | DRB32 WRITE to the DR11-W Interface                                 |                |

| C.5.2      | DRB32 READ of the DR11-W Interface                                  | C-10           |

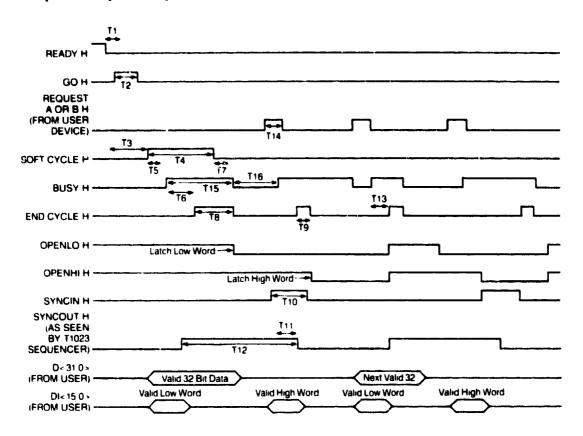

| C.5.3      | DMA Timing for a DRB32 WRITE to the DR11-W User Port                | C-11           |

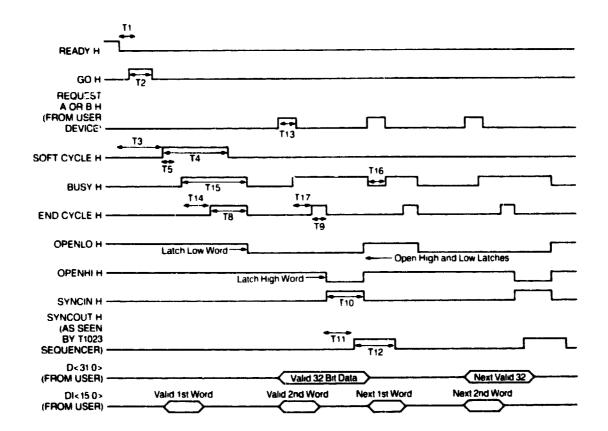

| C.5.4      | DMA Timing for a DRB32 READ of the DR11-W User Port                 | C-13           |

| C.6        | PROGRAMMED I/O MODE                                                 | C-14           |

| C.6.1      | Programmed I/O WRITEs to the DR11-W Port                            | C-14           |

| C.6.2      | Programmed I/O READs to the DR11-W Port                             | C-14           |

| C.7        | ELECTROMECHANICAL SPECIFICATIONS                                    |                |

| C.7.1      | Power Requirements                                                  | C-15           |

| C.7.2      | Environmental Requirements                                          | C-15           |

| C.7.3      | T1023 Electrical Specifications                                     | C-16           |

| C.7.3.1    | Cables                                                              | C-16           |

| C.7.3.2    | DR11-W Terminators                                                  |                |

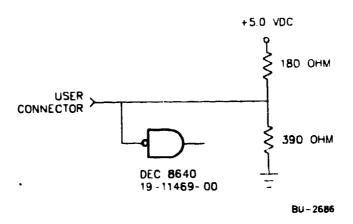

| C.7.3.3    | User Drivers and Receivers                                          | C-17           |

| C.8        | INTRODUCTION TO T1023-YA                                            | C-18           |

| C.9        | HARDWARE FEATURES OF THE T1023-YA                                   | C-18           |

| C.9.1      | Timing Considerations for READ and WRITE Transactions               | C-19           |

| C.10       | SOFTWARE                                                            | C-22           |

| C.10.1     | Driver Modifications to Allow Use of the Word Counter Functionality | C-22           |

| C.10.2     | Diagnostics                                                         | C-23           |

| C.11       | LIMITATIONS OF THE T1023-YA                                         | . C-24         |

| C.12       | IMPLEMENTATION OF T1023-YA FEATURES                                 | . C-24         |

| C.12.1     | Process                                                             | . C-25         |

| C.12.2     | READ Implementation                                                 | . C-25         |

| C.12.3     | LOAD Implementation                                                 | . C-26         |

| C.12.4     | New DRB32-W Counter Clock                                           | . C-26         |

| C.12.5     | T1023-YA Verification                                               | . C-27         |

| C.12.6     | Setting New Board Mode                                              | . C-27         |

| C.12.7     | Setting Old Board Mode                                              | . <b>C-2</b> 7 |

| C.13       | OTHER T1023-YA CONSIDERATIONS                                       | . C-28         |

| C.13.1     | Installation Instructions                                           | . C-28         |

| C.13.2     | Timing Information                                                  | . C-28         |

| C.13.3     | Specifications                                                      | . C-28         |

| C.13.4     | Diagnostics                                                         | . C-28         |

| APPENDIX D | USING THE BCAI ACCESS REGISTER (BAR)                                |                |

|            |                                                                     | _              |

| D.1        | WHAT THE DUAL-OCTAWORD REGISTER FILE LOOKS LIKE                     | . D-1          |

| D.2        | HOW THE DRB32-M USES THE DUAL-OCTAWORD REGISTER FILE                |                |

| D.3        | HOW TO GET THE DATA FROM THE BCAI                                   |                |

| APPENDIX E | GLOSSARY                                                            |                |

# **FIGURES**

| 1-1            | DRB32 Adapter (T1022)                                             |              |

|----------------|-------------------------------------------------------------------|--------------|

| 1-2            | DRB32 Simplified Block Diagram                                    |              |

| 1-3            | DRB32 Main Option (DRB32-M)                                       |              |

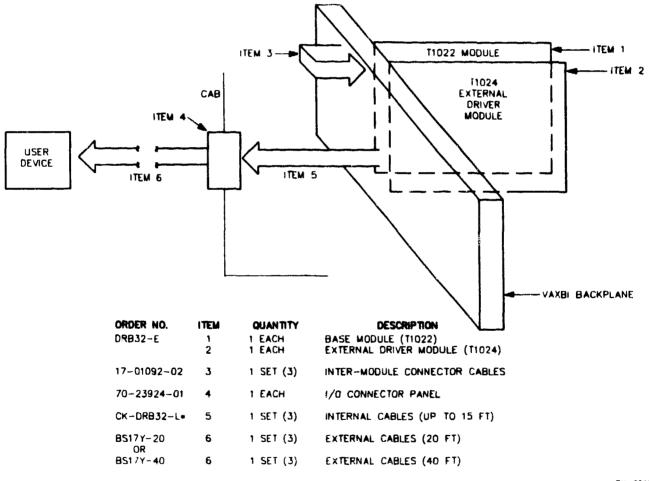

| 1-4            | DRB32 External Cable Driving Option (DRB32-E)                     |              |

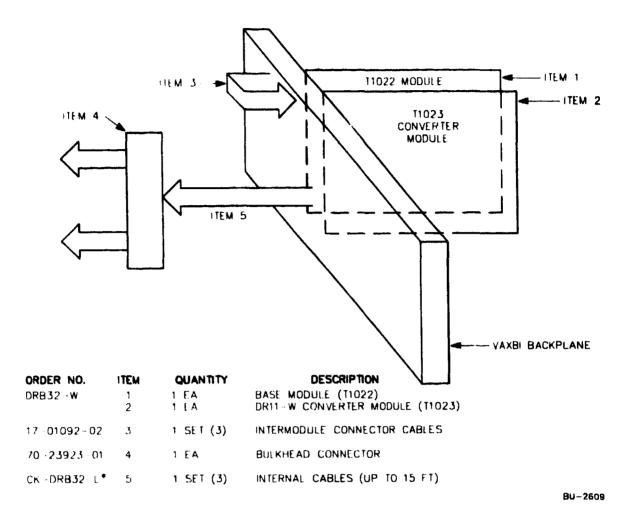

| 1-5            | DRB32-W Option                                                    | 1-7          |

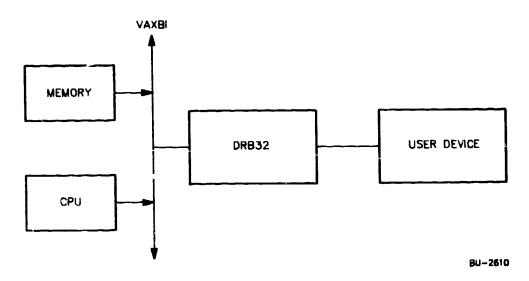

| 1-6            | Typical DRB32 System Configuration                                | 1-9          |

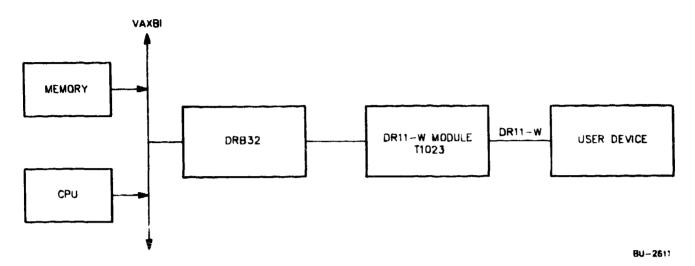

| 1-7            | Typical DRB32-W Configuration                                     |              |

| 1-8            | DRB32 System Configuration with Interface Module                  |              |

| 2-1            | DRB32 Block Diagram                                               |              |

| 2-2            | T-11 Subsystem                                                    |              |

| 2-3            | VAXBI Interface for the DRB32                                     | 2-5          |

| 2-4            | VAXBI I/O Address Space                                           |              |

| 2-5            | DRB32 Address Space                                               |              |

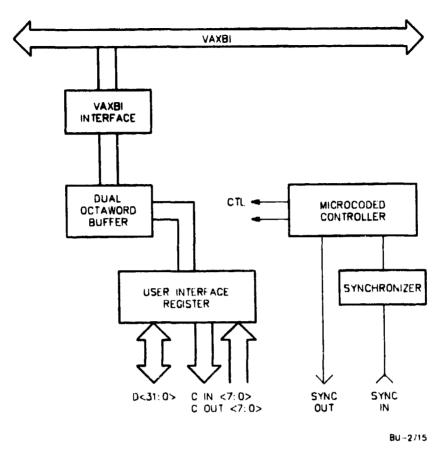

| 4-1            | DRB32 Data Path Block Diagram                                     | 4-2          |

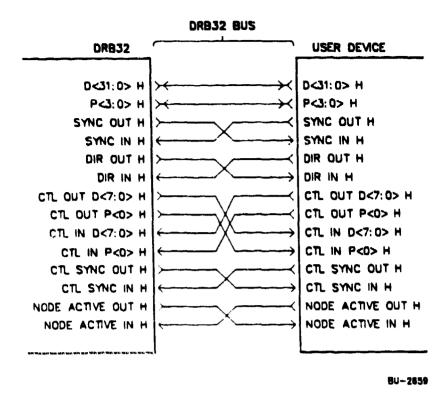

| 4-2            | DRB32 Signal Connections                                          | 4.3          |

| · <del>-</del> | Cold Data Timing Dispress                                         | A. Q         |

| 4-3            | Send Data Timing Diagram                                          | 4.0          |

| 4-4            | Receive Data Timing Diagram                                       |              |

| 4-5            | CTL SYNC OUT H Timing Diagram                                     |              |

| 4-6            | CTL SYNC IN H Timing Diagram                                      |              |

| 4-7            | DRB32 Data Path                                                   |              |

| A-1            | Send Data Timing Diagram                                          |              |

| A-2            | Receive Data Timing Diagram                                       |              |

| A-3            | Control Data OUT Timing                                           |              |

| A-4            | Control Data IN Timing                                            |              |

| A-5            | Power-Up Timing Diagram                                           | A-5          |

| A-6            | DRB32 Parallel Port Pin Assignments                               | A-9          |

| B-1            | DRB32-E Option Basic Cabinet                                      |              |

| B-2            | Typical DRB32-E Configuration                                     | B-1          |

| B-3            | DRB32-E Signal Pin Assignments                                    |              |

| B-4            | Propagation Delay Through the 74F240 and the 26S10                |              |

| B-5            | Delay for All Signals that are Driven Differentially              |              |

| B-6            | Delay for Signals that are Driven Through the 75110               | . <b>B-7</b> |

| B-7            | Signal Transfer Name Interpretation                               |              |

| C-1            | T1023 Module Connection to DRB32 and DR11-W                       |              |

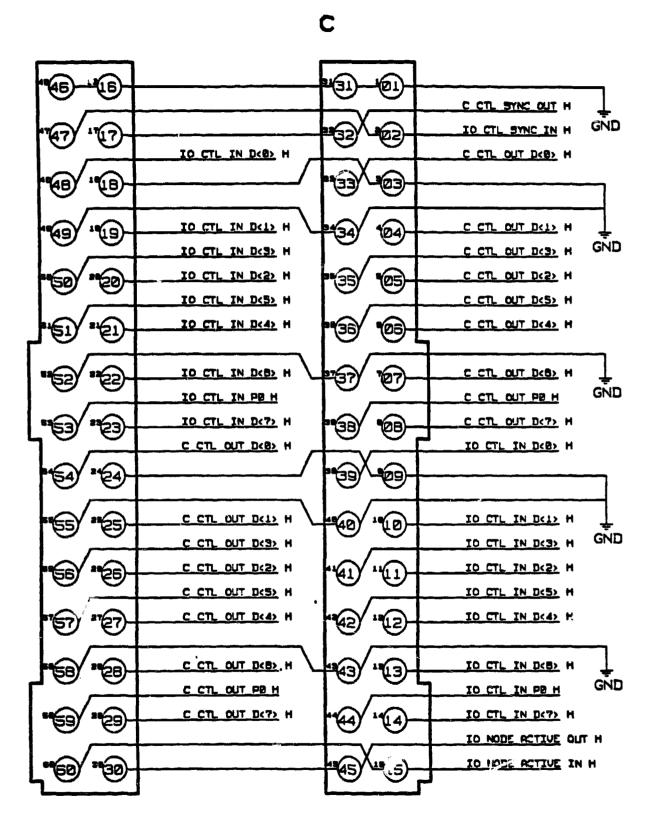

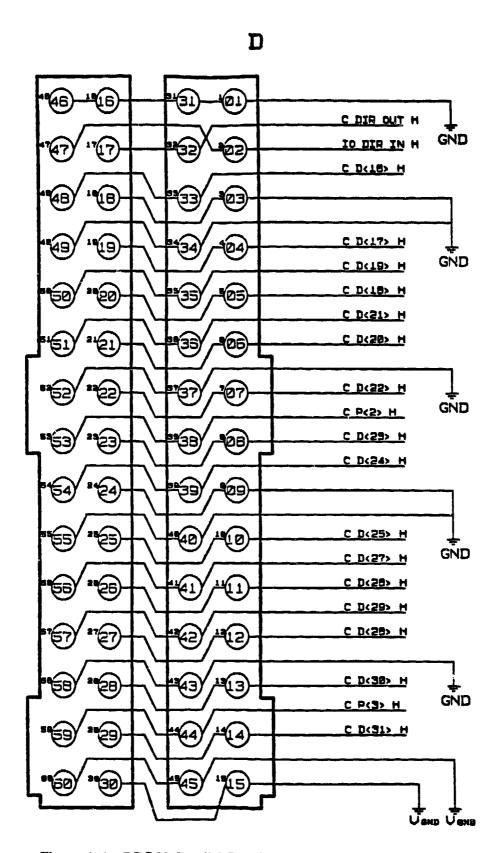

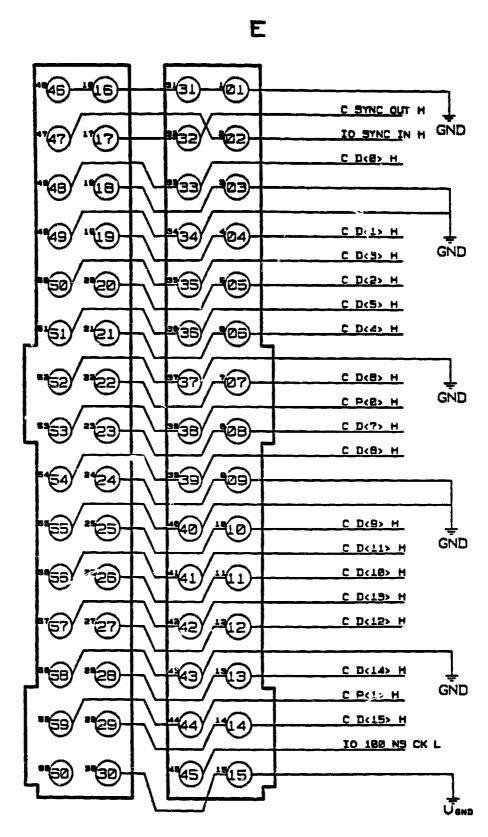

| C-2            | DRB32-W Signal Pin Assignments                                    |              |

| C-2<br>C-3     | I/O Control Register - Output Bytes                               |              |

| C-4            | I/O Control Register - Input Bytes                                |              |

| C-4<br>C-5     | T1023 I/O Data Register                                           | C-0          |

|                | Timing for DRB32 WRITE (Transfer from DRB32-W to User Device)     | C-11         |

| C-6            | Timing for DRB32 WKITE (Transfer from DRB32-W to User Device)     | $C_{12}$     |

| C-7            | Timing for DRB32 READ (Transfer from User Device to DRB32-W)      | C 17         |

| C-8            | User Driver Configuration                                         | . C-17       |

| C-9            | User Receiver Configuration                                       | . C-1/       |

| C-10           | Timing for DRB32-W WRITE (Transfer from DRB32-W to User Devi e)   | C 20         |

|                | Transfer Started by SOFT CYCLE                                    | . C-20       |

| C-11           | Timing for DRB32-W READ from User Device Transfer Started by SOFT |              |

|                | CYČLE                                                             | . C-21       |

# TABLES

| 1-1  | Data Transfer Rates                                               | . 1-6        |

|------|-------------------------------------------------------------------|--------------|

| 2-1  | Node Space Base Address Assignments                               |              |

| 3-1  | BIIC Registers                                                    | . 3-1        |

| 3-2  | DRB32 Arbitration Modes                                           | . 3-3        |

| 3-3  | Parallel I/O Port Registers                                       | . 3-13       |

| 3-4  | Direction of Data Transfer                                        | . 3-17       |

| 3-5  | ERRREG Error Codes                                                | . 3-19       |

| 3-6  | DRB32 Interrupt Levels                                            | . 3-21       |

| 3-7  | Data Transfer Widths                                              |              |

| 3-8  | VAX Console Register                                              | . 3-29       |

| 3-9  | User-Definable Registers                                          | . 3-30       |

| 4-1  | Data Path Data Signals                                            | . 4-4        |

| 4-2  | Direction of Data Transfer                                        | . 4-5        |

| 4-3  | Data Path Control Signals                                         | . 4-6        |

| 4-4  | Control Path Data Signals                                         | . 4-10       |

| 4-5  | Control Path Control Signals                                      |              |

| 4-6  | Device Status Signal Descriptions                                 | . 4-13       |

| 4-7  | DRB32 Speed Matrix                                                | . 4-19       |

| A-1  | Send Data Timing Description                                      | . A-2        |

| A-2  | Receive Data Timing Description                                   | . A-3        |

| A-3  | Control Data OUT Timing Description                               | <b>A-4</b>   |

| Λ-4  | Control Data IN Timing Description                                |              |

| A-5  | Power-Up Timing Description                                       |              |

| A-6  | DC Specifications for the Intraenclosure DRB32-M                  | <b>A-</b> 7  |

| A-7  | Propagation Time for Intraenclosure DRB32-M                       |              |

| Λ-8  | DRB32 Operating Environmental Specifications                      |              |

| A-9  | DRB32 Storage Environmental Specifications                        |              |

| B-1  | T1024 Power Requirements                                          |              |

| C-1  | Comparison of Adapter Transfer Rates                              |              |

| Č-2  | Miscellaneous Output Signals                                      |              |

| Č-3  | Error Status Bits                                                 |              |

| Č-4  | Timing for DRB32 WRITE (Transfer from DRB32-W to User Device)     | C-12         |

| C-5  | Timing for DRB32 READ (Transfer from User Device to DRB32-W)      | C-13         |

| C-6  | T1023 Power Requirements                                          | C-15         |

| C-7  | T1023 Operating Environment                                       | C-15         |

| C-8  | T1023 Storage Specifications                                      | <b>C-1</b> 6 |

| C-9  | 8881 Driver Output DC Specifications                              | C-!6         |

| C-10 | 8640 Receiver Input DC Specifications                             | C-16         |

| C-11 | Timing for DRB32-W WRITE (Transfer from DRB32-W to User Device)   | <del>-</del> |

| - 11 | Transfer Started by SOFT CYCLE)                                   | <b>C-2</b> 0 |

| C-12 | Timing for DRB32-W READ from User Device Transfer Started by SOFT |              |

| - 12 | CYCLE)                                                            | <b>C-</b> 21 |

| C-13 | Diagnostic Tests in FVDRI                                         | C-23         |

#### **PREFACE**

#### PURPOSE OF THIS MANUAL

The DRB32 Technical Manual (EK-DRB32-TM) describes the hardware components of the DRB32 adapter. This manual includes theory of operation, functional descriptions of components, VAXBI transactions for the DRB32, addressing and register descriptions, user interface signal descriptions, pin assignments, electrical and environmental specifications, and timing diagrams.

#### INTENDED AUDIENCE

this manual is for:

- Digital or customer personnel who install and repair this equipment in the field

- Customer engineers and programmers who incorporate this equipment into their own product or system.

The manual presumes familiarity with the VAXBI bus, VAX processors, and the VMS operating system.

#### STRUCTURE OF THIS MANUAL

Chapter 1 introduces the DRB32, describes its three subsystems, and illustrates typical DRB32 configurations.

Chapter 2 describes the theory of operation of the DRB32 adapter, including a block diagram of the basic module (T1022), functional descriptions and VAXBI transactions.

Chapter 3 describes the address space and registers of the DRB32, including BIIC registers and DRB32 module registers.

Chapter 4 describes the user interface signals and protocol of the DRB32 data path.

Appendix A includes electrical and environmental specifications, pin assignments, and timing diagrams.

Appendix B describes the DRB32-E module (T1024) for the DRB32-E option.

Appendix C describes both DRB32-W options: the T1023-00 and T1023-YA.

Appendix D describes the usage of the BCAI Access Register.

Appendix E is a glossary of DRB32-related terms used in this documentation set.

#### **RELATED MANUALS**

This is one of a family of processors, memories, and adapters that uses the 32-bit VAXBI bus. For a technical summary of all VAXBI modules, system components, and integrated circuits, see the VAXBI Options Handbook, EB-27271-46.

#### Preface

Other related technical manuals are:

DRB32 Introduction Order No. EK-DRB32-OV

DRB32 Programmer's Manual Order No. AA-HZ25C-TE

DRB32 Hardware Installation Guide Order No. EK-DRB32-IN

DR11-W User's Guide Order No. ED-DR11W-UG-003

For further information on VAX/VMS, see the VAX/VMS Documentation Set.

#### **CONVENTIONS USED**

In this manual, the following conventions are used:

- The DRB32 adapter is referred to as the DRB32.

- The VAXBI bus is referred to as the VAXBI.

# CHAPTER 1 INTRODUCTION

The DRB32 is a high-performance gateway to the VAXBI. The adapter provides a half-duplex asynchronous interface between Digital's VAXBI bus and user-designed devices such as signal processors, FFT machines, array processors, high-speed A/D converters, high-speed instrumentation, and other specialized devices.

#### 1.1 PRODUCT DESCRIPTION

The DRB32 is a VAXBI adapter that provides fast data transfers in longwords, words, or bytes, and connects external user devices to VAXBI systems. The DRB32 performs fast parallel I/O DMA transfers of up to 982,528 bytes. The hardware allows DMA transfers larger than 982,528 bytes with a double buffering capability. The DRB32 adapter can also be used in programmed I/O (data) mode, which requires a processor to intervene on each READ or WRITE cycle.

The DRB32 transfers data to the user device through a 32-bit data path and a pair of 8-bit control paths. Those user devices that do not accept the DRB32 parallel port I/O protocol require a DRB32 extension module, which converts the DRB32 I/O port protocol to a non-DRB32 protocol.

The DRB32 uses odd parity on its data path. Figure 1-1 shows the DRB32 adapter (T1022).

BU-2605

Figure 1-1 DRB32 Adapter (T1022)

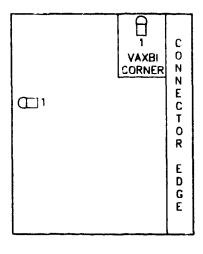

#### 1.2 DRB32 HARDWARE COMPONENTS

The DRB32 hardware has three subsystems:

- VAXBI interface

- 32-bit parallel I/O port

- T-11 subsystem

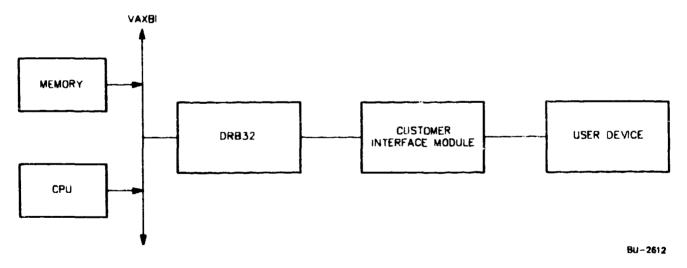

The DRB32 data path consists of the 32-bit parallel I/O port and the VAXBI interface. The T-11 is not part of the direct data transfer path. These components are shown in Figure 1-2.

Figure 1-2 DRB32 Simplified Block Diagram

A VAXBI backplane cable connects the DRB32 I/O port to a device within the same system enclosure. If an extension module is needed, it is connected to the DRB32 I/O port by another VAXBI backplane cable. The extension module I/O port is connected to a connector panel, or another device in the same enclosure.

See Chapter 2 for a functional description of the DRB32.

#### 1.3 DRB32 OPTIONS

The DRB32 is available in three options:

- DRB32-M

- DRB32-E

- DRB32-W

- T1023-00

- T1023-YA

These options are described in the following sections.

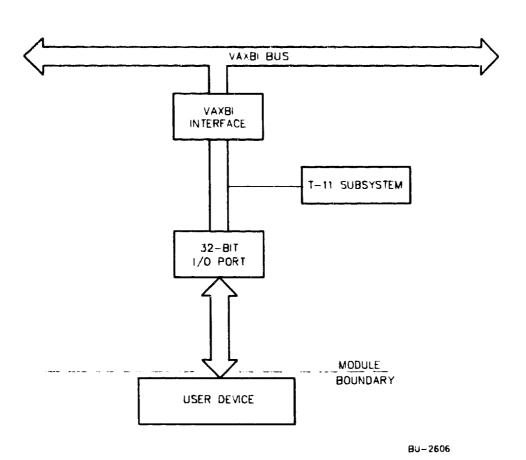

## 1.3.1 DRB32 Main Option (DRB32-M)

The DRB32-M is the basic DRB32 option and is designed for applications in which all cabling is kept within a single cabinet. Some examples are:

- Mount your equipment within a DEC STD FCC-compliant cabinet along with the BA32 box containing the DRB32.

- Connect the processor system cabinet to your equipment cabinet to form an FCC-compliant envelope.

- Design your own OEM box that can contain the DRB32 (your cabinet must also contain the VAXBI, as well as your own equipment).

The DRB32-M is the basic intracabinet DRB32 option. This option consists of the primary DRB module (T1022). A set of cables (CK-DRB32-L\*) available in various lengths connects the DRB32 to the customer equipment within the same EMI/RFI tight enclosure. Each cable has a 30-pin Berg connector at both ends. The electrical interface consists of FAST (Fairchild Advanced Shottky TTL) logic.

This option is designed to be compliant with FCC regulations when fully contained within an FCC-compliant cabinet. It is not designed to be FCC compliant with the cables exiting from an RFI/EMI shielded cabinet. The DRB32-M option is shown in Figure 1-3.

#### Introduction

Figure 1-3 DRB32 Main Option (DRB32-M)

## 1.3.2 DRB32 External Option (DRB32-E)

This option is for situations in which user equipment must be separate from the cabinet containing the DRB32. Therefore, a cable must connect the two cabinets. A compatible bulkhead connector must be provided for the bulkhead of the customer's cabinet.

The DRB32-E external cable driving option is designed to drive an intercabinet cable that is up to 40 feet (12 meters) long. The external cable is designed to be RFI/EMI tight (to comply with FCC requirements). The electrical interface is a combination of differential-drive TTL and controlled-threshold TTL. The DRB32-E option is shown in Figure 1-4.

Bu-2608

Figure 1-4 DRB32 External Cable Driving Option (DRB32-E)

#### 1.3.3 DRB32/DR11W Option (DRB32-W)

The DRB32-W option is provided for the customer with equipment currently designed to interface to the DR11-W. This option provides a means of connecting your current equipment with a VAXBI system without requiring a UNIBUS subsystem.

Since the DRB32-M option provides significantly higher performance than the DRB32-W option, redesigning the USER hardware to interface directly with the DRB32-M option would provide the benefits of increased throughput. Table 1-1 shows the data transfer rates for two of the DRB32 options.

#### NOTE

Please review Section 4.5 OPTIMIZING DATA TRANSFER SPEED, of this manual. This section supplies examples of how data transfer rates are calculated.

Table 1-1 Data Transfer Rates (MB/Second)

| Adapter | READ from<br>8200,8300<br>VAXBI<br>Memory | WRITE to<br>8200, 8300<br>VA XBI<br>Memory | READ from<br>9500, 8550,<br>8700, 8800<br>Priv. Memory | WRITE to<br>8500, 8550,<br>8700, 8800<br>Priv. Memory |  |  |

|---------|-------------------------------------------|--------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|--|--|

| DRB32-M | 6.0                                       | 6.7                                        | 3.3                                                    | 4.7                                                   |  |  |

| DRB32-W | 3.1                                       | 3.6                                        | 3.1                                                    | 3.6                                                   |  |  |

The DRB32-W option is an intracabinet connector (as is the DRB32-M). There are no specific provisions to make this device FCC compliant when used as an intercabinet connection. The DRB32-W option is shown in Figure 1-5.

#### NOTE

Two versions of the DRB32-W option exist. For a description of the differences between these two versions, please refer to Appendix C. When we talk about the DRB32-W option in this technical manual, we are talking about both versions unless we specifically mention both versions separately. The two versions of the DRB32-W module are the T1023-00 (produced before July 1990) and T1023-YA (produced after July 1990).

Figure 1-5 DRB32-W Option

#### 1.4 SOFTWARE

The DRB32 software is included in a VMS-layered product called DRB32VMSDRIVERS and must be ordered separately.

The following software is available for the DRB32-M and DRB32-E:

- VMS device driver (UQDRIVER) for the DRB32-M and DRB32-E

- Subroutine package for communications between two VAXBI systems through a back-to-back DRB32 link (DRB32\$MESSAGE)

- Test code for drivers (DRB32\$QIQ)

- MACRO and object libraries

- Command procedures to load and build the driver and test programs.

#### Introduction

The following software is available for the DRB32-W:

- VMS device driver to support DR11-W interfaces (UQWDRIVER)

- Test code for drivers (DRB32\$WQIO)

- MACRO and object libraries

- Command procedures to load and build the driver and test programs.

The software and its installation are described in the DRB32 Programmer's Manual.

The diagnostics are available and are described in the DRB32 Hardware Installation Guide.

#### 1.5 DRB32 CONFIGURATIONS

The DRB32 is available in two configurations:

- Intraenclosure DRB32

- Interenclosure DRB32

In the intraenclosure DRB32, both ends of the DRB32 data path and the cable connecting the DRB32 to the user device are completely enclosed in the same RFI-tight, FCC-compliant enclosure. This configuration is presented in the DRB32-M option.

In the interenclosure DRB32, the DRB32 adapter and the user device are in two different cabinets, with cable running between them. The length of the cable (a maximum of 40 feet or 12 meters) affects the data transfer rate. This configuration is presented in the DRB32-E option. These configurations are intended for different types of user applications. Two sets of electrical specifications are available for these configurations; see Appendix A.

#### 1.6 STRATEGIES FOR CONNECTING TO THE VAXBI

The DRB32 is offered as the gateway to VAXBI systems. You can use the DRB32 to simplify the task of connecting your equipment to the VAXBI. You can choose from a number of ways to implement this connection. The following strategies range from the easiest implementation to the most time-consuming.

- Use the DRB32 hardware and software as supplied by Digital. Extensive testing of the DRB32 components means that this approach entails less risk.

- Use the DRB32 hardware and modify the supplied software. This could include extensive modification of the supplied device driver.

- Use the DRB32 hardware and write a device driver from scratch.

- Use the DRB32-M hardware and design a customer interface module. This may require modifications to the driver and other software. The DRB32-M supplies the customer with quick access to the VAXBI, no VAXBI license is needed if you use the DRB32-M module to interface with the VAXBI. The customer interface would be simpler to design than a full VAXBI option.

A customer interface module connects your user device to the DRB32 adapter. It fits into a VAXBI backplane and converts the DRB32 output signals and protocol into a different set of signals and protocol. These modules are not "VAXBI nodes" and, therefore, do not have a VAXBI corner, but they do occupy a slot in the VAXBI backplane. These modules draw power from the VAXBI backplane. An example of an interface module is the DR11-W converter module (T1023) that is part of the DRB32-W option.

• Design a new VAXBI option. This requires a VAXBI license and is expensive in development time, but may be a good solution for some specialized applications.

For many applications, the use of the standard DRB32 is the best solution.

# 1.7 TYPICAL VAXBI/DRB32 SYSTEM CONFIGURATION

A typical DRB32 system configuration, in which the DRB32 adapter is used to connect a user device to the VAXBI and a VAX processor, is shown in Figure 1-6.

Figure 1-6 Typical DRB32 System Configuration

#### Introduction

A DRB32-W system configuration (including the basic DRB32 module and the T1023 DRW-11 converter module) is shown in Figure 1-7.

Figure 1-7 Typical DRB32-W Configuration

A DRB32 system configuration with a customer interface modale is shown in Figure 1-8.

Figure 1-8 DRB32 System Configuration with Interface Module

# CHAPTER 2 FUNCTIONAL DESCRIPTION

This chapter provides a functional description of the DRB32 adapter. The following topics are covered in this chapter:

- Block-diagram description of DRB32 module

- VAXBI transactions for the DRB32

- DRB32 address space

- DRB32 power-up sequence.

The DRB32 is an adapter that provides fast data transfers between Digital's VAXBI systems and user devices such as array processors, A/D converters, and high-speed instrumentation. The DRB32 provides a simple connection for your devices to VAXBI systems. Large, fast data transfers are the major advantages of the DRB32.

The DRB32 is optimized for large DMA transfers in Block mode. Block mode allows for transfers up to 982,528 bytes without processor intervention. The DRB32 hardware has double buffering that allows DMA transfers that are larger than this 982,528 bytes limit. Data transfers can also be made in Data mode, in which a host processor on the VAXBI directly reads or writes the DRB32 register that sends and receives data from the user device.

The DRB32 uses map registers to translate virtual addresses to VAXBI physical addresses. The DRB32 map register area is 1919 longwords. Mapped adapters require a process running in a VAX system to load map registers into the adapter for virtual-to-physical address conversion. Transfer widths are selected by the user. The DRB32 can handle longword (32 bit), word (16 bit), or byte (8 bit) transfers. However, the selection of 16- or 8-bit widths results in lower performance. The DRB32 uses odd parity.

#### 2.1 BLOCK-DIAGRAM DESCRIPTION OF THE DRB32 MODULE

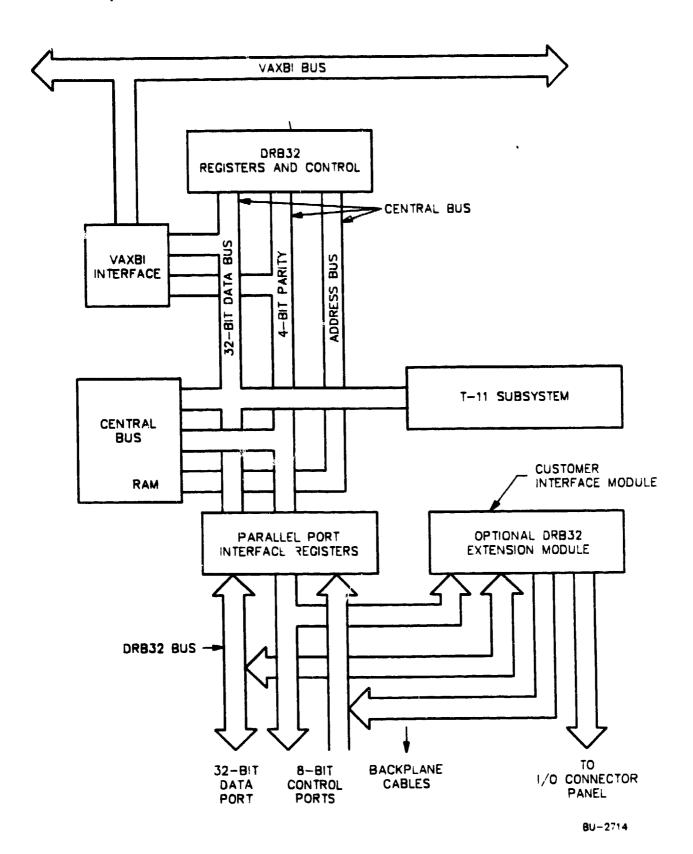

The major blocks of the DRB32 are the following:

- Parallel I/O port

- VAXBI interface

- T-11 subsystem.

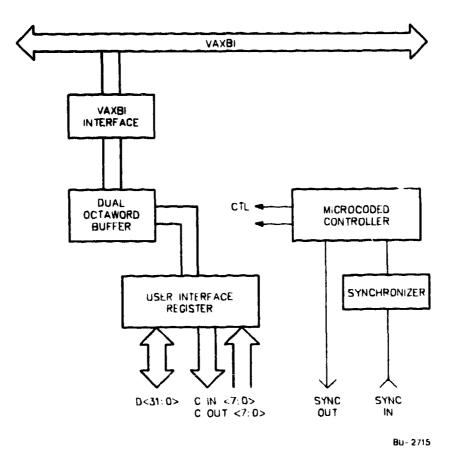

The DRB32 is a parallel I/O port (with a 32-bit, half-duplex data path and dual, 8-bit duplex control paths) that connects the VAXBI bus and a user device. The DRB32 parallel port has a user interface with signals for data, control, and device status. Attached to the parallel I/O port is a T-11 subsystem that performs module self-test. This section describes the three major parts of the DRB32 and some of the components of those parts. The user interface of the parallel I/O port is described in more detail in Chapter 4 of this manual. A block diagram of the DRB32 is shown in Figure 2-1.

Figure 2-1 DRB32 Block Diagram

In Figure 2-1, the parallel I/O port includes the DRB32 microcontroller, the central bus, the CB (central bus) RAM (containing map registers) and the DRB32 user interface. The user interface has a 32-line (plus four parity bits) data path, two 8-bit (8-line plus two parity bits) control paths, as well as two device status signals.

The T-11 section of the DRB32 is a complete microcomputer subsystem, with a 10 MHz T-11 microprocessor, RAM, and ROM. The ROM contains self-test.

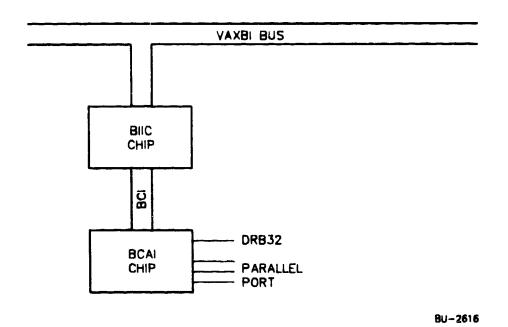

The VAXBI interface consists of the BIIC and BCAI chips. The BIIC handles VAXBI protocol, and the BCAI does byte alignment and provides some buffering.

The following sections describe the three major components in more detail.

#### 2.1.1 Parallel I/O Port

The parallel I/O port of the DRB32 includes a microcontroller, the central bus, the CB (central bus) RAM, a 32-bit, half-duplex data port (with parity bits), and an 8-bit duplex control port. See Figure 2-1.

The DRB32 microcontroller times and controls all data transfers between the VAXBI and the user device.

The 32-bit data path carries the data between the VAXBI and the user device. It is a half-duplex data path, meaning that data flows in only one direction at a time and the path must be "turned around" for data to be transferred in the opposite direction.

The two 8-bit control paths carry control and protocol information. The central bus connects the microcontroller, the CB RAM, the VAXBI interface, the T-11, the data and parity buses, and the user device (through the user interface).

The CB RAM contains the map registers and provides a buffer area for communications between the VAXBI and the T-11.

The parallel port interface moves data between the user device and the DRB32 with positive confirmation. See Chapter 4 for more information on the parallel port interface.

# 2.1.1.1 Features of the 32-Bit Parallel I/O Port Data Path - The 32-bit parallel I/O port data path has the following features:

- Half duplex

- DMA (block) or Programmed I/O (Data) mode data transfers

- Large block transfers without processor intervention (up to 982,528 bytes)

- Fast data transfer rate

- Optional odd parity, one parity bit per data byte

- Two sets of transfer control and status registers for double buffering

- 32-, 16-, or 8-bit data path.

#### **Functional Description**

Since the DRB32 is a half-duplex device, transfers occur in one direction until the block transfer is finished. At that point, you can set the data flow to the opposite direction.

Block or Programmed I/O mode transfers can be selected by the user. To achieve high data transfer rates, see the suggestions in the section on "Optimizing Data Transfer Speed" in Chapter 4.

- 2.1.1.2 Features of the Two 8-Bit Control Paths The two 8-bit control paths of the DRB32 parallel port have the following features:

- 8 bits in, 8 bits out

- Can be used as either 8-bit data paths or eight control lines.

- Odd parity in each direction.

See section 4.3 of this manual for more information on the user interface control path.

- 2.1.1.3 Parity The DRB32 can either accept odd parity on a per-byte basis for data from the parallel port, or internally generate parity for data before it is sent on the VAXBI. Parity is accepted from the VAXBI by the DRB32 and stored for map registers in the CB RAM. The parity is recalculated and checked when the map registers are combined with the Byte Offset Register to form the physical address.

- 2.1.1.4 Central Bus RAM The CB RAM has 2K longwords (8K bytes) of storage that contain the map and control registers. The VAXBI uses the CB RAM to allow long continuous data transfers with Current and Next map register areas. The map register area in the CB RAM is segmented by software into two areas, a Current and Next set of map registers. The host processor first loads the Current map registers, and then loads the control and map registers for the Next segment transfer while the Current segment transfer is underway. When the Current registers are empty and that segment transfer is complete, the DRB32 checks to see if the Next registers are loaded. If they are, the DRB32 transfers their contents to the Current registers, and performs the indicated segment transfer.

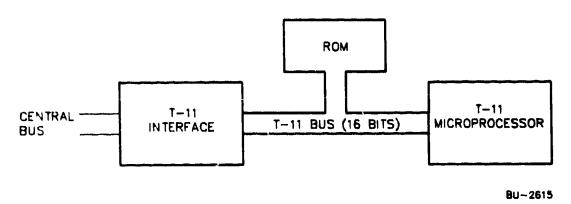

#### 2.1.2 T-11 Microprocessor Subsystem

The T-11 section of the DRB32 is a complete microcomputer subsystem. This subsystem contains:

- 16-bit PDP-11 microprocessor

- Diagnostic self-test in ROM

- 16-bit data bus

- An interface to the central bus of the DRB32.

The T-11 does not recognize or generate parity. Figure 2-2 is an illustration of the T-11 subsystem.

Figure 2-2 T-11 Subsystem

#### 2.1.3 VAXBI Interface

The DRB32 responds to VAXBI master transactions as a VAXBI slave port. The DRB32 also can initiate master VAXBI transactions for data transfers, VAXBI interrupt transactions, and VAXBI loopback transactions. Figure 2-3 is an illustration of the VAXBI interface for the DRB32.

Figure 2-3 VAXBI Interface for the DRB32

The BIIC chip (Backplane Interconnect Interface chip) connects the DRB32 to the VAXBI. This chip handles all the bus protocol associated with data transfers on the VAXBI. It also handles data transfers and interrupt transactions.

#### **Functional Description**

The BCAI chip (BCI Adapter Interface Chip) provides high-speed data flow from the DRB32 to the BIIC. (BCI or VAXBI Chip Interface refers to the adapter side of the BIIC.) The BCAI generates and checks parity, and provides a dual-octaword buffer to smooth data transfers to the VAXBI. The BCAI also performs data alignment, therefore it allows user data buffers to start and end on any byte boundary in memory, while the data flows through the parallel port as aligned longwords.

#### 2.2 VAXBI TRANSACTIONS

The DRB32 can act as bus master or respond as a slave node to VAXBI transactions. On the VAXBI, the node that gains control of the bus for a command transaction is the master. The node that responds is the slave. This section describes the following:

- VAXBI transactions initiated by the DRB32 as bus master

- DRB32 responses as slave node to VAXBI transactions.

#### 2.2.1 DRB32 Master VAXBI Transactions

The DRB32 can initiate the following master VAXBI transactions:

- Octaword Read

- Octaword Write

- Masked Octaword Write with Cache Intent (WMCI)

- Interrupt (INTR).

- 2.2.1.1 READ The DRB32 issues octaword READ transactions for all data transfers from the VAXBI to the user device.

- 2.2.1.2 WRITE The DRB32 issues octaword WRITE transactions for all data transfers from the user device to the VAXBI. First and last segment transfers, however, may use a masked octaword WRITE (WMCI). If the first and last segments are complete octawords, a WRITE transaction is used. If the first and last segments are not complete octawords, a masked octaword WRITE (WMCI) is used to align the data to octaword boundaries.

- 2.2.1.3 Masked Octaword WRITE (WMCI) The DRB32 issues masked octaword WRITE (WMCI) transactions for the first and last VAXBI transaction of a segment transfer from the user device to the VAXBI, when the segment transfer is not a complete octaword. The first masked octaword WRITE is used to align the user data to octaword boundaries on the VAXBI. The last masked octaword WRITE is used to transfer the exact number of bytes left in a data transfer.

- 2.2.1.4 Interrupt (INTR) The DRB32 initiates a VAXBI interrupt (INTR) transaction for the following reasons:

- Current segment is complete

- I/O Control Register (IOCTL) change of state

- Errors.

The corresponding bit in the DRB32 Interrupt Enable Register (DRBIE) must be set for the DRB32 to issue the INTR transaction.

#### 2.2.2 DRB32 Slave Response to VAXBI Commands

The DRB32 responds as a slave node to READ-type, WRITE-type, and data control commands issued by the VAXBI. The purpose of these commands is to allow the VAXBI node to read data from, or write data to, the DRB32's registers. The VAXBI node that originates these commands is the master node in the transaction.

READ-type commands are VAXBI transactions that the DRB32 responds to as if they were READ commands. READ-type commands include:

- READ To Node Space

- Interlock Read with Cache Intent (IRCI)

- Read with Cache Intent (RCi).

WRITE-type commands are VAXBI transactions that the DRB32 responds to as if they were WRITE commands. WRITE-type commands include:

- WRITE To Node Space

- WRITE with Cache Intent (WCI)

- Unlock Write Mask with Cache Intent (UWMCI)

- Write Mask with Cache Intent (WMCI).

The data control commands that the DRB32 responds to include the following:

- Identify (IDENT)

- STOP.

The DRB32 does not support the following VAXBI transactions, and therefore sends NO ACK if it receives them.

- READ To Adapter Window Space

- WRITE To Adapter Window Space

- Interrupt (INTR)

- Invalidate (INVAL)

- Broadcast (BDCST)

- Interprocessor Interrupt (IPINTR).

The DRB32 responses to each VAXBI transaction are described in the following sections.

2.2.2.1 READ-Type Transactions – The DRB32 responds in the same way to the following READ-type transactions: READ, IRCI, and RCI. The DRB32 only supports longword READ transactions to the device register space, and responds with NO ACK to all other lengths of READ transactions.

Up to eight stalls may be issued before the transaction is acknowledged, because of contention for the Central Bus on the DRB32.

**2.2.2.2 WRITE-Type Transactions** – The DRB32 responds in the same way to the WRITE-type transactions: WRITE, WCI, UWMCI, and WMCI. The DRB32 only supports longword WRITE transactions to the device register space, and responds with NO ACK to all other lengths of WRITE transactions.

Up to eight stalls may be issued before the transaction is acknowledged, because of contention for the Central Bus on the DRB32. The DRB32 ignores the mask bits in the WMCI and UWMCI transactions.

**2.2.2.3 IDENT (Identify)** – IDENT transactions occur after the DRB32 issues an interrupt to the host processor. The host processor issues an IDENT transaction to find out what device issued the interrupt. The DRB32 sends an interrupt vector.

The DRB32 has two vectors: the user interface vector and the error vector. The user interface vector is loaded into the BHC User Interrupt Control Register by the operating system during the initial start-up sequence. The external vector (EX VECTOR) bit in the BHC User Interface Interrupt Control Register is cleared during start-up. The error vector is loaded into the Error Interrupt Control Register by the operating system during system initialization. The error vector is sent in response to IDENT when the BHC generates an interrupt because it detected an error. The DRB32 uses the user interface vector when it wishes to interrupt the host processor.

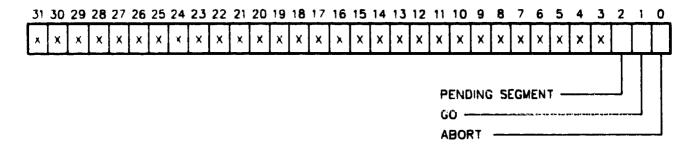

- **2.2.2.4** STOP Host processors use the STOP transaction to temporarily halt a node from issuing VAXBI transactions. A STOP transaction received by the DRB32 does the following:

- Terminates any DRB32 segment transfer

- Clears the Go bit in the Parallel Port CSR Register

- Stops any future transfers until the Parallel Port Control Register is reloaded

- Completes any pending VAXBI master transactions before stopping the DRB32.

The Pending Segment bit is not cleared by a STOP transaction.

#### 2.3 DRB32 ADDRESS SPACE

This section describes the following:

- VAXBI address space

- DRB32 address space as seen by the VAXBI.

The DRB32 does not implement window space.

# 2.3.1 VANBI Address Space Description

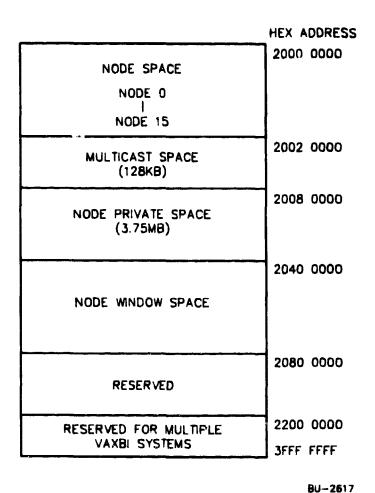

The 1024MB system address space on the VANBI is divided into two areas:

- Memory space (from address 0000 0000 through 1FFF FFFF hex)

- 1/O space (from address 2000 0000 through 3FFF FFFF hex).

the VAXBI node space. By assigning a section of node space to the DRB32, the VAXBI obtains access to the DRB32 address space. The VAXBI system I/O space is divided into several dedicated sections. One of these dedicated sections is

VAXBI node space consists of 16 blocks of I/O addresses that are allocated to the 16 possible VAXBI nodes. The size of each block is 8KB. A VAXBI node's node space assignment is based on that node's ID (0 through 15). The starting address of node spaces for nodes 1 through 15 is 2000 0000 plus 8K times the node ID. See Table 2-1.

Table 2-1 Node Space Base Address Assignments

| <del>50</del> . | m         | D          | C         | 8         | >         | ç         | ×         | 7         | 7          | · <b>J</b> i | <b>L</b>  | مد ً      | ۱.,      | _         | 0         | Vode Vo.    |

|-----------------|-----------|------------|-----------|-----------|-----------|-----------|-----------|-----------|------------|--------------|-----------|-----------|----------|-----------|-----------|-------------|

| 2001 E000       | 2001 C000 | 2001 \0000 | 2001 8000 | 2001 6000 | 2001 4000 | 2001 2000 | 2001-0000 | 2000 F000 | 2000 ( 000 | 2000 \000    | 2000 8000 | 2000 6000 | 000+0005 | 2000-2000 | 2000 0000 | Hev Address |

|                 |           |            |           |           |           |           |           |           |            |              |           |           |          |           |           |             |

#### **Functional Description**

The VAXBI system I/O space is shown in Figure 2-4.

Figure 2-4 VAXBI I/O Address Space

#### 2.3.2 DRB32 Address Space Description

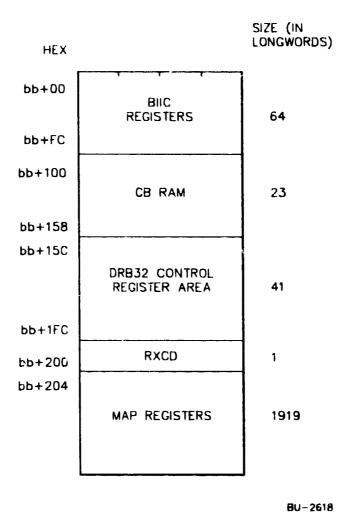

To any of the other VAXBI nodes, the DRB32 address space appears as node space on the VAXBI. A VAXBI node can communicate with the DRB32 through this node space and can see the BIIC registers, parallel port registers, map registers, and the RXCD (Receive Console Data) Register.

#### 2.3.3 DRB32 Address Space as Seen by the VAXBI

The DRB32 address space accessible to the VAXBI is shown in Figure 2-5.

BU-21

Figure 2-5 DRB32 Address Space

## 2.4 DRB32 POWER-UP SEQUENCE

The power-up sequence ensures that the DRB32 always starts up in a standard configuration. If necessary, your application can change these configurations while the application is running.

The DRB32 power-up sequence consists of the following:

- BIIC self-test executes

- DRB32 self-test executes

- The default configuration is set up

- The self-test LED lights and the Broke bit clears upon successful completion of the power-up sequence.

See Appendix A for a power-up timing diagram.

## CHAPTER 3 DRB32 REGISTER DESCRIPTIONS

This chapter describes the DRB32 registers. The DRB32 registers include BHC registers and DRB32 module registers.

The BIIC registers are physically located in the BIIC chip, which is the interface between the VAXBI and the DRB32. The DRB32 module registers include the parallel port registers, map registers in the CB RAM, the BCAI registers, and the RXCD register. The DRB32 module registers control the parallel port and enable error notification and interrupt services.

#### 3.1 BLIC REGISTERS

The BHC registers are listed in Table 3-1.

| Table | 3-1 | BHC. | Re | gisters |

|-------|-----|------|----|---------|

|-------|-----|------|----|---------|

|                  | DIK Regions                                |

|------------------|--------------------------------------------|

| VAXBI<br>Address | Register Name                              |

| bb+00            | Device Reg (DTYPE)                         |

| bb+04            | VAXBI Control and Status Reg (BICSR)       |

| bb+08            | Bus Error Reg (BER)                        |

| bb+0C            | Error Interrupt Control Reg (EINTRCSR)     |

| bb+10            | Interrupt Destination Reg (INTRDES)        |

| bb+14            | IPINTR Mask Reg                            |

| bb+18            | Force IPINTR/STOP Destination Reg          |

| bb+1C            | IPINTR Source Reg                          |

| bb+20            | Starting Address Reg                       |

| bb+24            | Ending Address Reg                         |

| bb+28            | BCI Control Reg                            |

| bb+2C            | Write Status Reg                           |

| bb+30            | Force IPINTR/STOP Command Reg              |

| bb+40            | User Interface Interrupt Control Reg       |

| bb+F0            | GPR 0 (self-test error code)               |

| bb+F4            | GPR 1 (DRB32 internal code revision level) |

| bb+F8            | General Purpose Reg 2                      |

| bb+FC            | General Purpose Reg 3                      |

#### **DRB32 Register Descriptions**

The BIIC registers are described below.

## 3.1.1 DTYPE—Device Register

This register is written by self-test. It should not be written by application code.

VAXBI : bb+0000

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------|---------------------------------------|--|--|--|--|--|--|--|--|--|

| DEVICE REVISION                                 | DEVICE TYPE                           |  |  |  |  |  |  |  |  |  |

|                                                 |                                       |  |  |  |  |  |  |  |  |  |

BU-2619

**Device Revision** <31:16>. This word indicates the current revision of the DRB32 hardware. It is written by self-test before the Broke bit in the VAXBI Control and Status Register is cleared.

Device Type <15:0>. This word is written by self-test before the Broke bit in the VAXBI Control and Status Register is cleared. It is loaded with the DRB32 device type (hex 0101).

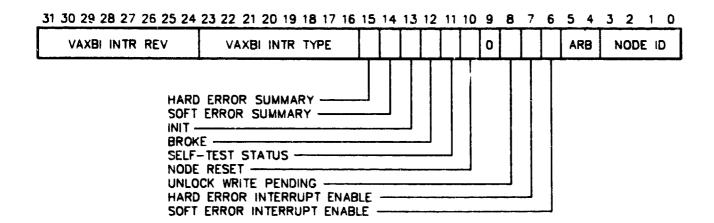

## 3.1.2 BICSR-VAXBI Control and Status Register

The VAXBI Control and Status Register provides status information about the VAXBI and determines DRB32 Arbitration mode.

VAXBI: bb+0004

BU--2620

**VAXBI Interface Revision - <31:24>.** This field indicates the revision of the BIIC in this DRB32. This field is READ-only.

VAXBI Interface Type - <23:16>. This field indicates the type of VAXBI interface on the DRB32. It is always 00000001.

HES - <15> - Hard Error Summary. When set, this bit indicates that one or more of the hard error bits in the Bus Error Register is set. This bit is READ-only.

SES - <14> - Soft Error Summary. When set, this bit indicates that one or more of the soft error bits in the Bus Error Register is set. This bit is READ-only.

INIT - <13> - INIT bit. The DRB32 ignores this bit.

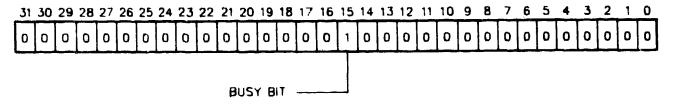

BROKE - <12>. The DRB32 clears this bit when the module has passed all internal self-tests. If this bit is set, the DRB32 is either in the process of running its internal self-test or has failed it. This bit can be cleared by writing a 1 to it, but should only be READ.

STS - <11> - Self-Test Status. This bit indicates the result of (only) the BIIC internal self-test. If the BIIC internal self-test is passed, the bit is a 1. If the BIIC internal self-test is failed, the bit is 0, the BIIC VAXBI drivers are disabled, and the chip cannot drive the bus. If the STS bit is reset, the WRITE transaction used to set the bus receives a NO-ACK response. This bit is READ/WRITE.

NRST - <10> - Node Reset. Writing a 1 to this bit initiates a complete DRB32 module self-test. When this bit is written (with a 1), the STS bit must also be written (with a 1) to ensure proper operation of the WRITE-type transaction. READs always return a 0. When the NRST bit is set, the DRB32 does not return ACK to slave transactions it receives, until DRB32 self-test successfully completes. Before completion of self-test, NO-ACKs are returned.

UWP - <08> - Unlock Write Pending. When set, this bit indicates that a Interlock Read with Cache Intent (IRCI) transaction has been successfully completed by this node and there has not yet been a subsequent Unlock Write Mask With Cache Intent (UWMCI) command.

HEIE - <07> - Hard Error Interrupt Enable. Determines whether an error interrupt is generated by the DRB32 when HES is asserted.

SEIE - <06> -Soft Error Interrupt Enable. Determines whether an error interrupt is generated by the DRB32 when SES is asserted.

ARB - <05:04> - Arbitration Control. The two ARB bits determine the DRB32 Arbitration mode. See Table 3-2 below.

Table 3-2 DRB32 Arbitration Modes

| Code | Arbitration Mode             |

|------|------------------------------|

| 00   | Dual round-robin arbitration |

| 01   | Fixed high priority          |

| 10   | Fixed low priority           |

| 11   | Disable arbitration          |

#### **DRB32 Register Descriptions**

NODE ID - <03:00>. The DRB32 node ID is dependent upon the node ID plug placed on the VAXBI The node ID is automatically loaded during the power-up sequence. This field is READ-only.

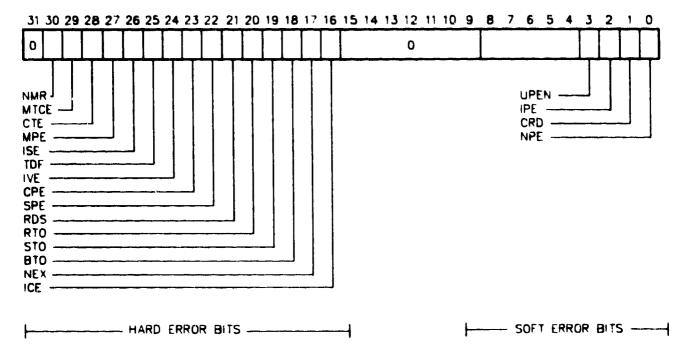

## 3.1.3 BER—Bus Error Register

This register indicates hard and soft errors detected on the bus.

VAXBI : 66+0008

BU- 2621

NMR - <30> - NO-ACK to Multi-Responder Command Received. This bit is set by the bus master if it receives a NO-ACK command confirmation for an INVAL, STOP, INTR, IPINTR, BDCST, or RESERVED command.

MTCE - <29> - Master Transmit Check Error. This bit is set if transmitted data during a master transaction does not agree with received data, in cycles where the master is the only source of data.

CTE - <28> - Control Transmit Error. This bit is set if the BIIC detects a deasserted state on VAXBI NO ARB L, VAXBI BSY L and VAXBI CNF<2:0> L when it is trying to assert them.

MPE - <27> - Master Parity Error. This bit is set if the master detects a parity error on the bus during a READ-type or vector ACK data cycle. This bit can be set during BIIC self-test. It is cleared by the firmware initialization routine after the DRB32 self-test has passed.

**ISE** - <26> - Interlock Sequence Error. This bit is set if this node successfully completes a UWMCI transaction when the Unlock Write Pending (UWP) bit in the BCI Control Register is not set.

TDF - <25> - Transmitter During Fault. The TDF bit is set by either the master or the slave following the detection of a parity error during a cycle in which that node was responsible for transmitting proper parity on the VAXBI.

IVE - <24> - IDENT Vector Error. This bit is set by the slave if, after sending an interrupt vector to the master that issued an IDENT, anything but an ACK confirmation is received.

CPE - <23> - Command Parity Error. This bit is set when the BIIC detects a parity error in a command/address cycle.

SPE - <22> - Slave Parity Error. This bit is set by the slave if the BHC detects a parity error during a WRITE-type ACK or STALL Data Cycle, or BDCST ACK Data Cycle.

RDS - <21> - Read Data Substitute. This bit is set if a Read Data Substitute or RESERVED status code is received during a READ-type or IDENT (for vector status) transaction.

RTO - <20> - Retry Timeout. This bit is set if the master receives 4096 consecutive RETRY responses from the slave for the same master port transaction

STO - <19> - Stall Timeout. This bit is set if the slave port asserts the STALL code on the BCI RS<1:0 - 1 lines for 128 consecutive cycles.

BTO - <18> - Bus Timeout. This bit is set if the BHC is unable to start at least one pending transaction before 4096 eyeles have elapsed.

NEX - <17> - Non-Existent Address. This bit is set when a NO-ACK response is received for a READ-type or WRITE-type command sent by the BHC.

ICE - <16> - Illegal Confirmation Error, This bit indicates that a RESERVED or illegal confirmation code has been received during a transaction in which the BHC is involved.

UPEN - <03> - User Parity Enable. This is a RFAD-only bit that indicates the BHC parity mode. A 1 indicates the BHC is configured for user-generated parity, while a 0 indicates the BHC will provide the parity generation. Since the BCAI always generates parity for the DRB32, this bit must always be set.

IPE - <02> - ID Parity Error. This bit indicates that a parity error was detected on the encoded master ID during an embedded ARB cycle.

CRD - <01> - Corrected Read Data. This bit indicates that a corrected read data status code was received during a READ-type transaction initiated by the master port.

NPE - <00> - Null Bus Parity Error. This bit indicates that ODD parity was detected on the bus during the second cycle of a two cycle sequence during which VAXBI NO ARB L and VAXBI BSY L were unasserted.

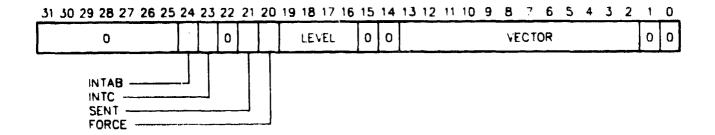

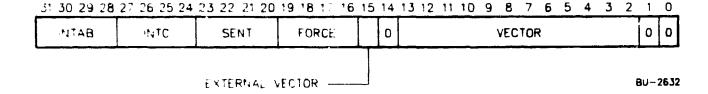

## 3.1.4 EINTRCSR—Error Interrupt Control Register

The Error Interrupt Control Register controls the operation of interrupts initiated by a BHC-detected bus error or by a Force bit set in this register.

VAXBL: bb+000C

BU-2622

INTAB - <24> - Interrupt Abort. The Interrupt Abort bit is set if an INTR command sent under control of this register is aborted. Reset this bit by writing a 1 to it.

**INTC** - <23> - Interrupt Complete. This bit is set when the vector for an error interrupt has been successfully transmitted or if an INTR command sent under the control of this register has aborted. This bit is reset when the interrupt request is removed.

SENT - <21>. The SENT bit indicates that an INTR command for this interrupt has been sent, and that an IDENT command is expected. This bit is cleared during an successful IDENT command matching the interrupt.

**FORCE** – <20>. This bit is set to initiate an error interrupt request.

LEVEL - <19:16>. The LEVEL field determines the level(s) at which INTR commands are transmitted under the control of this register.

**VECTOR** – <13:2>. This field contains the vector used during error interrupt sequences.

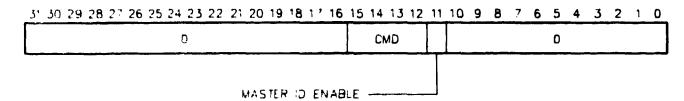

## 3.1.5 INTRDES—Interrupt Destination Register

This register is loaded with the VAXBI nodes to be interrupted when a DRB32 sends an interrupt. If bit  $\pm 0$  is set. Node 0 is the target of the interrupt. If bit  $\pm 2$  is set. Node 2 is the target of the interrupt.

VAXBL: bb+0010 R/W

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------------------------------------------------|---------------------------------------|

| 0                                               | INTERRUPT DESTINATION                 |

BU-2623

## 3.1.6 IPINTRMSK-Interprocessor Int grupt Mask Register

This register contains the mask that determines which nodes are permitted to send interprocessor interrupts to the DRB32. Since interprocessor interrupts are not supported on the DRB32, IPINTRMSK is set to (hex) 0000 by the VAXBI operating system at power-up, after the Broke bit is cleared by the DRB32 self-test.

VAXBi : bb+0014

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| IPINTR MASK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                     |

| THE THE TAX TO SEE TH |                                       |

BU-2624

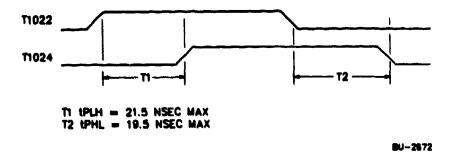

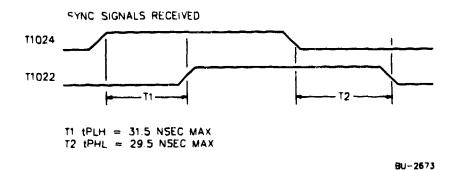

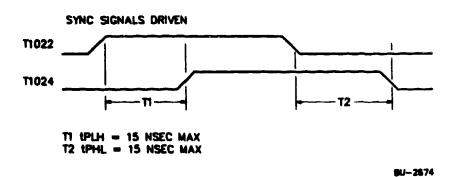

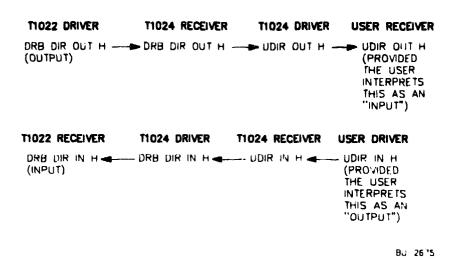

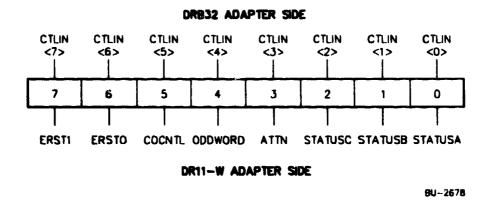

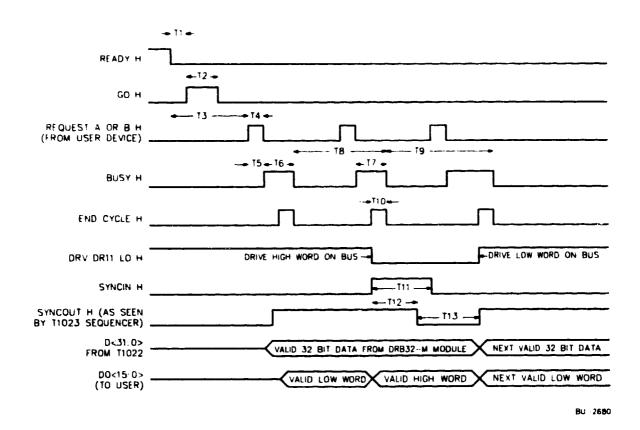

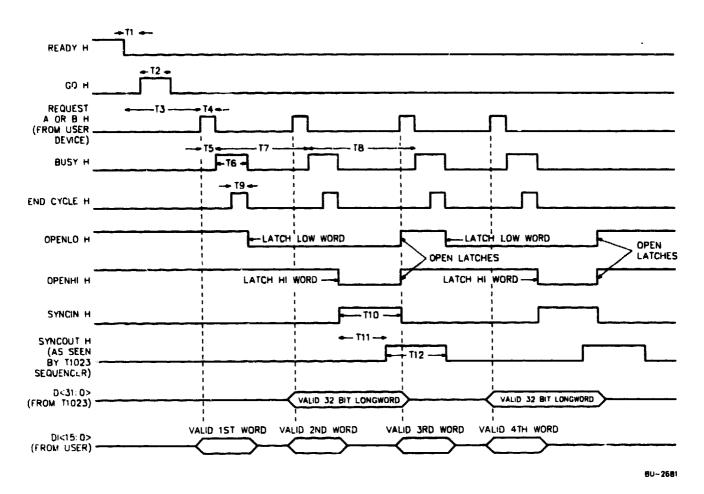

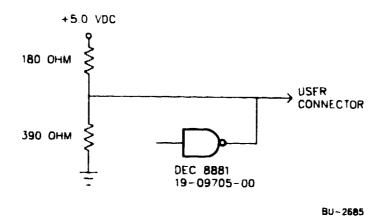

## 3.1.7 FIPSDES—Force Interprocessor Interrupt/Stop Destination Register