# VAX 8600/8650 SBIA Technical Description

Prepared by Educational Services of Digital Equipment Corporation

#### © Digital Equipment Corporation 1985, 1986. All Rights Reserved.

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

Printed in U.S.A.

The manuscript for this book was created on a VAX-11/780 system and, via a translation program, was automatically typeset by Digital's DECset Integrated Publishing System. The book was produced by Educational Services Development and Publishing in Marlboro, MA.

The following are trademarks of Digital Equipment Corporation.

DEC P/OS

DECmate Professional

DECUS Q-Bus

DECwriter Rainbow

DIBOL RSTS

MASSBUS RSX

RT UNIBUS VAX VMS VT

Work Processor

## **CONTENTS**

|           |                                                | Page |

|-----------|------------------------------------------------|------|

| CHAPTER 1 | INTRODUCTION                                   |      |

| 1.1       | MANUAL SCOPE AND RELATED DOCUMENTS             | 1-1  |

| 1.2       | GENERAL DESCRIPTION                            |      |

| 1.3       | PHYSICAL DESCRIPTION                           | 1-2  |

| 1.3.1     | Module Partitioning                            |      |

| 1.3.1.1   | SBA Module                                     | 1-2  |

| 1.3.1.2   | SBS Module                                     | 1-3  |

| 1.4       | SBIA DATA TRANSFERS                            | 1-3  |

| 1.4.1     | CPU Write                                      | 1-3  |

| 1.4.2     | CPU Read                                       | 1-3  |

| 1.4.3     | DMA Transfers                                  | 1-3  |

| 1.4.3.1   | DMA Write                                      | 1-4  |

| 1.4.3.2   | DMA Read                                       | 1-4  |

| 1.5       | PHYSICAL MEMORY ADDRESSES                      |      |

| 1.6       | SBIA ERROR DETECTION                           |      |

| 1.7       | SBIA REGISTERS                                 | 1-7  |

| CHAPTER 2 | FUNCTIONAL DESCRIPTION                         |      |

| 2.1       | CHAPTER OVERVIEW                               | 2-1  |

| 2.2       | SBIA BASIC BLOCK DIAGRAM                       |      |

| 2.2.1     | CPU/SBIA State Machine                         |      |

| 2.2.2     | Register File                                  |      |

| 2.2.3     | S-Data Assembly                                |      |

| 2.2.4     | SBI Interface                                  |      |

| 2.2.5     | SBI Protocol                                   | 2-3  |

| 2.2.6     | A-Data Assembly                                |      |

| 2.2.7     | Clock Logic                                    |      |

| 2.2.7.1   | ABus Clock Logic                               |      |

| 2.2.7.2   | SBI Clock Generation                           |      |

| 2.2.8     | DMA Buffer Control and Request Synchronization | 2-6  |

| 2.2.9     | ECL Address and Read/Write Control             | 2-6  |

| 2.2.10    | TTL Address and Read/Write Control             | 2-6  |

| 2.2.11    | Interrupt Logic                                | 2-6  |

| 2.2.12    | SBIA Registers                                 | 2-6  |

| 2.2.13    | SBI Arbitration Chips                          | 2-7  |

| 2.3       | CPU TRANSACTION FLOWCHARTS                     |      |

| 2.3.1     | Starting the State Machine                     | 2-7  |

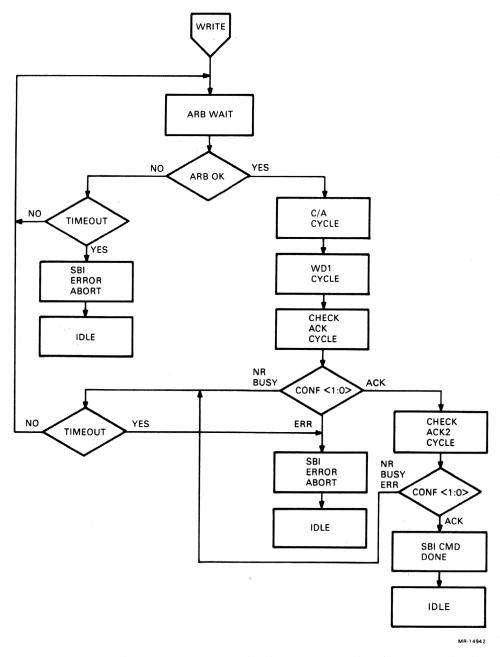

| 2.3.2     | CPU Write                                      |      |

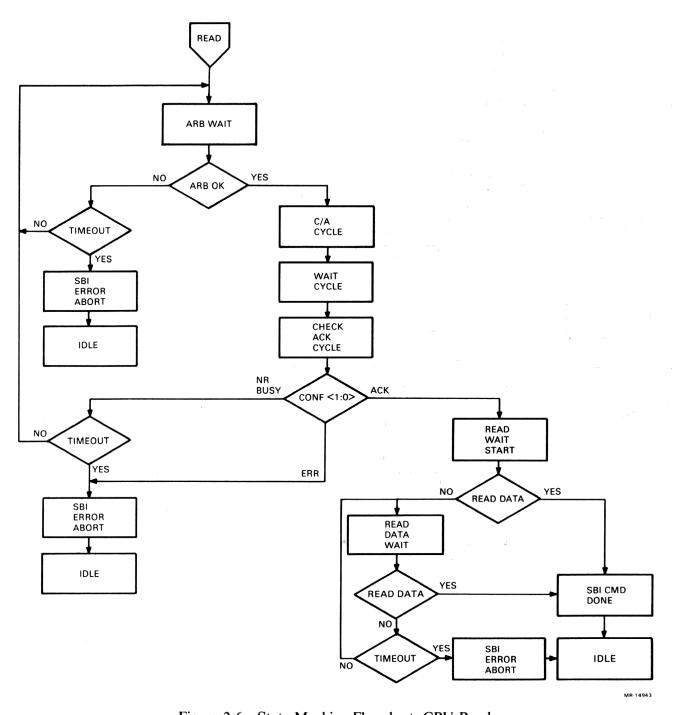

| 2.3.3     | CPU Read                                       | 2-10 |

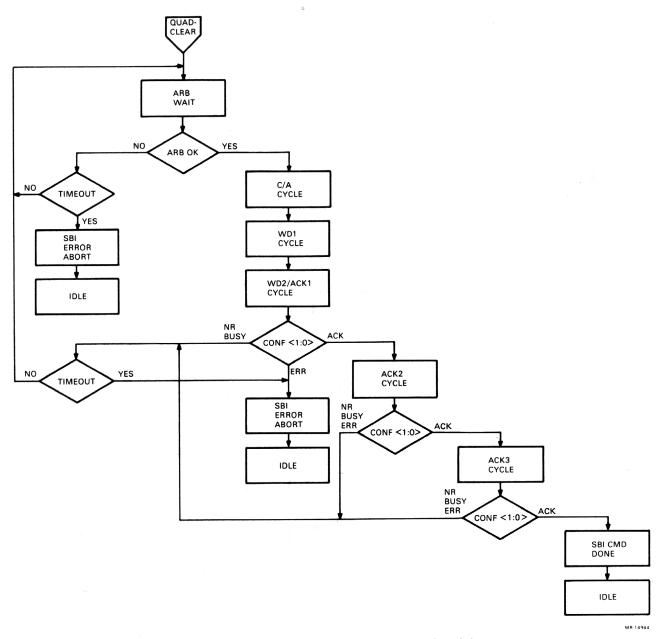

| 2.3.4     | Quadclear                                      |      |

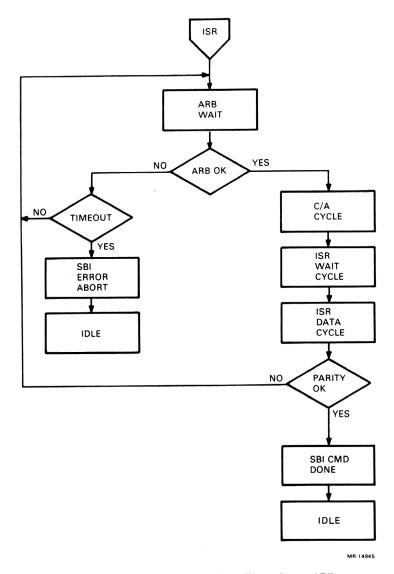

| 2.3.5     | Interrupt Summary Read                         | 2-13 |

## **CONTENTS (Cont)**

|           |                                                                    | Page  |

|-----------|--------------------------------------------------------------------|-------|

| 2.4       | SBIA TRANSFERS NOT USING STATE MACHINE                             | 2-15  |

| 2.4.1     | SBIA Register Writes or Reads                                      | 2-15  |

| 2.4.2     | Unjam                                                              | 2-15  |

| 2.4.3     | DMA Transactions                                                   | 2-15  |

| 2.4.3.1   | DMA Write                                                          | 2-16  |

| 2.4.3.2   | DMA Read                                                           | 2-16  |

| CHAPTER 3 | DETAILED DESCRIPTION                                               |       |

| 3.1       | REGISTER FILE ORGANIZATION                                         | 3-1   |

| 3.1.1     | CPU Transaction Buffer                                             | 3-1   |

| 3.1.2     | DMAI Transaction Buffer                                            | 3-2   |

| 3.1.3     | DMAA, DMAB, or DMAC Transaction Buffers                            | 3-2   |

| 3.2       | CPU WRITE SBI NEXUS REGISTER                                       | 3-2   |

| 3.2.1     | Loading CPU Command/Address                                        | 3-2   |

| 3.2.2     | Loading CPU Write Data                                             | 3-2   |

| 3.2.3     | Addressing and Unloading the Register File for TTL Read            | 3-3   |

| 3.2.3.1   | Valid File Read                                                    | 3-4   |

| 3.2.3.2   | Double Unload                                                      | 3-5   |

| 3.2.4     | File Data Latch                                                    | 3-5   |

| 3.2.5     | Loading the Command/Address Latch                                  | 3-5   |

| 3.2.6     | Loading the Write Data Latch                                       | 3-5   |

| 3.2.7     | Starting the CPU-SBI State Machine                                 | 3-5   |

| 3.2.8     | CPU ARB WAIT                                                       | 3-5   |

| 3.2.9     | CPU Write SBI Nexus Register: Command/Address Cycle                | 3-6   |

| 3.2.10    | CPU Write SBI Nexus Register: Write Data Cycle                     | 3-8   |

| 3.2.11    | CPU Write SBI Nexus Register: Check ACK Cycle                      | 3-9   |

| 3.2.12    | CPU Write SBI Nexus Register: Check ACK2 Cycle                     | 3-10  |

| 3.2.13    | CPU Write SBI Nexus Register: Timeout                              | 3-10  |

| 3.3       | CPU READ SBI NEXUS REGISTER                                        | 3-10  |

| 3.3.1     | Loading CPU Command/Address for CPU Read SBI Nexus Register        | 3-10  |

| 3.3.2     | Addressing the Register File for TTL Read Nexus Register           | 3-11  |

| 3.3.3     | File Data Latch                                                    | 3-11  |

| 3.3.4     | Loading the Command/Address Latch for CPU Read SBI Nexus           | 2 11  |

|           | Register                                                           | 3-11  |

| 3.3.5     | Starting the CPU-SBI State Machine for CPU Read SBI Nexus Register | 3-11  |

| 3.3.6     | CPU Read SBI Nexus Register: CPU ARB Wait                          | 3-11  |

| 3.3.7     | CPU Read SBI Nexus Register: Command/Address Cycle                 | 3-12  |

| 3.3.8     | CPU Read SBI Nexus Register: Wait Cycle                            | 3-14  |

| 3.3.9     | CPU Read SBI Nexus Register: Check ACK Cycle                       | 3-14  |

| 3.3.10    | CPU Read SBI Nexus Register: Read Wait Start                       | 3-13  |

| 3.3.11    | CPU Read SBI Nexus Register: Read Data Wait                        | 3-13  |

| 3.3.12    | Sending Acknowledge for the Read Data Word                         | 3-13  |

| 3.3.13    | CPU Read SBI Nexus Register: Read Data Transfer to Register File   | 3-16  |

| 3.3.14    | CPU Read SBI Nexus Register: Register File TTL Write Address       | 3-1 / |

| 3.3.15    | CPU Read SBI Nexus Register: ABUS CPU BUF DONE                     | 3-1/  |

| 3.3.16    | CPU Read SBI Nexus Register: MBox Reads the Register File          | 3-1/  |

| 3.4       | CPU WRITE SBIA REGISTER                                            | 3-1/  |

| 3.4.1     | SBIA Address Recognition                                           | 3-18  |

## **CONTENTS (Cont)**

| •       |                                                                                    | Page         |

|---------|------------------------------------------------------------------------------------|--------------|

| 3.4.2   | Selecting and Writing the SBIA Register                                            | 3-18         |

| 3.4.3   | Selecting and Writing the SBIA Register CPU Write SBIA Register: ABUS CPU BUF DONE | 3-18         |

| 3.4.4   | CPU Write SBIA Register: ABUS CPU BUF ERROR                                        | 3-19         |

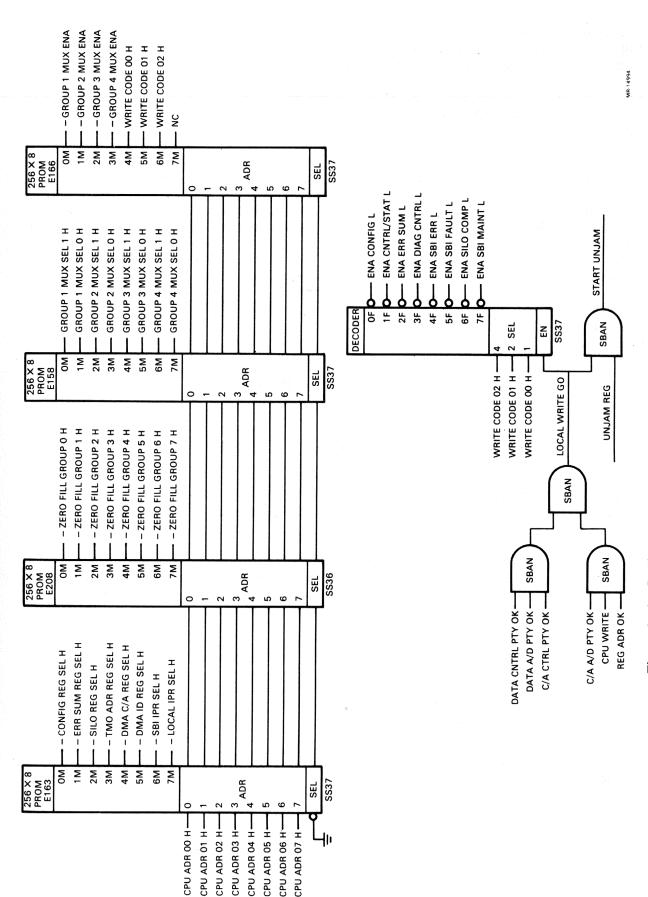

| 3.5     | CPU READ SBIA REGISTER                                                             |              |

| 3.5.1   | Register Data Bus                                                                  |              |

| 3.5.2   | Zero Fill                                                                          |              |

| 3.5.3   | Enabling Register Data to File Info Bus                                            | 3-24         |

| 3.5.4   | Register File TTL Write Address                                                    | 3-25         |

| 3.5.5   | CPU Read SBIA Register: ABUS CPU BUF DONE                                          | 3-25         |

| 3.5.6   | CPU Read SBIA Register: MBox Reads the Register File                               |              |

| 3.5.7   | CPU Read SBIA Register: ABUS CPU BUF ERROR                                         | 3-26         |

| 3.6     | INTERRUPT SUMMARY READ                                                             | 3-26         |

| 3.6.1   | Interrupt Requests                                                                 |              |

| 3.6.2   | EBox IPR Arbitration                                                               |              |

| 3.6.3   | EBox Microcode Generates the Read Address                                          | 3-26         |

| 3.6.4   | Command/Address                                                                    |              |

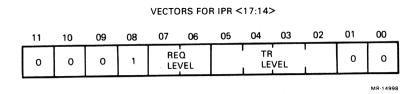

| 3.6.5   | Obtaining the Interrupt Vector for IPR 14-IPR 17                                   | 3-27<br>3-27 |

| 3.6.5.1 | IPR 14–IPR 17                                                                      | 3-27<br>2 27 |

| 3.6.5.2 | ISR CPU ARB Wait Cycle                                                             | 2 20         |

| 3.6.5.3 | ISR C/A Cycle                                                                      | 2 20         |

| 3.6.5.4 | ISR Wait Cycle                                                                     |              |

| 3.6.5.5 | ISR Data Cycle                                                                     |              |

| 3.6.5.6 | SBI CMD DONE                                                                       |              |

| 3.6.5.7 | Vector Transfer to the Register File                                               |              |

| 3.6.5.8 | ISR: TTL Register File Write Address                                               | 2 20         |

| 3.6.5.9 | MBox Reads Vector                                                                  |              |

| 3.6.6   |                                                                                    |              |

| 3.7     | Local Interrupt VectorQUADCLEAR                                                    |              |

| 3.7.1   | Quadalaar Command / Address Cyala                                                  | 3-30         |

| 3.7.1   | Quadclear Command/Address Cycle                                                    |              |

|         | Quadelear: Write Data Cycle 1                                                      |              |

| 3.7.3   | Quadelear: Write Data Cycle 2/ACK 1                                                |              |

| 3.7.4   | Quadelear ACK2 Cycle                                                               |              |

| 3.7.5   | Quadclear ACK3 Cycle                                                               |              |

| 3.7.6   | Quadclear Timeout                                                                  | 3-35         |

| 3.8     | QUADCLEAR FOR MICRODIAGNOSTICS                                                     | 3-33         |

| 3.9     | UNJAM                                                                              | 3-33         |

| 3.10    | DMA OVERVIEW AND BUFFER CONTROL                                                    |              |

| 3.10.1  | DMA Buffer Control                                                                 | 3-3/         |

| 3.10.2  | DMA Transaction Buffer Selection                                                   |              |

| 3.11    | DMA WRITE                                                                          | 3-40         |

| 3.11.1  | DMA Write: Command/Address Reception                                               | 3-40         |

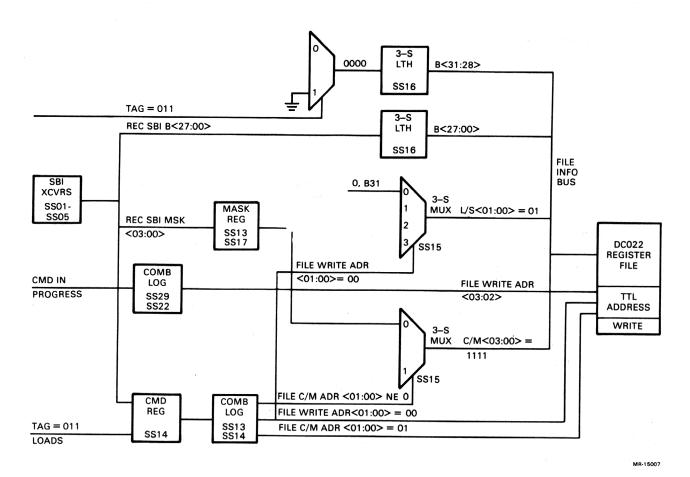

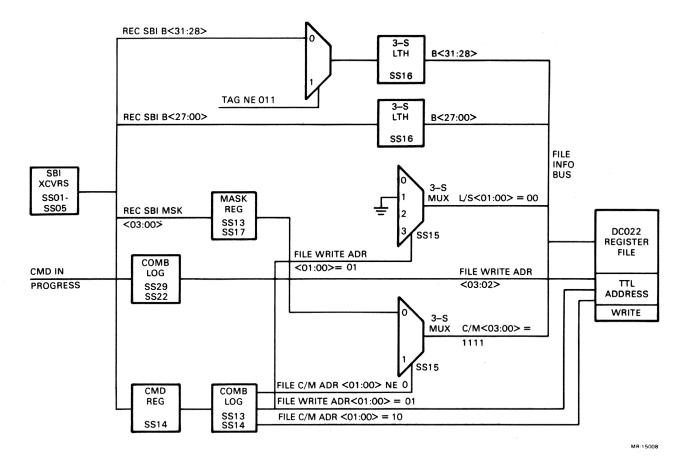

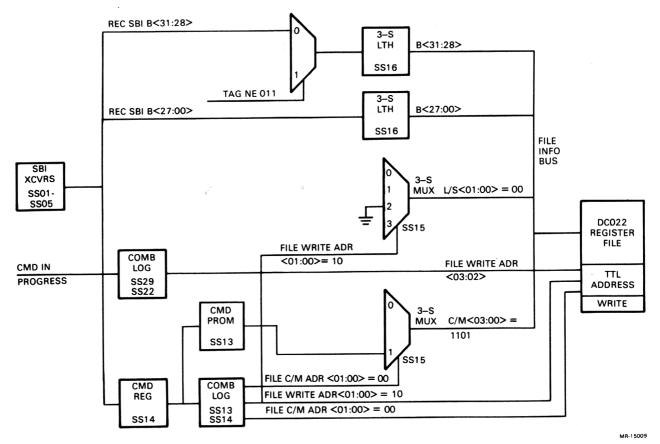

| 3.11.2  | DMA Write: Register File TTL Write Address Generation                              |              |

| 3.11.3  | DMA Write: A-Data Assembly Command/Address Transfer                                |              |

| 3.11.4  | DMA Write: A-Data Assembly Transfer of Write Data 1                                |              |

| 3.11.5  | DMA Write: A-Data Assembly Transfer of Write Data 2                                |              |

| 3.11.6  | DMA Write: Acknowledge                                                             |              |

| 3.11.7  | DMA Write: Sending IOA Request to the MBox                                         |              |

| 3.11.8  | DMA Write: MBox Reads the Register File                                            |              |

| 3.12    | DMA READ                                                                           | 3-48         |

## **CONTENTS (Cont)**

|            |                                                      | Page |

|------------|------------------------------------------------------|------|

| 3.12.1     | DMA Read: Command/Address Reception                  | 3-49 |

| 3.12.2     | DMA Read: Register File TTL Write Address Generation | 3-49 |

| 3.12.3     | DMA Read: A-Data Assembly Command/Address Transfer   | 3-49 |

| 3.12.4     | DMA Read: ID File                                    |      |

| 3.12.5     | DMA Read: Acknowledge                                |      |

| 3.12.6     | DMA Read: IOA Request                                |      |

| 3.12.7     | DMA Read: MBox Reads the Register File               | 3-51 |

| 3.12.8     | DMA Read: DMA DONE/ERROR                             |      |

| 3.12.9     | DMA Read: Register File TTL Read Address             |      |

| 3.12.10    | DMA Read: DMA Read Data Transfer to the SBI          |      |

| 3.12.11    | DMA Read Clear                                       |      |

| 3.12.12    | DMA Read: Second Read Data Longword                  | 3-54 |

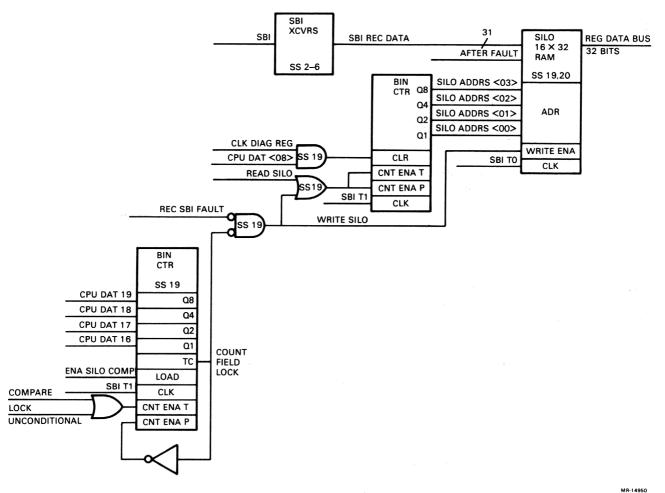

| 3.13       | SBIA SILO                                            |      |

| 3.13.1     | Silo Contents                                        |      |

| 3.13.2     | Locking the Silo                                     |      |

| 3.13.3     | Silo During Normal System Operation                  |      |

| 3.13.4     | Silo During Maintenance                              |      |

| 3.13.4.1   | Silo Unconditional Lock                              | 3-57 |

| 3.13.4.2   | Silo Conditional Lock                                |      |

| 3.14       | SBIA REGISTERS                                       |      |

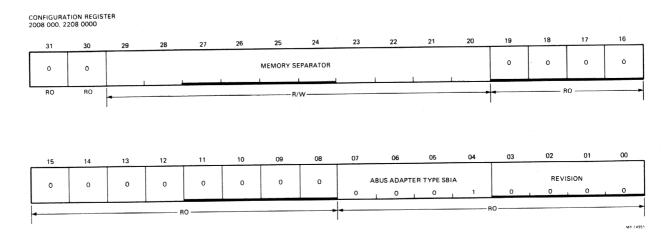

| 3.14.1     | Configuration Register                               |      |

| 3.14.2     | Control and Status Register                          | 3-59 |

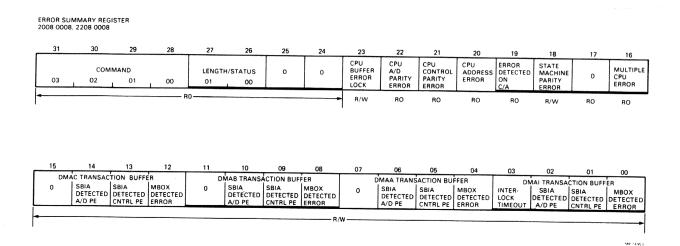

| 3.14.3     | Error Summary Register                               | 3-61 |

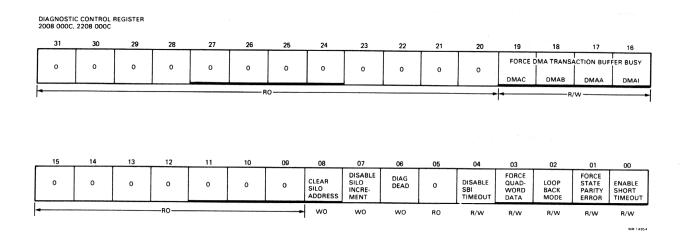

| 3.14.4     | Diagnostic Control Register                          | 3-67 |

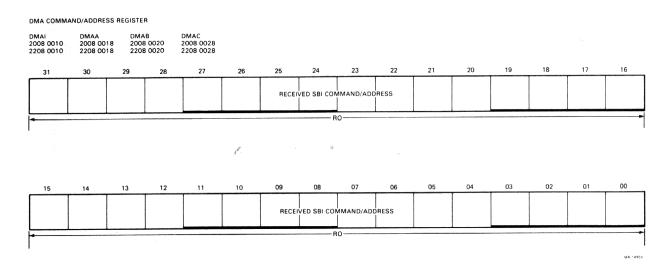

| 3.14.5     | DMA Command/Address Registers                        | 3-70 |

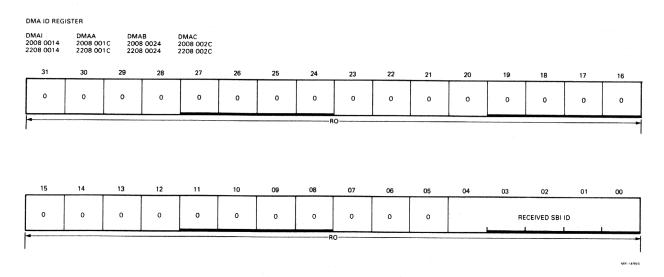

| 3.14.6     | DMA ID Registers                                     |      |

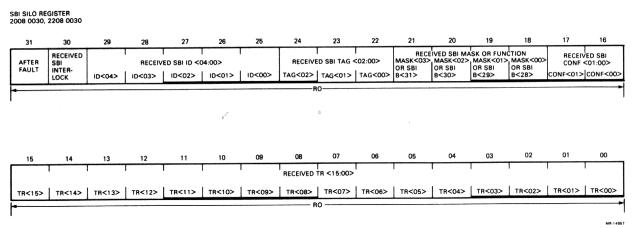

| 3.14.7     | SBI Silo Register                                    | 3-72 |

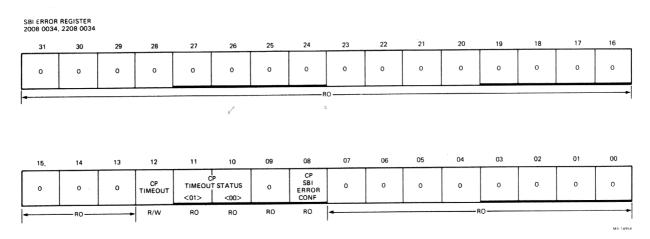

| 3.14.8     | SBI Error Register                                   | 3-74 |

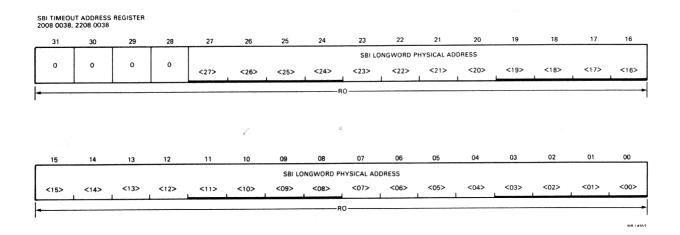

| 3.14.9     | SBI Timeout Address Register                         | 3-76 |

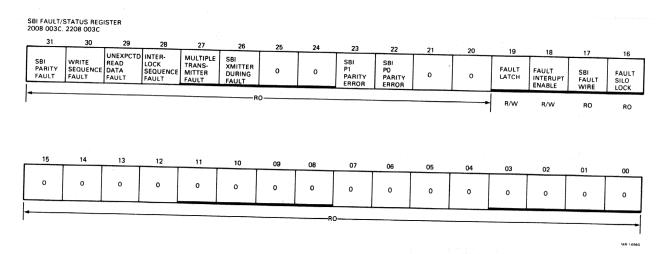

| 3.14.10    | SBI Fault/Status Register                            | 3-77 |

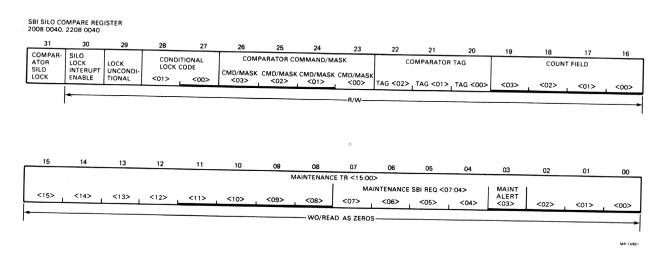

| 3.14.11    | SBI Silo Comparator Register                         | 3-79 |

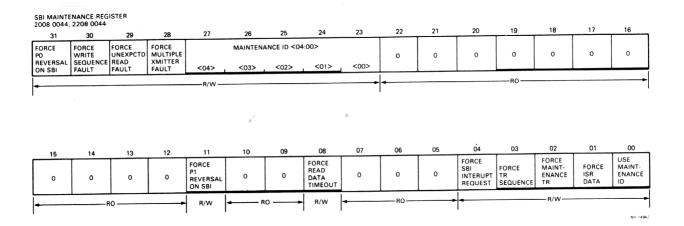

| 3.14.12    | SBI Maintenance Register                             | 3-82 |

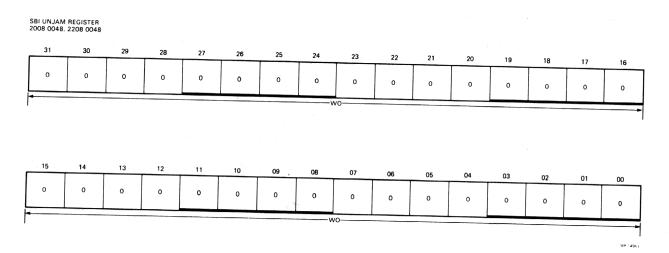

| 3.14.13    | SBI Unjam Register                                   | 3-85 |

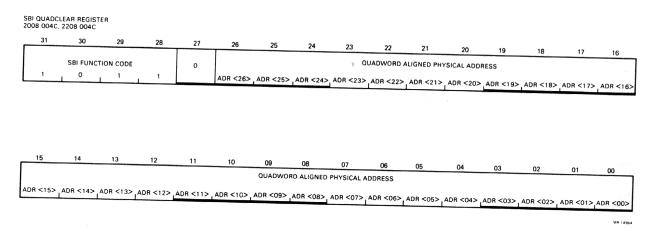

| 3.14.14    | SBI Quadclear Register                               | 3-85 |

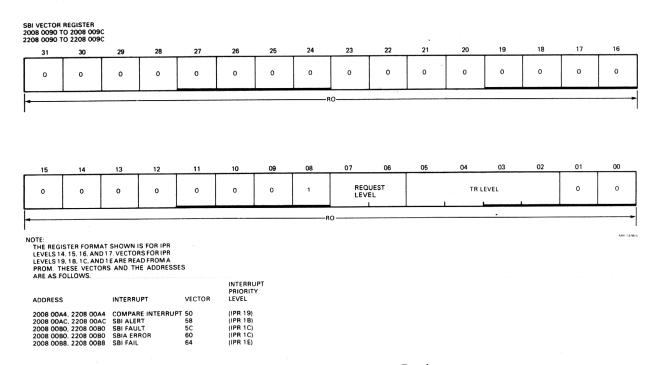

| 3.14.15    | SBI Vector Register                                  | 3-86 |

| APPENDIX A | ABUS PROTOCOL                                        |      |

| APPENDIX B | SBI PROTOCOL                                         |      |

APPENDIX C SBI ARBITRATION

## **FIGURES**

| Figure No. | Title                                                               | Page |

|------------|---------------------------------------------------------------------|------|

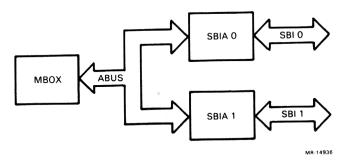

| 1-1        | ABus/SBIA Interconnect                                              | 1-2  |

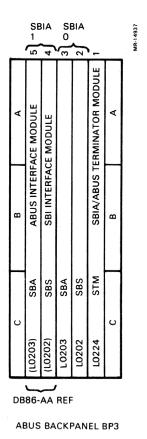

| 1-2        | ABus Backpanel                                                      | 1-2  |

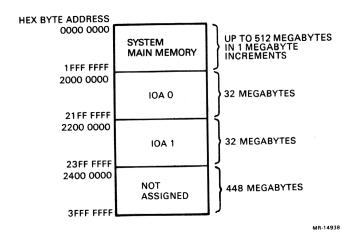

| 1-3        | Physical Memory Address Allocation                                  | 1-4  |

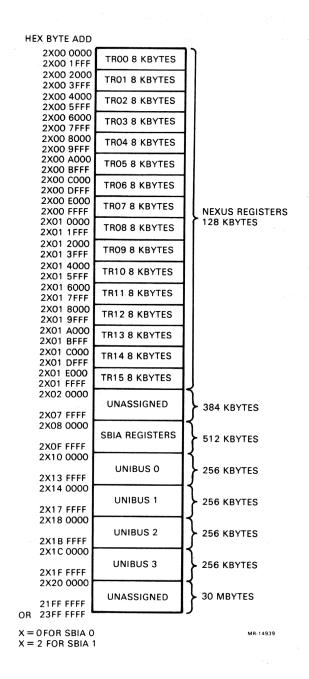

| 1-4        | I/O Adapter Physical Address Allocation                             | 1-5  |

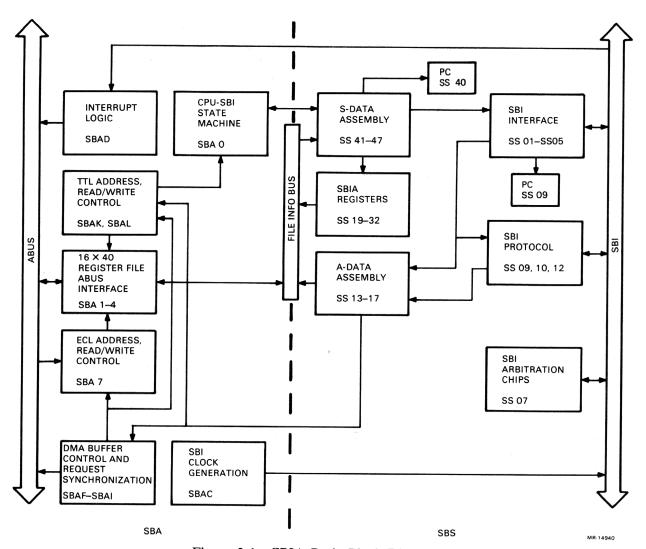

| 2-1        | SBIA Basic Block Diagram                                            |      |

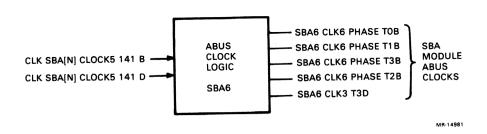

| 2-2        | ABus Clock Logic                                                    |      |

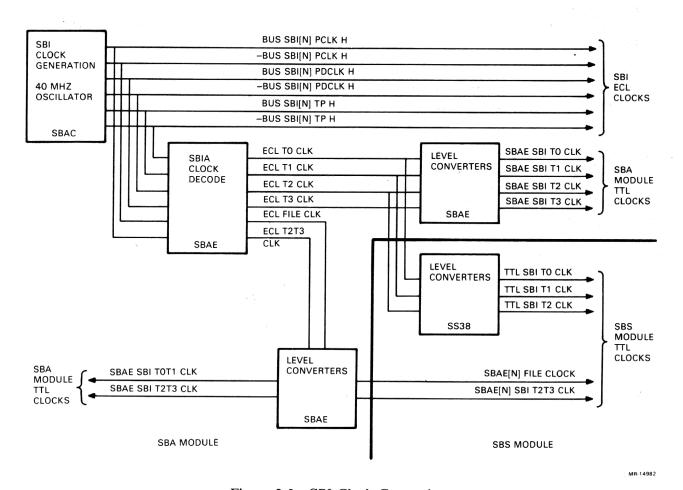

| 2-3        | SBI Clock Generation                                                | 2-5  |

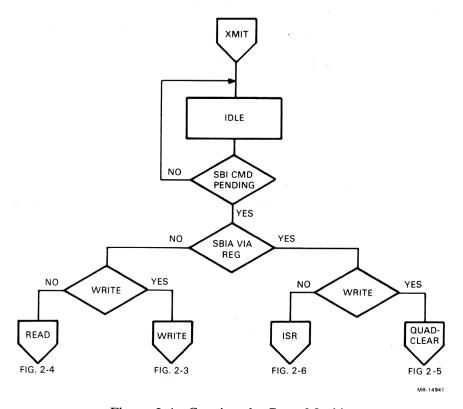

| 2-4        | Starting the State Machine                                          | 2-7  |

| 2-5        | State Machine Flowchart: CPU Write                                  | 2-9  |

| 2-6        | State Machine Flowchart: CPU Read                                   | 2-11 |

| 2-7        | State Machine Flowchart: Quadclear                                  | 2-12 |

| 2-8        | State Machine Flowchart: ISR                                        |      |

| 3-1        | SBIA Register File                                                  |      |

| 3-2        | CPU Write: ABus Protocol                                            | 3-3  |

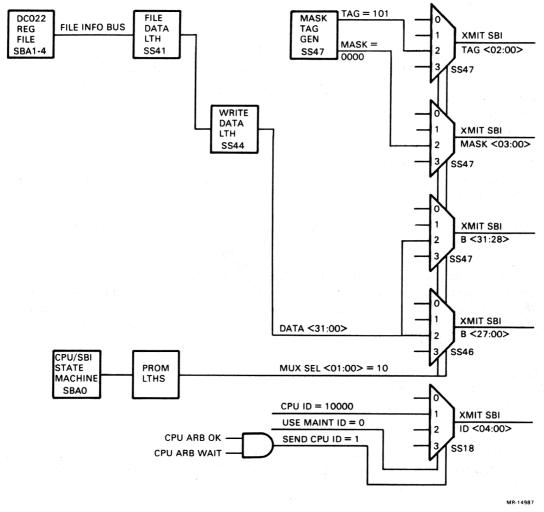

| 3-3        | S-Data Assembly: CPU Write SBI Nexus Register Command/Address Cycle | 3-6  |

| 3-4        | Command/Address and Write Data Transfer to SBI for CPU Write Nexus  |      |

|            | Register                                                            | 3-7  |

| 3-5        | S-Data Assembly: CPU Write SBI Nexus Register Write Data Cycle      | 3-9  |

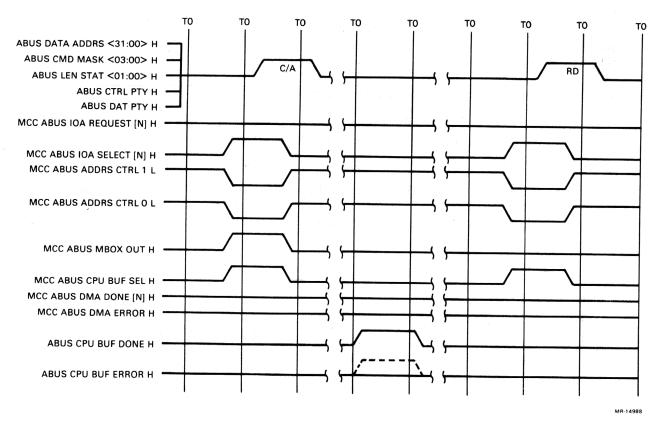

| 3-6        | CPU Read SBI Nexus Register: ABus Protocol                          | 3-11 |

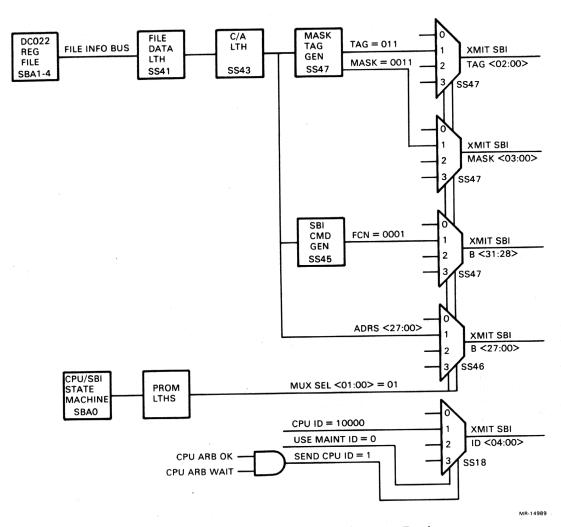

| 3-7        | S-Data Assembly: CPU Read Nexus Register                            | 3-12 |

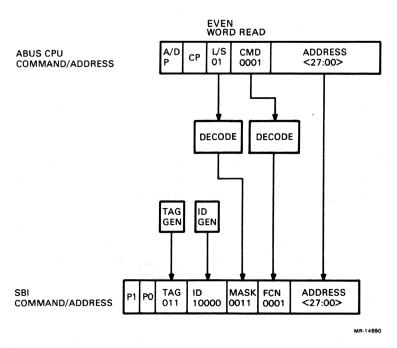

| 3-8        | Command/Address Transfer to SBI for CPU Read SBI Nexus Register     | 3-13 |

| 3-9        | A-Data Assembly: CPU Read Nexus Register, Read Data                 | 3-16 |

| 3-10       | CPU Write SBIA Registers                                            | 3-18 |

| 3-11       | Register Address Decode Logic                                       | 3-19 |

| 3-12       | Register Selection, Zero Fill, and Write Enables                    | 3-21 |

| 3-13       | Read SBIA Registers                                                 | 3-23 |

| 3-14       | Enabling Register Data Bus and Local Read Done                      | 3-25 |

| 3-15       | S-Data Assembly: Interrupt Summary Read                             | 3-28 |

| 3-16       | Vector Generation                                                   | 3-30 |

| 3-17       | Quadclear Data Transfer to SBI                                      | 3-31 |

| 3-18       | S-Data Assembly: Quadclear Command/Address Cycle                    | 3-32 |

| 3-19       | S-Data Assembly: Quadclear Write Data Cycle 1                       | 3-33 |

| 3-20       | S-Data Assembly: Quadclear Write Data Cycle 2                       | 3-34 |

| 3-21       | Unjam Sequencer                                                     | 3-36 |

| 3-22       | DMA Buffer Control                                                  | 3-38 |

| 3-23       | DMA Quadword Write Data Transfer                                    | 3-41 |

| 3-24       | DMA Write, A-Data Assembly Command/Address Transfer                 | 3-43 |

| 3-25       | DMA Write: A-Data Assembly Transfer of Write Data 1                 | 3-45 |

| 3-26       | DMA Write: A-Data Assembly Transfer of Write Data 2                 |      |

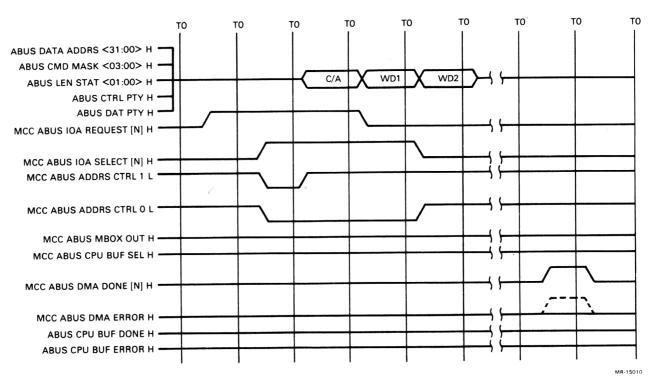

| 3-27       | DMA Quadword Write, ABus Protocol                                   |      |

| 3-28       | DMA Quadword Read: Command/Address Transfer                         | 3-49 |

| 3-29       | DMA Quadword Read: C/A Transfer to DC022                            | 3-50 |

| 3-30       | DMA Quadword Read ABus Protocol (with cache hit)                    | 3-52 |

| 3-31       | DMA Quadword Read: S-Data Assembly Transfer of Read Data            | 3-53 |

| 3-32       | SBIA Silo                                                           | 3-55 |

| 3-33       | Configuration Register                                              | 3-58 |

| 3-34       | Control and Status Register                                         | 3-59 |

| 3-35       | Error Summary Register                                              | 3-61 |

| 3-36       | SBI Diagnostic Control Register                                     | 3-67 |

## FIGURES (Cont)

| Figure No. | Title                                           | Page |

|------------|-------------------------------------------------|------|

| 3-37       | DMA Command/Address Error Registers             | 3-70 |

| 3-38       | DMA ID Error Registers                          | 3-/1 |

| 3-39       | SBI Silo Register                               | 3-12 |

| 3-40       | SBI Error Register                              | 3-74 |

| 3-41       | SRI Timeout Address Register                    | 3-/6 |

| 3-42       | SRI Fault/Status Register                       | 3-11 |

| 3-43       | SBI Silo Comparator Register                    | 3-79 |

| 3-44       | SBI Maintenance Register                        | 3-82 |

| 3-45       | SBI Uniam Register                              | 3-85 |

| 3-46       | SBI Quadclear Register                          | 3-85 |

| 3-47       | SBI Vector Register                             | 3-86 |

| A-1        | ABus Interface                                  | A-1  |

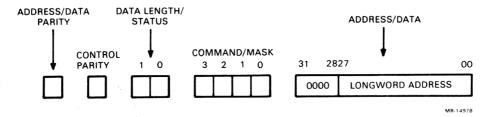

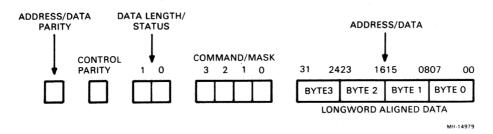

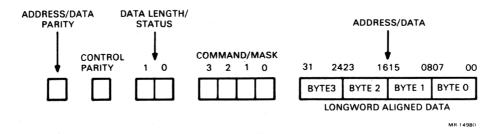

| A-2        | ABus Command/Address Cycle Format               | A-2  |

| A-3        | ABus Write Data Cycle Format                    | A-2  |

| A-4        | ABus Read Data Cycle Format                     | A-2  |

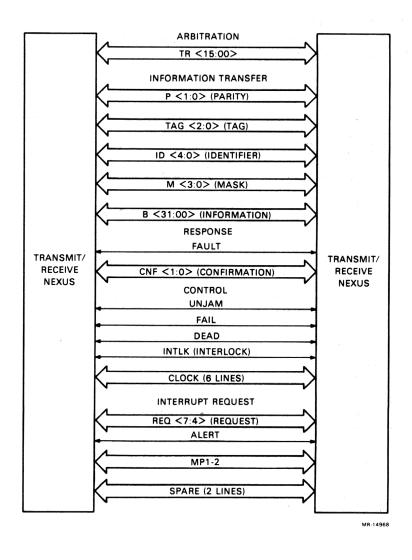

| B-1        | SBI Signal Names                                | B-3  |

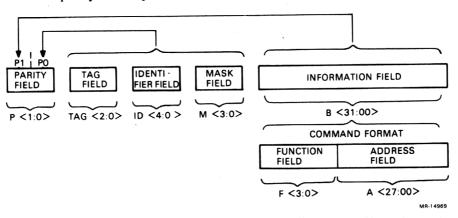

| B-2        | SBI Parity Field Configuration                  | B-4  |

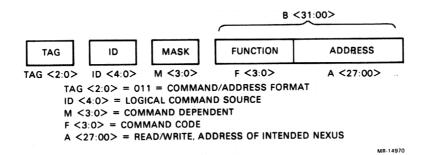

| B-3        | SBI Command/Address Format                      | B-4  |

| B-4        | SBI Command Codes                               | B-4  |

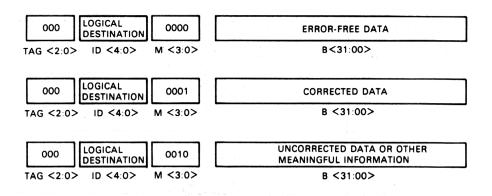

| B-5        | Read Data Format                                | B-5  |

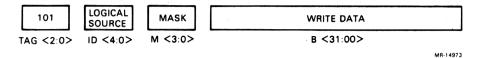

| B-6        | Write Data Format                               | B-5  |

| B-7        | Interrupt Summary Formats                       | B-5  |

| B-8        | SBI Cycles for Extended Read                    | B-6  |

| B-9        | SBI Cycles for Extended Write Masked            | B-6  |

| B-10       | SBI Clock Signals                               | B-7  |

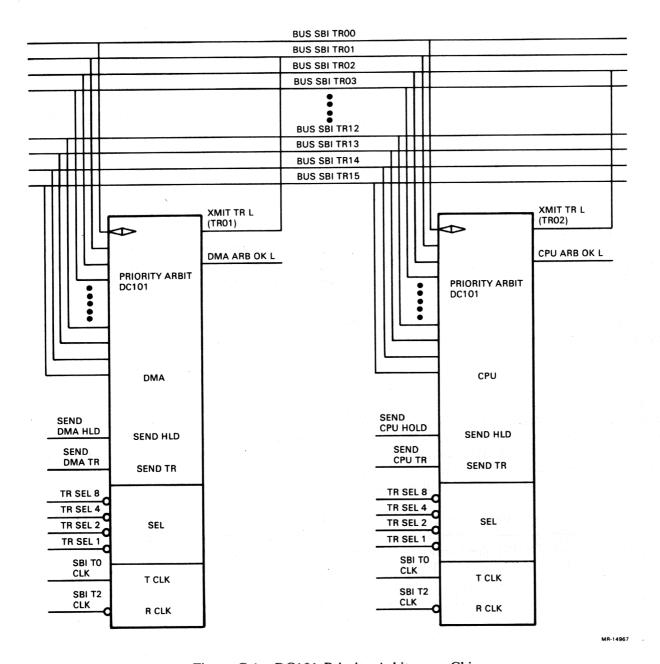

| C-1        | DC101 Priority Arbitration Chips                |      |

|            |                                                 |      |

|            | TABLES                                          |      |

| Table No.  | Title                                           | Page |

| 1-1        | Related Hardware Manuals                        | 1-1  |

| 1-2        | SRIA Register Addresses                         | 1-6  |

| 2-1        | SBIA Operation Performed                        | 2-8  |

| 3-1        | FCL File Address <01:00>                        | 3-3  |

| 3-2        | Register File TTL Read Address                  | 3-4  |

| 3-3        | CPI Command Conversion to SBI Function Codes    | 3-8  |

| 3-4        | SRI Confirmation Bits                           | 3-9  |

| 3-5        | SRI Mask Bits from CPU L/S Bits                 | 3-13 |

| 3-6        | Register Bus Multiplexer Enabling               | 3-22 |

| 3-7        | Register Bus Zero Fill                          | 3-24 |

| 3-8        | Interrupt Priority                              | 3-26 |

| 3-9        | Vector Register Addresser and Interrupt Vectors | 3-27 |

| 3-10       | Setting SBI B<07:04> for ISR                    | 3-29 |

| 3-11       | Uniam Sequencer States                          | 3-36 |

| 3-12       | Register File TTL Write Address <03:02>         | 3-42 |

| 3-13       | Register File TTI Write Address <01:00>         | 3-42 |

| 3-14       | Register File ECL Read Address <03:02>          | 3-48 |

## TABLES (Cont)

| Table No. | Title                                              | Page |

|-----------|----------------------------------------------------|------|

| 3-15      | COND LOCK CODE Control of Silo Comparisons         | 3-57 |

| 3-16      | Configuration Register Bit Definition              | 3-59 |

| 3-17      | Control and Status Register Bit Definitions        | 3-60 |

| 3-18      | Error Summary Register Bit Definitions             | 3-61 |

| 3-19      | SBI Diagnostic Control Register Bit Definition     | 3-67 |

| 3-20      | DMA Command/Address Error Registers Bit Definition | 3-70 |

| 3-21      | DMA ID Error Register Bit Definition               | 3-71 |

| 3-22      | SBI Silo Register Bit Definition                   | 3-72 |

| 3-23      | SBI Error Register Bit Definitions                 | 3-74 |

| 3-24      | SBI Timeout Address Register Bit Definition        | 3-76 |

| 3-25      | SBI Fault/Status Register Bit Definitions          | 3-77 |

| 3-26      | SBI Silo Comparator Register Bit Definition        | 3-80 |

| 3-27      | SBI Maintenance Register Bit Definition            | 3-82 |

| 3-28      | SBI Unjam Register Bit Definitions                 | 3-85 |

| 3-29      | SBI Quadclear Register Bit Definition              | 3-86 |

| 3-30      | SBI Vector Register Bit Definitions                | 3-87 |

| A-1       | ABus Commands                                      | A-3  |

| A-2       | Length/Status for CPU Read/Write                   | A-3  |

| A-3       | Length/Status for DMA Command/Address Cycle        |      |

| A-4       | Length/Status for Data Cycles                      |      |

| A-5       | MCC ABUS ADDRS CTRL                                | A-6  |

| A-6       | Register File ECL Address Control                  | A-7  |

| B-1       | SBI Signal Names and Description                   | B-1  |

| C-1       | XMIT TR Jumpers                                    | C-3  |

|           | •                                                  |      |

# **CHAPTER 1 INTRODUCTION**

#### NOTE

For simplicity, the word "system" is used throughout this manual and applies to both the VAX 8600 and VAX 8650 systems unless otherwise specified.

#### 1.1 MANUAL SCOPE AND RELATED DOCUMENTS

This manual, written as a training and field resource, is a comprehensive description of the VAX 8600/8650 SBIA. The manual is written on three levels – general, functional, and detailed. Table 1-1 lists related hardware documentation.

#### 1.2 GENERAL DESCRIPTION

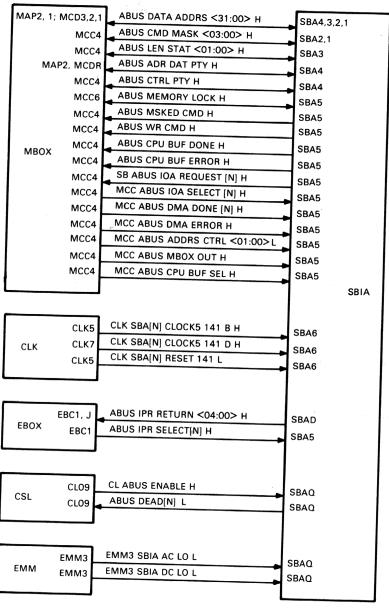

A VAX 8600/8650 may contain two synchronous backplane interconnect adapters (SBIAs), SBIA 0 and SBIA 1. Each SBIA provides an interface between the MBox, via the ABus, and a synchronous backplane interconnect (SBI) that will do the following conversions.

Table 1-1 Related Hardware Manuals

| Title                                                   | DIGITAL P.N. |

|---------------------------------------------------------|--------------|

| Technical Descriptions                                  |              |

| VAX 8600/8650 Console Technical Description             | EK-KA86C-TD  |

| VAX 8600/8650 EBox Technical Description                | EK-KA86E-TD  |

| VAX 8600/8650 System Power Technical Description        | EK-KA86P-TD  |

| VAX 8600/8650 FBox Technical Description                | EK-FP86X-TD  |

| VAX 8600/8650 IBox Technical Description                | EK-KA86I-TD  |

| VAX 8600/8650 MBox/Memory Technical Description         | EK-KA86M-TD  |

| VAX 8600/8650 System Clocks Technical Description       | EK-KA86K-TD  |

| VAX 8600/8650 EMM Technical Description                 | EK-KA86V-TD  |

| VAX 8600/8650 System Description and Processor Overview | EK-KA86S-TD  |

| User's Guides                                           |              |

| VAX 8600/8650 System Diagnostics User's Guide*          | EK-KA86D-UG  |

| VAX 8600/8650 System Hardware User's Guide              | EK-8600H-UG  |

| VAX 8600/8650 System Maintenance Guide*                 | EK-86XV1-MG  |

| VAX 8600/8650 System Installation Manual                | EK-8600I-IN  |

| VAX 8600/8650 System Fault Isolation Manual*            | EK-8600S-MM  |

<sup>\*</sup> For Internal Use Only

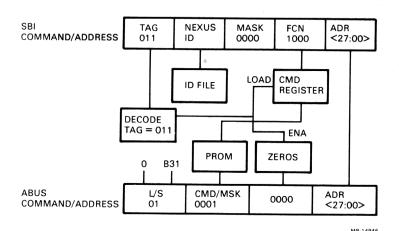

The SBIA enables the CPU, via the MBox, to read or write SBI nexus registers and SBIA registers (see Figure 1-1). In response to the CPU's reading a vector register, the SBIA initiates an interrupt summary read to determine interrupt vectors. In a like manner, in response to the CPU's writing the unjam register, the SBIA hardware carries out the SBI unjam sequence.

Figure 1-1 ABus/SBIA Interconnect

When an SBI nexus initiates a DMA write, after being set up by the CPU, the SBIA transfers the command/address and writes data to the MBox. For a DMA read, the SBIA transfers the command/address to the MBox, accepts the read data from the MBox, and then transfers the read data to the SBI.

#### 1.3 PHYSICAL DESCRIPTION

The SBIAs are located on the five-slot ABus backpanel (Figure 1-2). There are two slots for each SBIA and one slot for an SBI/ABus terminator module. The ABus backpanel is specific for SBIAs; no other ABus interfaces can be used on this backpanel. A VAX 8600/8650 includes one SBIA. The DIGITAL part number for the second SBIA is DB86-AA.

#### 1.3.1 Module Partitioning

The ABus interface module, SBA, an L0203, is installed in slot 3 for SBIA 0 and slot 5 for SBIA 1. The SBI interface module, SBS, an L0202, is installed in slot 2 for SBIA 0 and slot 4 for SBIA 1. The SBI/ABus terminator module, the STM module, an L0224, is installed in slot 1. The terminator provides termination for the ABus and one end of both SBIs. The SBI clock signals are not terminated by the STM, but on the far end of the SBI. The far end SBI terminator is an SBT for SBI 1 and an M9040 for SBI 0, unless SBI 0 is connected to an expansion cabinet. In that case, SBI 0 will also be terminated with an SBT.

### 1.3.1.1 SBA Module - The SBA module has the following characteristics.

- Contains both ECL and TTL logic 1.

- Has a CPU/SBI state machine, a 1K × 12-bit PROM 2.

- Has ECL to TTL and TTL to ECL logic translators 3.

- Contains a 16 × 40-bit register file, the primary interface between the SBIA and the ABus.

#### SBS Module - The SBS module has the following characteristics. 1.3.1.2

- With the exception of the clock translators, completely TTL logic 1.

- Contains the DC101 SBI priority arbitration chips 2.

- Has the following ROMs/PROMs:

- A 256 × 4-bit ROM for ABus commands a.

- A 32 × 8-bit PROM for SBIA error vectors

- A  $256 \times 8$ -bit PROM for zero fill c.

- Three 256 × 8-bit PROMs for register read/write control d.

- A 1K × 4-bit PROM used for address decoding.

Figure 1-2 ABus Backpanel

#### 1.4 SBIA DATA TRANSFERS

The SBIA is involved in all data transfers between the CPU and SBI nexus. A brief description of each type of transfer follows.

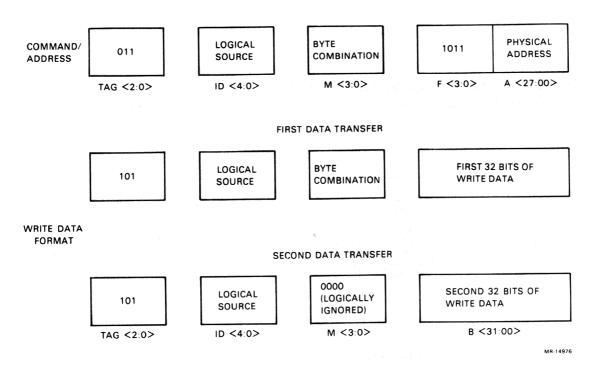

#### 1.4.1 CPU Write

The CPU initiates a CPU write by sending a command/address, and write data longword over the ABus to the SBIA. They conform to ABus protocol. For an overview of ABus protocol and a list of ABus signals, see Appendix A. The command/address and write data are loaded into the SBIA register file. The address portion of the command/address is the target location for the write data. The SBIA removes the command/address and then the write data from the register file. If the address specifies an SBIA register, the data is written into the SBIA register.

If the address is for an SBI nexus, the SBIA modifies the command/address so that it conforms to SBI protocol (see Appendix B). When the SBIA can get control of the SBI at the CPU transfer request level (set at TR02, see Appendix C) it will transmit the modified command/address on the SBI. The write data is transmitted on the SBI on the following SBI cycle.

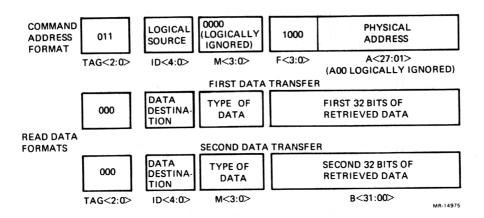

#### 1.4.2 CPU Read

The CPU also initiates a CPU read by sending a command/address over the ABus to the SBIA. It is loaded into the register file as with the CPU write. Again, the address portion of the command/address indicates the target location for the read. The SBIA removes the command/address from the register file, and, if the address is for an SBIA register, gates the contents of the addressed register to the register file.

If the address indicates an SBI nexus, the SBIA modifies the command/address so that it conforms to SBI protocol. As with the CPU write, when the SBIA can get control of the SBI at the CPU transfer request level, it transmits the modified command/address on the SBI.

The addressed nexus recognizes the address and returns the requested read data on the SBI. The SBIA then takes the read data from the SBI, reformats it so that it conforms to ABus protocol, and loads it into the register file. When the read data is in the register file, either from an SBIA register or an SBI nexus, the SBIA informs the MBox that the read data is available.

The MBox takes the read data from the register file and transfers it to the EBox.

#### 1.4.3 DMA Transfers

For DMA transfers, the CPU must provide the nexus with necessary information, such as the starting address of the data transfer and number of bytes to transfer. Interrupts must be enabled if the CPU is to be interrupted at completion of the transfer. The CPU writes nexus registers to prepare for the transfer.

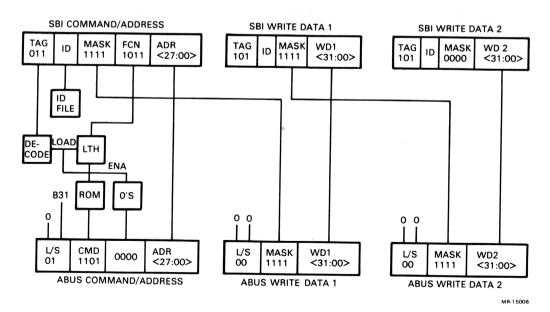

- 1.4.3.1 DMA Write Once the nexus has been programmed for a DMA write, it arbitrates for the SBI and transfers the command/address, followed by the write data longword or longwords for a quadword transfer. The SBIA modifies the command/address so that it conforms to ABus protocol and stores it in the register file. The write data is placed in the register file following the command/address. When the command/address and write data are in the register file, the SBIA asserts an IOA request to the MBox for service. The MBox reads the command/address and then the write data, storing the data in cache.

- 1.4.3.2 DMA Read As for the DMA write, the nexus arbitrates for the SBI and transfers the command/address. The SBIA reformats the command/address, stores it in the register file, and then asserts an IOA request to the MBox. The MBox reads the command/address, obtains the requested data from cache/memory, and places the read data in the SBIA register file. The SBIA removes the read data from the register file and arbitrates for control of the SBI at the transfer request level assigned to the DMA, TR01. When the SBIA gains control of the SBI, it transfers the read data to nexus over the SBI.

#### 1.5 PHYSICAL MEMORY ADDRESSES

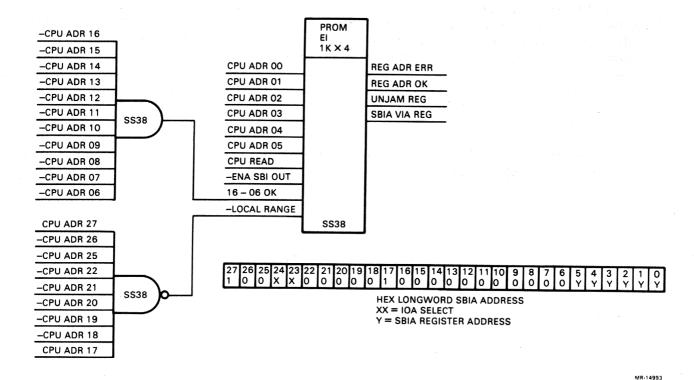

The system physical memory allocation is shown in Figure 1-3. The memory allocation for each IO adapter is shown in Figure 1-4.

Figure 1-3 Physical Memory Address Allocation

Figure 1-4 I/O Adapter Physical Address Allocation

The SBIA register addresses are shown in Table 1-2. Both the hex byte and hex longword addresses are shown. The MBox, before placing the physical address on the ABus, shifts the address right by two bits to provide a longword address. The SBIA decodes the hex longword address. Any address returning to the MBox from the SBIA is shifted left by two bits as it enters the MBox from the ABus. The SBIA registers are described in detail in Chapter 3.

Table 1-2 SBIA Register Addresses\*

| Hex Byte                      | Syte Hex Longword |          |

|-------------------------------|-------------------|----------|

| Register Name                 | Address           | Address  |

| Configuration register        | 2X08 0000         | 8Y2 0000 |

| Control and status register   | 2X08 0004         | 8Y2 0001 |

| Error summary register        | 2X08 0008         | 8Y2 0002 |

| Diagnostic control register   | 2X08 000C         | 8Y2 0003 |

| DMAI command/address register | 2X08 0010         | 8Y2 0004 |

| DMAI ID register              | 2X08 0014         | 8Y2 0005 |

| DMAA command/address register | 2X08 0018         | 8Y2 0006 |

| DMAA ID register              | 2X08 001C         | 8Y2 0007 |

| DMAB command/address register | 2X08 0020         | 8Y2 0008 |

| DMAB ID register              | 2X08 0024         | 8Y2 0009 |

| DMAC command/address register | 2X08 0028         | 8Y2 000A |

| DMAC ID register              | 2X08 002C         | 8Y2 000B |

| SBI silo                      | 2X08 0030         | 8Y2 000C |

| SBI error register            | 2X08 0034         | 8Y2 000D |

| SBI timeout address register  | 2X08 0038         | 8Y2 000E |

| SBI fault/status register     | 2X08 003C         | 8Y2 000F |

| SBI silo comparator           | 2X08 0040         | 8Y2 0010 |

| SBI maintenance register      | 2X08 0044         | 8Y2 0011 |

| SBI unjam register            | 2X08 0048         | 8Y2 0012 |

| SBI quadclear register        | 2X08 004C         | 8Y2 0013 |

| Vector registers              | 2X08 0080         | 8Y2 0020 |

|                               |                   | •        |

| •                             | •                 |          |

| Vector registers              | 2X08 00B8         | 8Y2 002E |

<sup>\*</sup> For SBIA 0: X = 0 and Y = 0For SBIA 1: X = 2 and Y = 8

#### 1.6 SBIA ERROR DETECTION

The SBIA detects the following types of errors.

- 1. SBI parity errors

- 2. Parity errors on ABus data being transferred to the SBI, when it is removed from the register file

- 3. Timeouts

- a. The SBIA is unable to gain control of the SBI in 102.4  $\mu$ s.

- b. An SBI nexus does not respond to a command/address.

- c. If, after the SBI nexus acknowledges the command/address for a CPU read, the SBIA does not receive read data in 102.4  $\mu$ s.

#### 4. SBI protocol errors

- a. The SBIA receives read data when a read is not pending.

- b. A command/address has indicated a write function, but there is no write data on the next SBI cycle.

- c. An SBI nexus attempts an interlock write without a previous interlock read.

- d. More than one SBI nexus transmits on the SBI at the same time.

The errors are described in Chapters 2 and 3. First, the errors are described in the data transfer description, at the time the error might be detected. The errors are also described, in detail, with the register bit descriptions, for the register bit that the particular error would set.

#### 1.7 SBIA REGISTERS

The SBIA has 35 registers in the I/O address space (see Table 2-1). They include control registers, status registers, maintenance registers, error registers, and vector registers. The vector registers occupy addresses 2008 0080 (2208 0080, SBIA 1) to 2008 00B8 (2208 00B8, SBIA 1). The remaining registers are in addresses 2008 0000 (2208 0000, SBIA 1) to 2008 004C (2208 004C, SBIA 1). Each register is described in detail in Chapter 3.

## CHAPTER 2 FUNCTIONAL DESCRIPTION

#### 2.1 CHAPTER OVERVIEW

This chapter covers the SBIA at the block diagram level. Each block is treated individually; the relationship between blocks is described and, if a particular block is used in a data transfer, that aspect is included. Chapter 3 contains detailed descriptions of the data transfers. The SBIA block diagram (Figure 2-1) provides the reference for most of the overview. The numbers in the blocks refer to to print set sheet designation. Flowcharts are used to describe the CPU read/write transactions and the possible error conditions that may arise during those transactions.

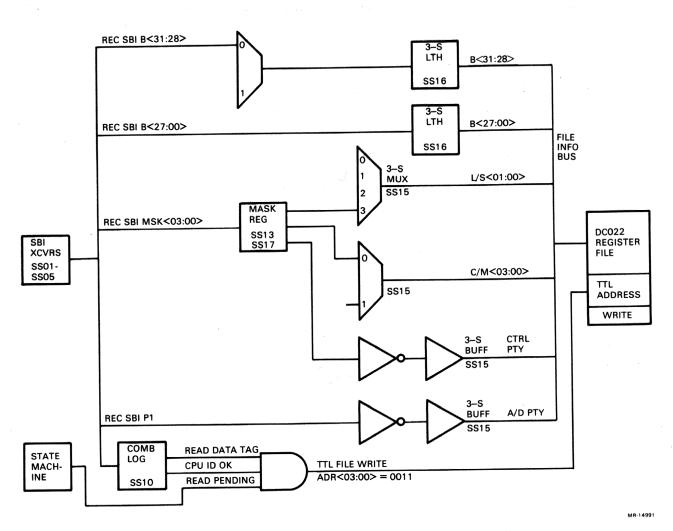

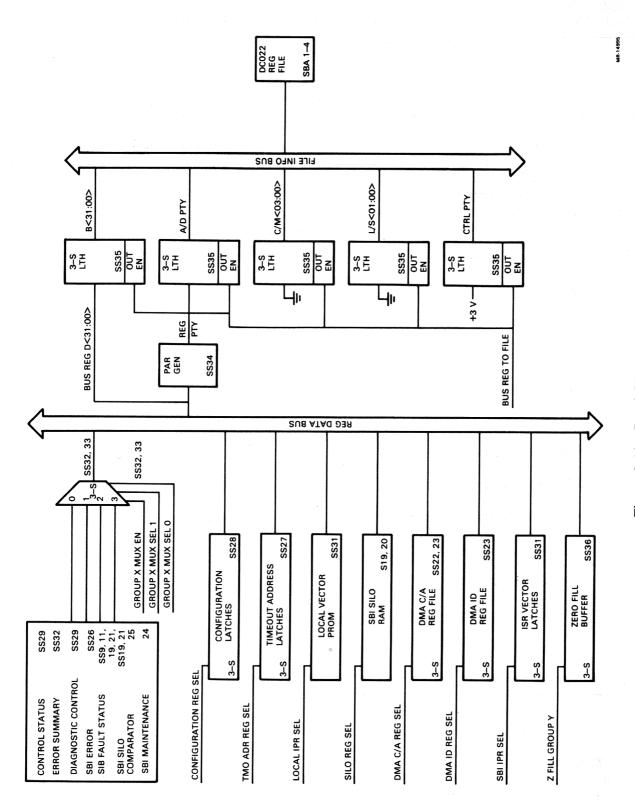

Figure 2-1 SBIA Basic Block Diagram

#### 2.2 SBIA BASIC BLOCK DIAGRAM

Figure 2-1, the SBIA block diagram, is logically divided by the file info bus, which is the backpanel interconnect between the SBA and SBS modules. Everything to the left of the file info bus is on the SBA module. Everything to the right of the file info bus is on the SBS module.

The SBS print set pages are designated as SS00-SS48 and do not include any hex numbers. The SBA module print set is numbered from SBA00-SBAT. The alphabetic numbering starts as if the print set is numbered in hex, but continues through the alphabet after F.

2.2.1 CPU/SBI State Machine

The CPU/SBI state machine is a 1K × 12-bit PROM used to control CPU read/write transactions to SBI nexus registers and vector registers. The state machine is not used for CPU reads/writes to SBIA registers other than the vector registers. Its major function is to control the S-data assembly, during the transfer of register file data, from the ABus to the SBI. During this transfer, it controls the modification of ABus protocol to conform to SBI protocol. It also controls the monitoring of SBI bits to check for error conditions.

The CPU/SBI state machine microword contains an even parity bit, and parity is checked on every microword, even if the state machine is not involved with the transfer. Other outputs include four bits that are used to generate the next address (next state), the bits used to control the S-data assembly, and a bit to allow the SBIA to hold the SBI for an additional cycle for CPU writes to nexus registers.

The state machine does not leave the idle state for a CPU read/write unless the command/address and write data for a CPU write have been removed from the register file without parity errors. When the state machine leaves the idle state, it steps through a series of microinstructions to allow the read/write transaction to take place.

The state machine monitors the SBI confirmation bits by branching on these two bits, and uses these branch conditions to detect error or timeout conditions. The error conditions are covered in the flowcharts.

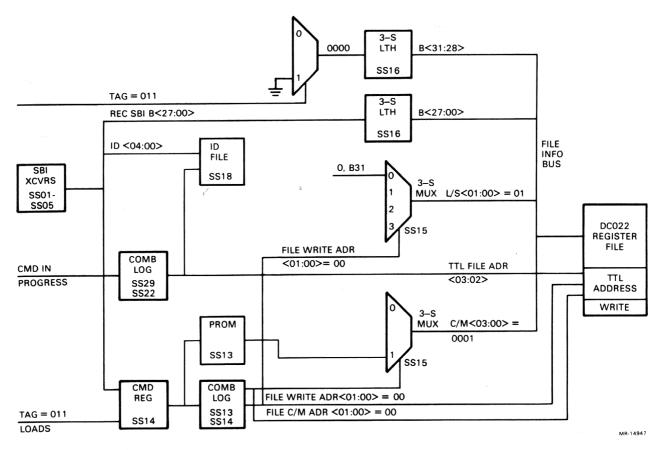

2.2.2 Register File

The most significant part of the ABus interface is the register file, a  $16 \times 40$ -bit dual port register file. This register file is capable of being addressed, written, or read simultaneously on each of its two ports. One port is on the ABus, and the other is on the file info bus, the backpanel bus that connects the SBA module to the SBS module. The register file contains both ECL and TTL logic, with the ABus side being ECL logic and the file info bus side TTL logic.

All information exchange over the ABus must go through the register file, and there are locations reserved for the various transactions. Two locations are reserved for CPU transactions, one location for the command/address word and one location for the read or write data. Two locations are also reserved for interlock read transactions, with one location for the command/address word and one for the read data. There is a block of locations reserved for each of the other DMA transactions - transaction buffers A (DMAA), B (DMAB), and C (DMAC). Each contains three locations, one for the command/address and the other two for the read or write data longwords. (Paragraph 3.1 covers the register file in detail, and Figure 3-1 shows the register file organization.)

If the MBox is writing information into the register file or reading data from the register file, the MBox sets up the register file address. If the SBIA is removing information from the register file for transfer to the SBI, or placing modified SBI information into the register file, the SBIA will control the address. There is a read/write address on the ABus side and a read/write address on the file info bus side.

On the ABus side, the register file can be read or written only if commanded by the MBox. On the TTL side, the register file is read every SBI T0 (see Appendix B, Figure B-10). It is written, when enabled, at SBI T2. Even though it is read every SBI cycle, the contents of the addressed location are not necessarily valid information. The SBIA does not process information read on the TTL side unless it is valid information that the MBox has loaded.

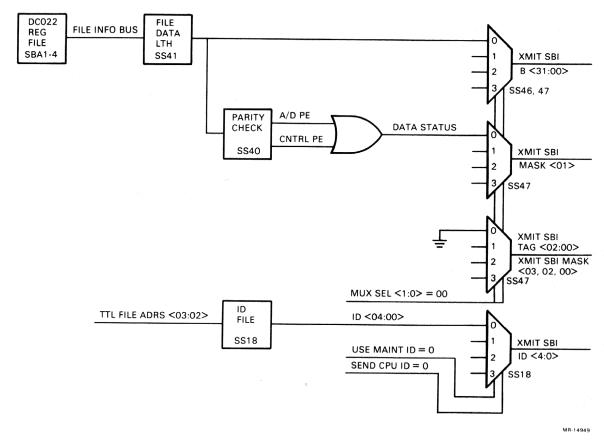

#### 2.2.3 S-Data Assembly

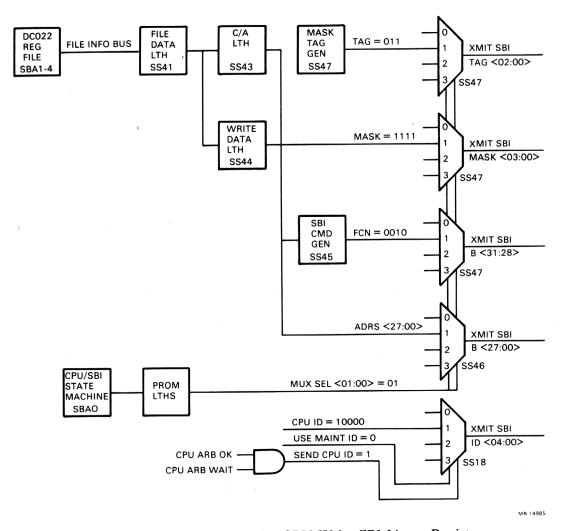

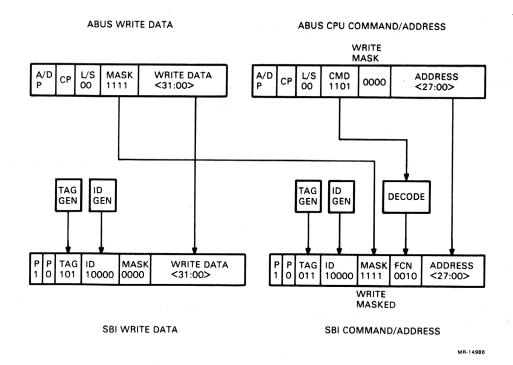

When the register file is read, the data is transferred over the file info bus to the S-data assembly. If the data is to be transmitted on the SBI, the S-data assembly checks for proper parity, reformats each piece of information to insure that it will conform to SBI protocol, and passes the reformatted information to the SBI transceivers.

The S-data assembly contains parity checkers to insure that ABus data has reached the S-data assembly without errors. It also contains parity generation circuitry that will change the ABus odd parity to SBI even parity.

Every SBI T0T1, the contents of the register file, as addressed by the TTL address, will be read and transferred to the S-data assembly. If the MBox has not loaded pertinent information into the register file, the information just read will not get transferred to the SBI. However, a parity check is made in any case. At this point, the data is in ABus format, so the parity is checked accordingly. (See Appendix A for a review of ABus protocol.)

The S-data assembly uses multiplexers to reformat the data so that it will conform to SBI protocol. The multiplexers, and thus the format, are controlled by the state machine.

The S-data assembly also recalculates parity to provide even parity as required on the SBI.

#### 2.2.4 SBI Interface

The SBI interface consists of 8646 4-bit transceiver latches. They are clocked to transmit every SBI T0, if enabled. The receive latches are opened every SBI T2 and closed at -SBI T2. Each chip generates odd parity over the four bits it receives. These parity outputs are used by the SBI protocol logic to check for even SBI parity.

#### 2.2.5 SBI Protocol

The SBI protocol logic combines the parity outputs from each of the SBI transceiver chips to check for SBI parity. Parity is checked over the following bits.

- 1. BUS SBI B<31:00>

- 2. BUS SBI M<03:00>

- 3. BUS SBI P<01:00>

- 4. BUS SBI TAG<02:00>

- 5. BUS SBI ID<04:00>.

Parity is not checked over the following bits.

- 1. BUS SBI TR<15:00>

- 2. BUS SBI CONF<01:00>

- 3. BUS SBI FAULT

- 4. BUS SBI INTLK

- 5. BUS SBI MP<02,01>

- 6. BUS SBI SPARE <01:00>.

The protocol logic monitors for other SBI faults as follows.

- Unexpected read fault: The SBIA receives read data with the CPU ID but is not expecting read 1. data.

- Write sequence fault: The command/address indicated a write function, and the information 2.. received on the next SBI cycle has good parity but it is not write data.

- Multiple transmitter fault: The SBIA just transmitted on the SBI, but the ID received does not 3. compare to the ID transmitted.

- Interlock sequence fault: The SBIA receives a command/address for an interlock write, but the 4. interlock flip-flop is not set (there was no interlock read).

2.2.6 A-Data Assembly

The A-data assembly is primarily responsible for the reformatting of SBI data to insure that it conforms to ABus protocol. It receives the SBI information from the SBI transceivers, modifies it as necessary, and passes it over the file info bus to the register file for temporary storage. Parity will be recalculated to provide odd parity.

2.2.7 Clock Logic

There are two major parts of the clock logic, the ABus clock logic and the SBI clock generation circuitry.

2.2.7.1 ABus Clock Logic - The SBIA uses two clock signals from the clock module, CLK SBA[N] CLOCK5 141 B and CLK SBA[N] CLOCK5 141 D to generate the following ECL clocks.

- SBA6 CLK6 PHASE T0B 1.

- SBA6 CLK6 PHASE T1B 2.

- SBA6 CLK6 PHASE T3B 3.

- SBA6 CLK6 PHASE T2D 4.

- SBA6 CLK3 T3D. 5.

These five clocks provide timing for portions of the ABus interface logic (see Figure 2-2).

Figure 2-2 ABus Clock Logic

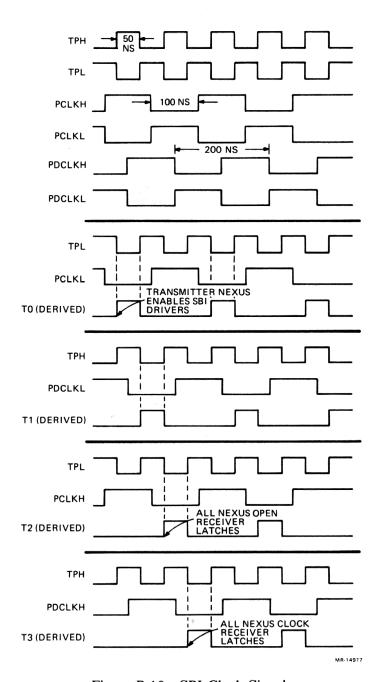

2.2.7.2 SBI Clock Generation – The SBI clock generation circuitry uses a 40 MHz crystal oscillator to provide the six SBI ECL clocks (see Appendix B). The six clocks used by the SBI nexus, including the SBIA, to derive the four 50 ns time states, T0, T1, T2, and T3 are:

- 1. BUS SBI TP H

- 2. BUS SBI TP L

- 3. BUS SBI PCLK H

- 4. BUS SBI PCLK L

- BUS SBI PDCLK H

- 6. BUS SBI PDCLK L.

The SBIA decodes these six SBI clocks to provide various ECL timing terms that are converted to TTL for use on the SBA module. Three of the ECL timing terms are converted to TTL on the SBS module for use on that module (see Figure 2-3).

The external clock input is for manufacturing use only. An input for an external clock, backpanel pin A06, must be enabled by grounding pin A01. Both of these pins are in slot 3 (SBIA 0) or slot 5 (SBIA 1).

Figure 2-3 SBI Clock Generation

2.2.8 DMA Buffer Control and Request Synchronization

The register file contains locations dedicated to specific data transfer transactions, with four separate groups of locations reserved for the DMA transactions. DMA transaction buffers DMAA, DMAB, and DMAC are used for DMA transactions other than interlock reads. Transaction buffer DMAI is used only for interlock reads.

When a DMA transfer is initiated by an SBI nexus, the SBIA must insure that the information is loaded into a transaction buffer in the register file and that it will not be disturbed until the transfer is complete. The DMA buffer control and request synchronization logic determines the transaction buffer to be used next, provides this information to the address control logic, and, when there is a DMA queued in the register file, asserts the DMA request to the MBox. A DMA transaction is considered to be queued when the command/address and write data for a DMA write have been loaded into the register file. When the DMA transaction is complete, the transaction buffer is free for another DMA request.

2.2.9 ECL Address and Read/Write Control

The ECL address and read/write control logic generates the read and write address and enables reading or writing the register file from the ABus (see Paragraph 3.2.1).

The method of address generation depends on the type of data transaction. For DMA transfers, part of the address is generated by the SBIA logic and part by the MBox. For CPU reads, the entire address is generated by the MBox.

The register file can be written from the ABus only if the I/O adapter is selected, and then only if the MBox enables writing the register file. Likewise, to read the register file, the I/O adapter must be selected. The contents of the addressed location are gated to the ABus if the MBox does not enable writing the register file.

2.2.10 TTL Address and Read/Write Control

This block of logic is responsible for controlling the register file address on the SBI side of the register file. The address depends on the type of data transfer operation in progress. For DMA transactions, the DMA buffer control and request synchronization logic control the address. For a CPU read/write, the address is controlled by ABus signals.

2.2.11 Interrupt Logic

The interrupt logic receives the SBI and other interrupt requests, and, if interrupts are enabled (control and status register bit 31 set), establishes priority of the interrupts, and sends an encoding of the highest priority interrupt to the EBox on the IPR return lines (ABus IPR RETURN <04:00>).

The interrupt priorities are as follows. (See Table 3-9 for a list of interrupt priority levels and vectors.)

- 1.

- SBI fault or SBIA error 2.

- 3. Alert

- Silo compare 4.

- SBI request <07:04>.

2.2.12 SBIA Registers

The SBIA has 35 registers in the I/O address space - 20 control, status, error, and maintenance registers, and 15 interrupt vector registers. The first group lies in the local address range of 2008 0000 to 2008 004C (SBIA 0) or 2208 0000 to 2208 004C (SBIA 1). The vector registers are addresses 2008 0080 to 2008 00B8 (SBIA 0) and 2208 0080 to 2208 00B8 (SBIA 1). Access to any other location within the local address space causes an error.

Any data to, or from, the SBIA registers must pass through the register file and over the ABus. The register contents pass through tri-state devices to the file info bus to prevent the possibility of register data and SBI traffic colliding on the file info bus. When the registers are read, if there are numerous bits that are not used, special logic (the zero fill logic) provides logic zeros for most unused bits. (The registers and their bit definitions are defined in detail in Paragraph 3.14, SBIA Registers).

#### 2.2.13 SBI Arbitration Chips

Two DC101 priority arbitration chips allow the SBIA access to the SBI. One, used for DMA transactions, transfers the read data to the SBI; the other gives the SBIA control of the SBI for CPU read or write transactions. The DC101s and SBI arbitration is described in detail in Appendix C.

#### 2.3 CPU TRANSACTION FLOWCHARTS

The following flowcharts describe the PROM flow for CPU transactions. Each flowchart is followed by a brief description. A detailed description may be found in Chapter 3, and the PROM code may be found in microfiche.

#### 2.3.1 Starting the State Machine

The first flowchart, Figure 2-4, is used to determine which of the other four flowcharts to follow. When the VAX 8600/8650 is first powered-up, the ABus is not enabled (the console provides a continuous INIT to the SBIA). When the console enables the ABus by setting console register MCSR <01>, CL ABUS ENABLE is asserted to remove the INIT. The CPU/SBI state machine is forced to the idle state by an INIT.

Figure 2-4 Starting the State Machine

Three functions are involved in getting the CPU-SBI state machine from the idle state to a read, write, ISR, or quadclear state: SBI CMD PENDING, SBIA VIA REG, and WRITE.

- 1. SBI CMD Pending: If there is no SBI command pending, the SBI state machine remains in the idle state. If an SBI command is pending, other control signals are monitored to determine what path to follow. An SBI command is pending under the following conditions.

- a. The MBox has loaded the register file with a command/address for a CPU read or write.

- b. When the command/address is removed from the register file and is transferred to the S-data assembly, there are no address or control parity errors.

- c. For a CPU write, there are no data or control parity errors on the write data.

- d. The address has to be a valid SBI address with the SBIA enabled to access the SBI, or the address must be a valid SBIA vector register address.

If there are any error conditions, the state machine will not leave the idle state. ABUS CPU BUF ERROR will be asserted to inform the MBox of the error, and the timeout address register, the SBI error register, and the error summary register <31:26> are latched to hold the error conditions.

- 2. SBI VIA REG: SBI VIA REG, one of the outputs of a PROM addressed by the command/address, is asserted if the CPU is writing the quadclear register or reading the vector registers for IPR <17:14>. The latter initiates an interrupt summary read.

- 3. WRITE: WRITE will be asserted if bit three of the CPU command in the command/address, is set.

Table 2-1 shows which operation is performed and which flowchart to follow, for the various combinations of WRITE and SBIA VIA REG.

Table 2-1 SBIA Operation Performed

|       | SBI        |                        |            |

|-------|------------|------------------------|------------|

| Write | VIA<br>REG | Operation Performed    | Figure No. |

| 0     | 0          | Read                   | 2-6        |

| 0     | 1          | Interrupt summary read | 2-8        |

| 1     | 0          | Write                  | 2-5        |

| 1     | 1          | Quadclear              | 2-7        |

#### 2.3.2 CPU Write

When the state machine leaves the idle state it starts a timeout counter and goes to the ARB WAIT state (Figure 2-5). The SBIA will request control of the SBI by asserting the transfer request. The transfer request level is selected by connecting backpanel pins to backpanel pins at ground potential (see Appendix C). The state machine remains in the ARB WAIT state until ARB OK is received or a timeout occurs.

Figure 2-5 State Machine Flowchart: CPU Write

If ARB OK is not received within 512 SBI cycles (102.4  $\mu$ s), the state machine goes to the error abort state and the command is aborted. ABUS CPU BUF ERROR is asserted to inform the MBox of the error condition, and the SBI error register, the timeout address register, and the error summary register <31:26> are latched to hold the error information. From the abort state, the state machine returns to the idle state. ABUS CPU BUF DONE is asserted simultaneously with ABUS CPU BUF ERROR. ABUS CPU BUF DONE tells the MBox that the SBIA has finished the transaction.

When the SBIA has gained control of the SBI, it transmits the command/address and then the write data on the SBI. The state machine then monitors for an acknowledge from the SBI nexus.

If there is no response, or there is a busy response, the SBIA returns to the ARB WAIT state to arbitrate for control of the SBI again. When the SBIA gains control of the SBI, the SBIA retransmits the command/address followed by the write data.

If there is no response, or the the nexus continues to send a busy response and the timeout counter expires after 512 SBI cycles (102.4  $\mu$ s), the state machine enters the error abort state and reports the error with ABUS CPU BUF ERROR. The state machine then returns to the idle state.

If the SBIA receives an error confirmation, the state machine enters the error abort state, reports the error, and then returns to the idle state.

If the SBIA receives an acknowledge for the command/address, the state machine then looks for an acknowledge for the write data. If the write data response is busy or error or there is no response, the state machine assumes an intermittent error and returns to the ARB WAIT state; it then retransmits the command/address and write data.

When the SBIA receives an acknowledge for the write data, before the expiration of the timer, the state machine goes to the command done state. It asserts ABUS CPU BUF DONE to inform the MBox that the command has been carried out and then returns to the idle state.

#### 2.3.3 CPU Read

When the state machine leaves the idle state, it goes to the ARB WAIT state, asserts the transfer request, and waits for ARB OK (see Figure 2-6). If the SBIA does not gain control of the SBI within 512 SBI cycles, a timeout condition exists, the state machine goes to the abort state, asserts ABUS CPU BUF ERROR to report the error, and returns to the idle state.

When the SBIA gains control of the SBI, it transmits the command/address on the SBI. It waits one cycle and then checks for an acknowledge for the command/address. If there is no response, or the response is a busy response, the state machine returns to the ARB WAIT state, waits for control of the SBI once more, and then retransmits the command/address.

If the SBIA receives an error response for the command/address, or the timeout counter expires before receiving an acknowledgment, the state machine goes to the error abort state and asserts ABUS CPU BUF ERROR to report the error.

If an acknowledge is received, the SBIA restarts the 512 SBI cycle timeout counter. The SBIA waits for the nexus to transmit the read data on the SBI. If the SBIA does not receive the read data within 512 SBI cycles, the state machine goes to the error abort state to report the error.

If the read data is received within the allotted time, the SBIA reformats the data and loads it into the register file. The state machine then goes to the SBI CMD DONE state and asserts ABUS CPU BUF DONE. The MBox assumes that the transaction was carried out successfully when ABUS CPU BUF ERROR is not asserted. The state machine then returns to the idle state.

The MBox transfers the read data from the register file to the EBox to complete the CPU read transaction.

Figure 2-6 State Machine Flowchart: CPU Read

2.3.4 Quadclear

The purpose of the quadclear operation is to clear ECC errors in SBI memories (see Figure 2-7). For the VAX 8600/8650 system, microdiagnostics uses the quadclear operation extensively to perform DMA quadword loopback transfers.

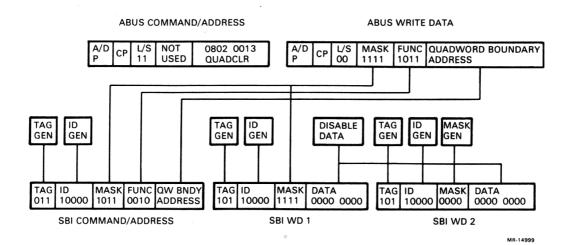

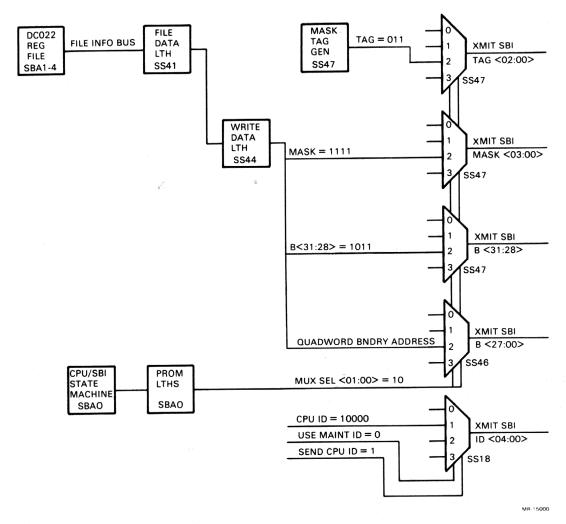

The CPU writes the quadclear register. The command/address specifies a CPU write to the quadclear register. The write data contains the SBI command for an extended write masked (1011) and the address of the quadword to be cleared. The ABus write data is used to form the SBI command/address, and the SBI write data is two all-zero longwords. The flowchart for quadclear is much the same as for CPU write.

Figure 2-7 State Machine Flowchart: Quadclear

The state machine goes to the ARB WAIT state to await the availability of the SBI. As with the CPU read or write, the SBIA must gain control of the SBI within 512 SBI cycles, or a timeout condition will exist. If the SBIA does not gain control of the SBI within 512 SBI cycles, the state machine goes to the error abort state and asserts ABUS CPU BUF ERROR to report the error.

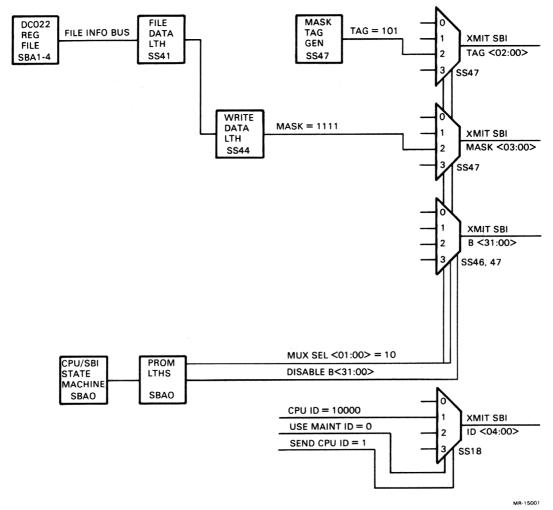

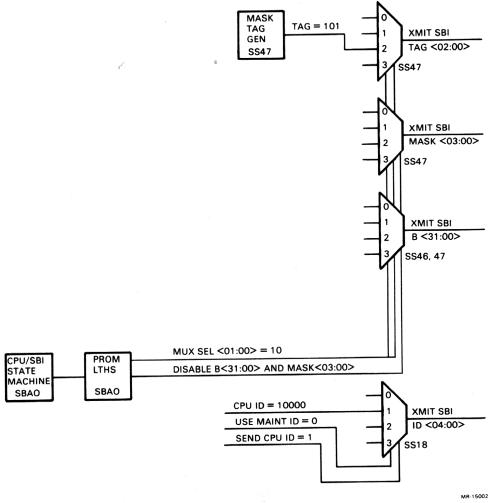

When the SBIA gains control of the SBI, it transmits the command/address developed from the ABus write data, followed by two all-zero write data cycles. On the second write data SBI cycle, the SBIA looks for an acknowledgment for the command/address from the nexus.

If there is no response, or the confirmation is a busy response, the state machine returns to the ARB WAIT state, waits for control of the SBI, and retransmits the command/address and write data. If the SBIA continues to receive busy responses or receives no response for 512 SBI cycles, the state machine goes to the error abort state to report the error. Also, if an error response is received for the command/address, the state machine goes to the error abort state.

When the state machine has seen an acknowledgment for the command/address, it looks for the acknowledgments for the write data cycles. An acknowledgment is expected for each write data cycle. If the SBIA receives an error or busy confirmation, or receives no response for either data cycle, the state machine will go to the ARB WAIT cycle to retransmit the command/address and write data. Again, it is assumed that the command/address was received properly, so there must have been an intermittent error.

When the state machine has detected the proper number of acknowledgments (three), it goes to the SBI CMD DONE state, asserts ABUS CPU BUF DONE, and then returns to the idle state.

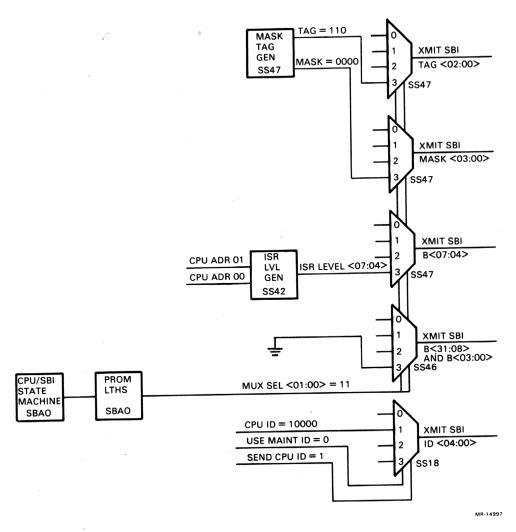

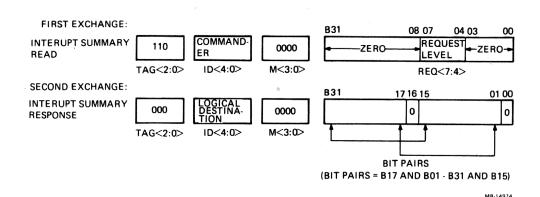

#### 2.3.5 Interrupt Summary Read

When the CPU is going to handle an interrupt, it reads the SBIA vector register corresponding to the IPR level of the active interrupt (see Figure 2-8). The SBIA initiates an interrupt summary read (ISR) in response to the CPU reading the SBIA register for an IPR of 14, 15, 16, or 17. (See Table 3-9 for a comprehensive list of IPR levels, addresses, or vectors.)

The command/address from the CPU indicates a read, and the address specifies the vector register.

During the SBI command/address cycle, the SBIA transmits data with a bit set according to the IPR level being handled – B<04> for IPR 14, B<05> for IPR 15, B<06> for IPR 16, and B<07> for IPR 17.

Any nexus interrupting at that IPR level is expected to transmit an interrupt summary response two cycles after receiving the ISR. The interrupt summary response will have two bits set, the first bit being the same as the nexus TR level, and the other bit equal to the nexus TR level plus 16. The extra bit is not used by the SBIA, but is needed to insure even parity on the SBI. For instance, if the interrupting nexus has a TR of 4, the nexus would set B<20> and B<04>. More than one nexus could be responding to the IPR, and no nexus can be expected to have control of the parity bits. Each nexus will transmit two bits, so parity remains even no matter the number of nexus responses to the ISR.

During an ISR the SBIA does not check the confirmation bits for an acknowledgment, error, or busy. The interrupt summary return is checked only for parity errors.

The state machine enters the ARB WAIT state until the SBIA can gain control of the SBI. If the SBI is not available within 512 SBI cycles, the state machine goes to the error abort state to report the error.

When the SBI is available, the state machine goes to the ISR command/address cycle to transmit the interrupt summary read word. The next state waits just one SBI cycle.

Figure 2-8 State Machine Flowchart: ISR

The state machine expects the interrupt summary return on the next SBI cycle and performs a parity check on the received data. If there is a parity error, the state machine returns to the ARB WAIT state for SBI availability, and retransmits the interrupt summary read word.

If there is no parity error, the SBIA generates the vector from the interrupt summary response and loads the vector into the register file (see Figure 3-16). The state machine goes to the command done state to inform the MBox that the transaction is complete and that the vector is in the register file. The state machine then returns to the idle state.

#### 2.4 SBIA TRANSFERS NOT USING STATE MACHINE

#### 2.4.1 SBIA Register Writes or Reads

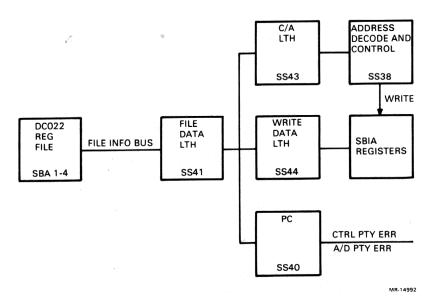

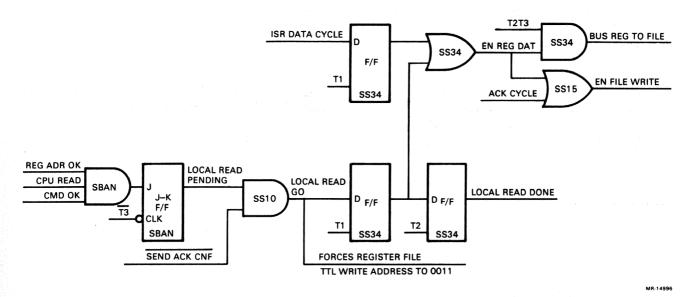

When the CPU writes or reads an SBIA register, the state machine does not leave the idle state and therefore is not involved with the transfer. The MBox loads the register file with a command/address with a command indicating a write or a read, and an address specifying an SBIA register. For a CPU write to an SBIA register, the MBox loads the register file with the write data immediately following the command/address. For a read, the register contents are transferred to the register file. The MBox then reads the register file.

When the command/address and write data for a CPU write are transferred from the register file to the S-data assembly, parity is checked. If there are no parity errors, and the address is a valid SBIA register address, the write data is written into the addressed register. If there are no errors, the MBox is informed that the operation is complete with the assertion of ABUS CPU BUF DONE.

If there is a parity error over the command/address or the write data, or the address is an invalid SBIA register address, the SBIA asserts ABUS CPU BUF ERROR to inform the MBox of the error condition. As with the preceding errors, the SBI error register, the timeout address register, and the error summary register <31:26> are latched to hold the error information.

For a CPU read register, if there are no parity errors and the address is a valid register address, the contents of the addressed register are written into the register file. ABUS CPU BUF DONE informs the MBox that the register data is in the register file. The MBox reads the data from the register file and transfers it to the EBox.

#### 2.4.2 Unjam

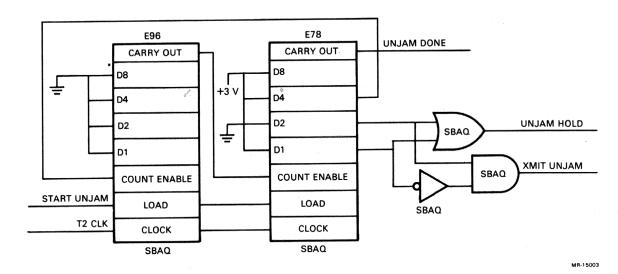

An unjam, issued to the SBI to clear a hung system, is initiated by the CPU writing the SBIA unjam register, address 2008 0048 or 2208 0048. The MBox loads the register file with a command/address indicating a write to the unjam register. Because it is a register write, the MBox also transfers write data to the register file. Although the write data is not used, it is needed to provide good parity on the write data to initiate the unjam sequence.

If there are no parity errors on the command/address and the write data, and the address is a valid SBIA register address, the decoding of the unjam register address initiates the hardware unjam sequencer, which issues SBI HOLD for 16 SBI cycles, SBI HOLD and SBI UNJAM for 16 SBI cycles, and SBI HOLD for another 16 SBI cycles.

If there is a parity error over the command/address or the write data, or the address is an invalid SBIA register address, the SBIA will assert ABUS CPU BUF ERROR to inform the MBox of the error condition. The SBI error register, the timeout address register, and the error summary register <31:26> are latched to hold the error information.

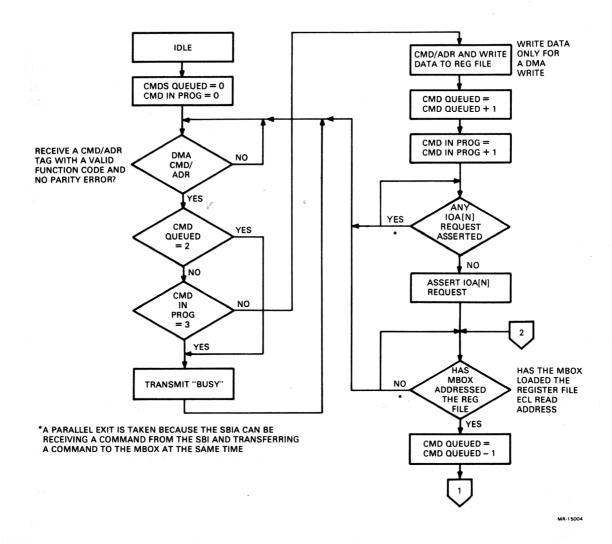

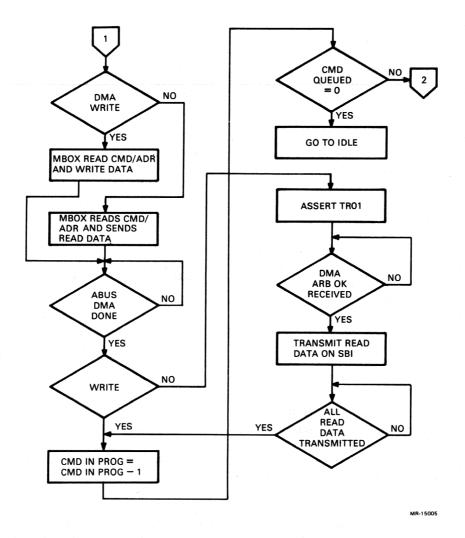

#### 2.4.3 DMA Transactions

The CPU initiates DMA transactions by a series of CPU writes to the appropriate nexus registers. When properly programmed and enabled, the nexus starts the data transfer by placing a command/address on the SBI. With DMA write, the command/address is followed by the write data. With a DMA read, the nexus expects to receive the read data over the SBI later.

DMA transactions may be interlocked or noninterlocked. A DMA interlock read must precede an interlock write. An interlock write occurring without a preceding interlock read is an interlock sequence fault, and SBI FAULT is asserted to interrupt the CPU.

An interlock timeout exists if the interlock write does not occur within 512 SBI cycles (102.4  $\mu$ s) of the interlock read. An interlock timeout asserts a DMAI ERROR, which will interrupt the CPU.

- 2.4.3.1 DMA Write The SBIA, upon receiving the command/address from the SBI nexus, reformats the command/address and writes it into the register file if the following conditions are met.

- 1. There are no SBI parity errors over the command/address.

- 2. The address is for a memory location; it is less than the contents of the configuration register.

- 3. The tag is for a command/address (011).

- 4. The function is a valid SBI function.

- 5. The SBIA is not expecting write data, which means that the previous SBI cycle was not a command/address for a DMA write.

- 6. There is an available transaction buffer in the register file.

The following SBI cycle(s) should contain the write data to be written into memory. The write data will be written into the register file if the following conditions are met.

- 1. The command/address indicated a write function or extended write function.

- 2. The tag indicates write data (101).

- 3. There are no parity errors on the write data.

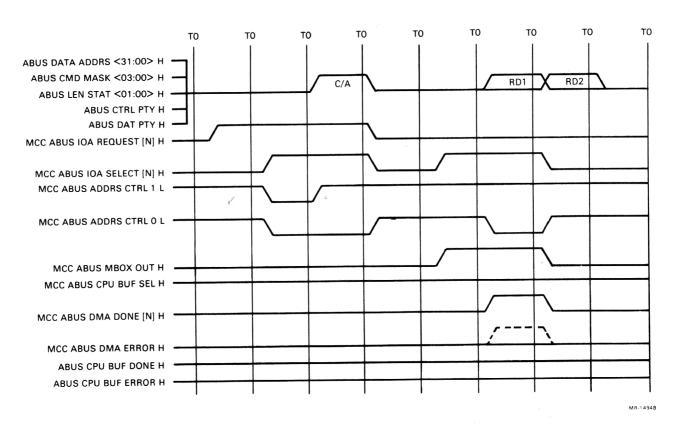

If the SBIA detects an SBI parity error over the command/address or write data, the error condition is latched in the SBI fault/status register. The information is not written into the register file, and the EBox is notified of the error condition by an interrupt request.

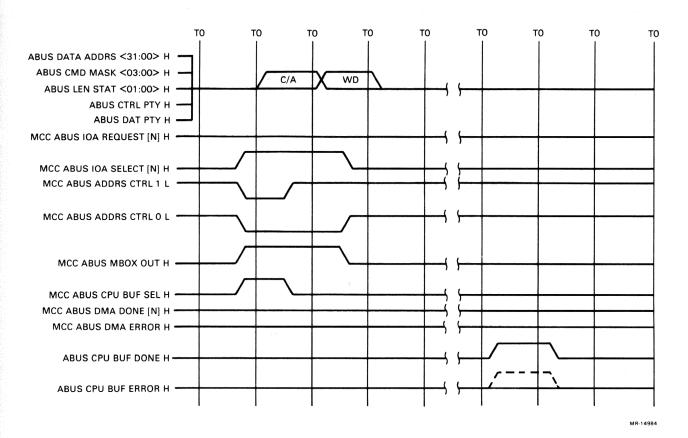

When the command/address and write data have been written into the register file, the SBIA asserts ABUS IOA REQUEST [N] to request MBox attention. When ABUS IOA REQUEST [N] is asserted, ABUS WR CMD will be asserted to inform the MBox that it is a DMA write. ABUS MSKED CMD may also be asserted if it is a masked write. The assertion of the latter two signals allows the MBox microcode to branch early. The microcode does not have to wait until it gets the command/address to know what is expected.

The MBox reads the command/address and write data and stores the write data in cache/memory. If the MBox detects no errors it informs the SBIA that the transaction is complete by asserting MCC ABUS DMA DONE. If the MBox detects an error, it asserts MCC ABUS DMA ERROR at the same time it asserts MCC ABUS DMA DONE. The SBIA latches the error condition in the error summary register and the appropriate DMA command/address and DMA ID register. The SBIA asserts an interrupt request to inform the EBox of the DMA error.

2.4.3.2 DMA Read - The DMA read is initiated by the nexus in the same manner as the DMA write; it transmits the command/address on the SBI. The nexus monitors the SBI for the returning read data.

The SBIA, upon receiving the command/address, reformats it and writes it into the register file if the conditions listed in Paragraph 2.4.3.1 for a DMA write are met. If there is an SBI parity error, the error will be reported the same as for a DMA write.

When the command/address has been written into the register file, the SBIA asserts ABUS IOA REQUEST [N] to request MBox attention. Because ABUS WR CMD is not asserted, the MBox microcode assumes it is a DMA read. ABUS MSKED CMD (not asserted) is used to allow the MBox microcode to branch before it sees the command/address.

The MBox reads the command/address and obtains the read data from cache/memory. It will then write the read data into the SBIA register file. Then the MBox informs the SBIA that the read data is in the register file by the assertion of MCC ABUS DMA DONE. If the MBox detected an error, MCC ABUS DMA ERROR would also have been asserted.

The SBIA removes the read data from the register file and transfers it to the S-data assembly for parity check, reformatting, and transfer to the SBI. When the SBIA can get control of the SBI at TR1, the read data is reformatted to conform to the SBI format and transmitted on the SBI.

If the MBox detected a DMA error, the SBIA latches an error bit in the error summary register and latches the appropriate DMA command/address register and DMA ID register.

If a parity error is detected when the SBIA transfers the read data from the register file to the S-data assembly, the error condition is latched in the error summary register and the appropriate DMA command/address and DMA ID register.

The SBI nexus initiating the DMA read is informed of the error condition because the SBIA forces the mask bits to 0010, read data substitute. No other SBI nexus detects the error because the read data is transmitted on the SBI with even P0 and P1.

# CHAPTER 3 DETAILED DESCRIPTION

#### 3.1 REGISTER FILE ORGANIZATION

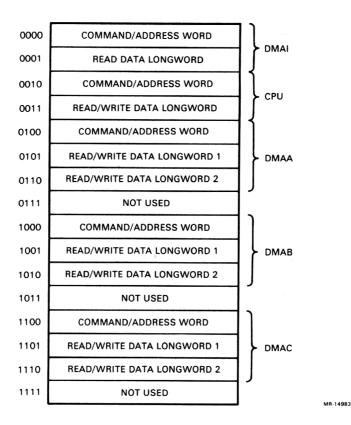

The SBIA register file contains 16 locations, each 40 bits wide. It is divided in five areas called transaction buffers. One transaction buffer, the CPU transaction buffer, is reserved for CPU reads and writes of SBIA or SBI nexus registers. The DMAI transaction buffer is reserved for DMA interlock reads. The remaining three transaction buffers, DMAA, DMAB, and DMAC, are reserved for DMA read and write transfers.

The information contained in the register file conforms to ABus protocol. Therefore, reformatting is necessary before placing the information on the SBI, or before placing SBI information into the register file. (See Appendix A, ABus Protocol, and Appendix B, SBI Protocol.)

#### 3.1.1 CPU Transaction Buffer

The CPU transaction buffer consists of two locations. Location 2 is reserved for the command/address, and location 3 is reserved for the read or write data longword. Refer to Figure 3-1.

Figure 3-1 SBIA Register File

#### 3.1.2 DMAI Transaction Buffer

Register file location 0 is reserved for the command/address for a DMA read interlock. Location 1 is reserved for the read interlock data longword. The interlock is released with a write interlock, through the DMAA, DMAB, or DMAC transaction buffers.

# 3.1.3 DMAA, DMAB, or DMAC Transaction Buffers

Each of the three DMA transaction buffers, DMAA, DMAB, or DMAC, consists of three locations within the register file. DMAA uses locations 4, 5, and 6; DMAB uses locations 8, 9, and A; and DMAC uses locations C, D, and E. The command/address is stored in the first of the three locations, while the other two locations are reserved for the read or write data longwords. The upper two bits of the four-bit address is the same for each of the three locations for a DMA transaction buffer. DMAA = 01XX, DMAB = 10XX, and DMAC = 11XX. When a particular DMA transaction buffer is selected, the upper two bits can be held constant until that buffer is no longer in use. The lower bits can be manipulated to address the required location within the transaction buffer. (This process becomes more apparent as the CPU read, CPU write, and DMA transactions are investigated.)

# 3.2 CPU WRITE SBI NEXUS REGISTER

A CPU read or write cannot be initiated by the MBox if the SBIA has any DMA IOA requests pending (SB ABUS IOA REQUEST [N]).